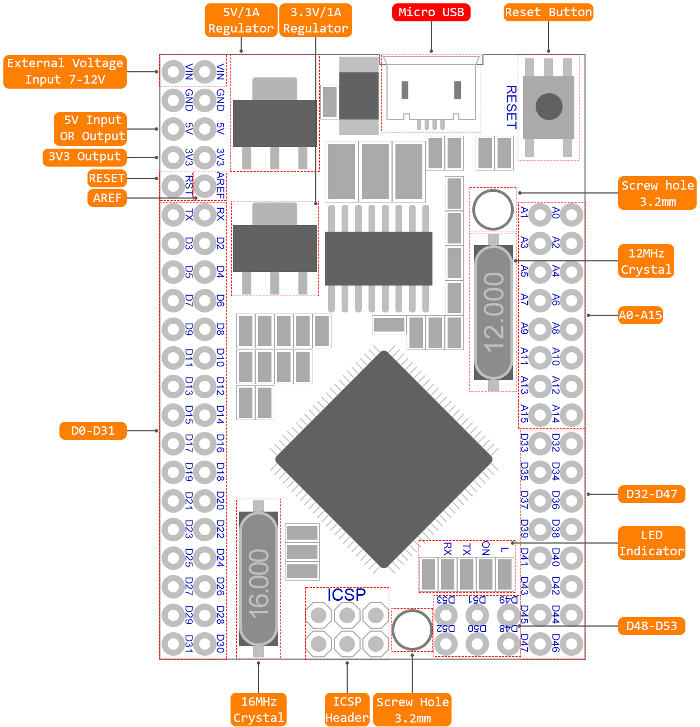

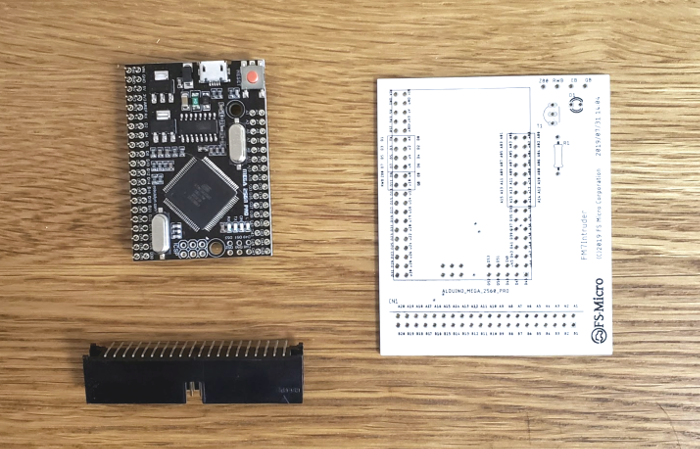

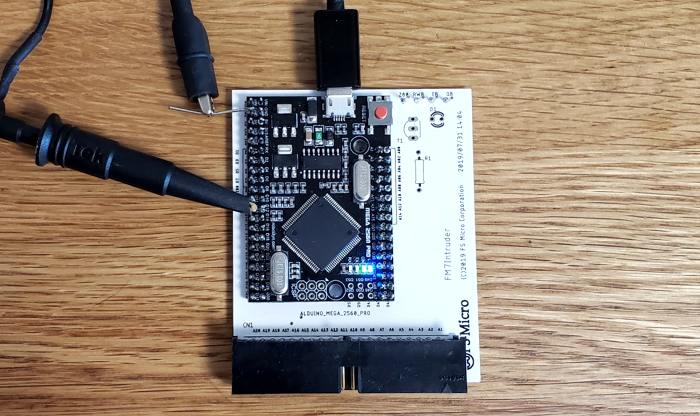

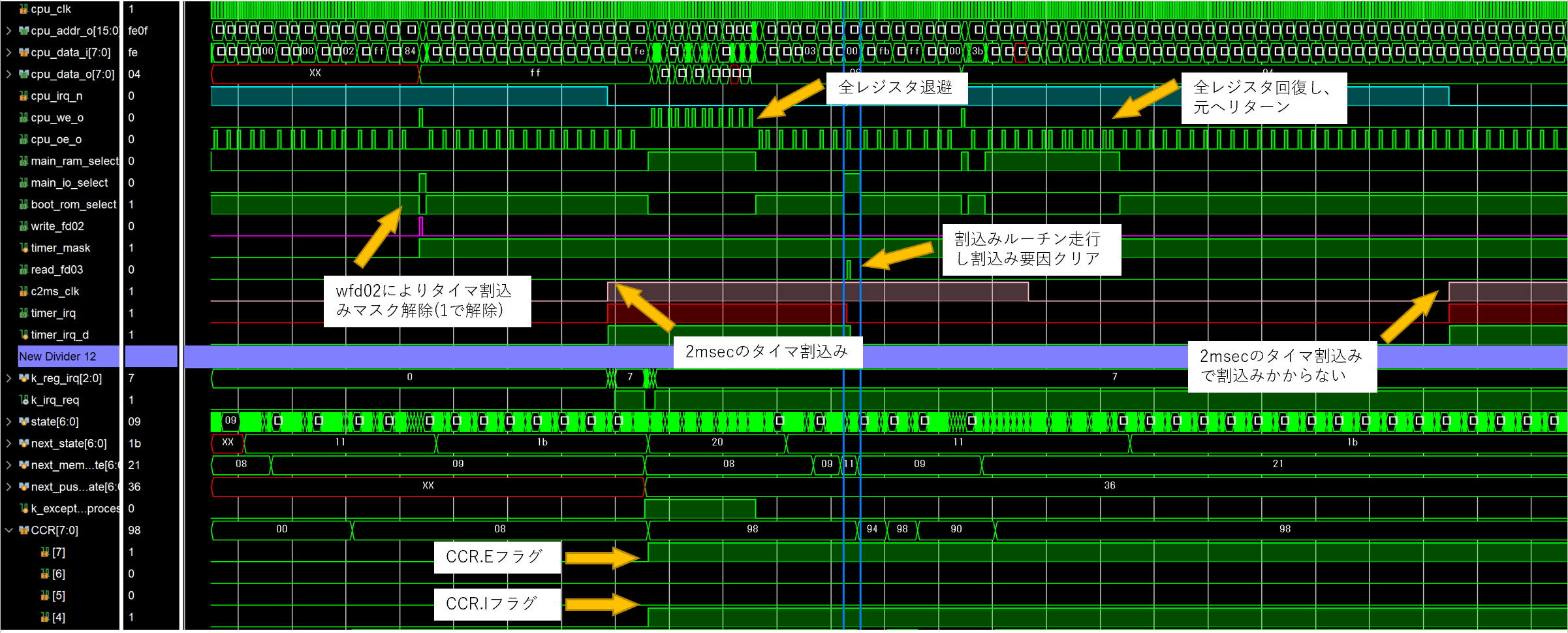

Arduino Mega 2560 Proの端子図を図158.1及び図158.2に示します。

図158.1 Arduino Mega 2560 Proの端子図

図158.1 Arduino Mega 2560 Proの端子図

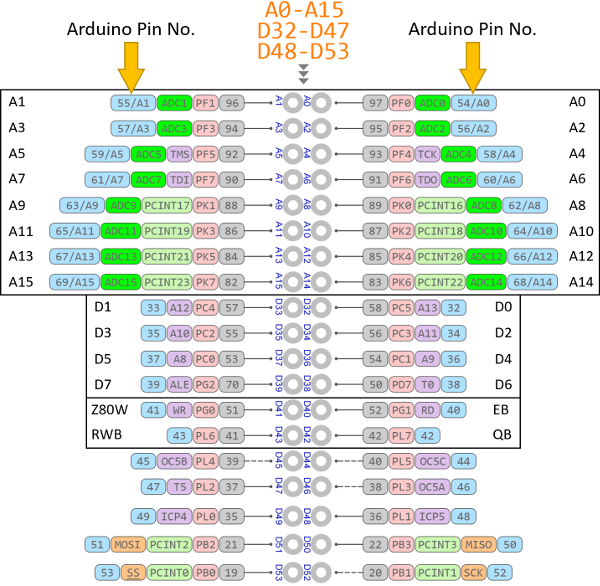

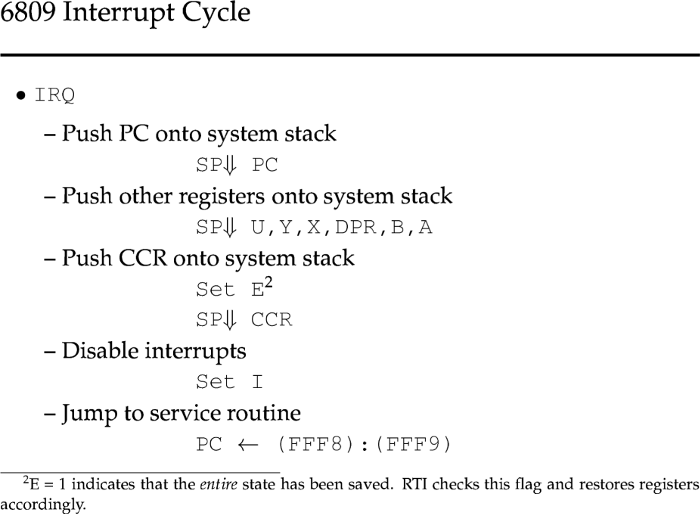

図158.2 Arduino Mega 2560 Proの端子図(右側の端子)

図158.2 Arduino Mega 2560 Proの端子図(右側の端子)

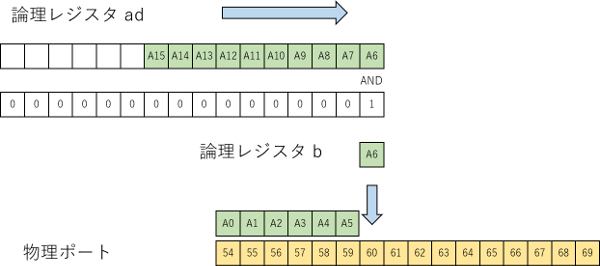

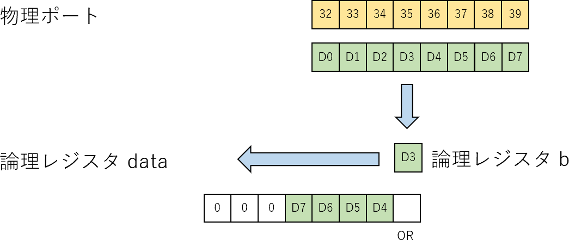

アドレス、データ、制御信号を全てソフトコントロールしています。スケッチはここに置きました。ただし、初版からデータピンの位置を変更しているため、ボードの版数に合わせて適宜修正する必要があります。

これにより吸い出したfbasic30 ROM(\$8000~\$FBFF)生データの一部を示します。

8000 8e 80 13 ce 01 f9 c6 0a bd 85 97 8e 80 26 c6 0a

8010 7e 85 97 06 80 1d 80 5a 09 80 1d 80 77 a0 a0 a0

8020 a0 a0 a0 a0 a0 a0 06 80 30 80 5a 01 80 71 80 77

8030 43 48 41 49 ce 45 52 41 53 c5 4c 4c 49 53 d4 4c

:

:

fbc0 e1 7e 9b 50 7e 8d d1 7e af 1a 7e 96 63 7e b2 34

fbd0 7e b0 ee 7e af 11 7e cc 37 7e af 97 7e ce dc 7e

fbe0 ce df 7e b0 44 7e e3 4d 7e da f9 7e da ef 7e d4

fbf0 df 7e c2 8c 7e c6 7a 7e da f6 f1 7d 86 84 84 8b

このままCOEファイルに変換するか、あるいはバイナリにすれば、前稿のスクリプトが使えますが、簡単なのでこのままawkによりCOE化することにします。

ネットで入手したFM-7エミュレータ用のROMデータと実機から吸い上げた生データを比較したところ、fbasic30.coeは全てのバイトが一致しました。

一方boot.coeは末尾の2 lineが不一致となりました。エミュレータ用のROMでは0xffとなっていますが、実機のROMは割込みベクタが置かれているためにデータが入っています。

エミュレータ用ROMの末尾32バイト:

ffe0 ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff

fff0 ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff

実機ROMの末尾32バイト:

ffe0 ff ff ff ff ff ff 01 04 ff ff ff ff ff ff ff ff

fff0 ff ff 01 d1 01 d4 01 e0 01 dd 01 d7 01 da fe 00

ところが、「FM-7ユーザーズマニュアルシステム仕様」を見ると、\$FFE0~\$FFFFはベクトル領域となっており、boot ROMではないため、これで全てのバイトが一致しました。

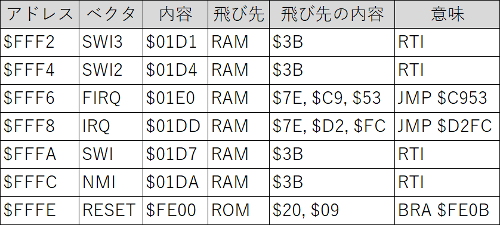

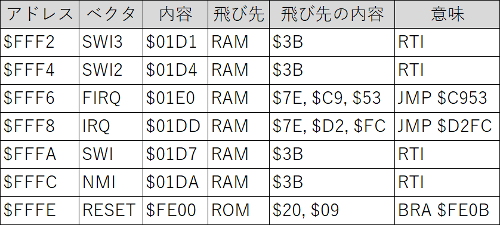

末尾32バイトはベクトル領域というRAM領域でジャンプテーブルとなっています。飛び先のRAMの内容を含めて表にまとめます。

図158.3 割込みベクタまとめ表

図158.3 割込みベクタまとめ表

FIRQ割込みハンドラは\$C953から、IRQ割込みハンドラは\$D2FCからのようです。本カードにより(メインCPUを停止し)\$AAを書き込んだところ、以下のようになったため、\$FFE0~\$FFFDはRAM、\$FFFE~$\$FFFFはROMのようです。

ffe0 aa aa aa aa aa aa aa aa aa aa aa aa aa aa aa aa

fff0 aa aa aa aa aa aa aa aa aa aa aa aa aa aa fe 00

前のブログ

次のブログ

前のブログ

次のブログ