|

25 |

FPGAで機械学習 (3) |

ブート

Ultra96にはMiniDPケーブル経由でディスプレイを接続し、またUSB経由でキーボードとマウスを接続しておきます。前回焼きこんだSDカードをUltra96に差し込み、電源を入れ、リセットスイッチを押すとLinuxがブートします。

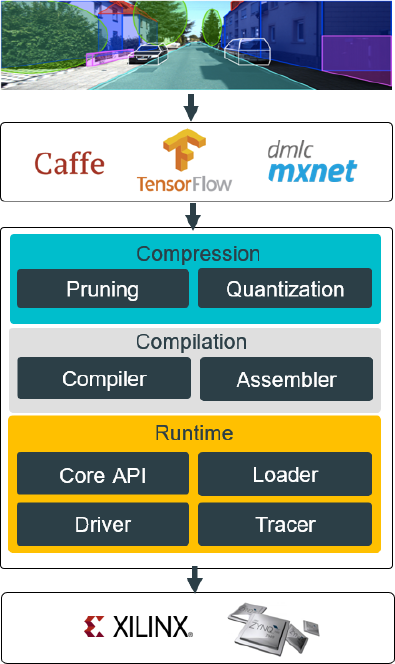

ライブラリインストール

プログラムを展開します。文字が小さくて見づらかったのですが、なんとかターミナルを立ち上げられました。

root@ultra96:~# cd /home/linaro/

root@ultra96:/home/linaro# tar xvzf xlnx_dnndk_2.08_1901.tar.gz

これにより各種プログラムが展開されます。次にUltra96のディレクトリに移り、

root@ultra96:/home/linaro# cd xilinx_dnndk_v2.08/Ultra96

root@ultra96:/home/linaro/xilinx_dnndk_v2.08/Ultra96# bash install.sh Ultra96

により、必要なDNNライブラリをインストールします。ここで評価ボードの再起動が必要となります。

コンパイル&ラン

各種デモプログラムはコンパイルしてランするだけで全て動作しました。

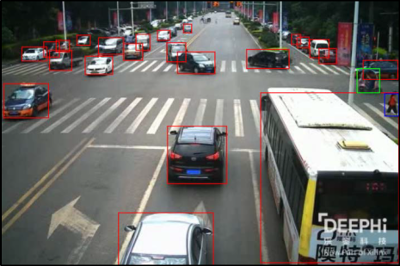

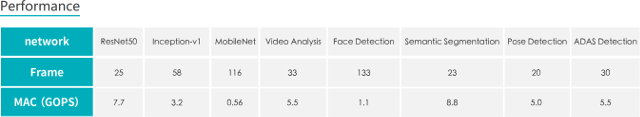

静止画の画像認識はResnet50やMobileNetを用いており、それぞれ25FPS、116FPSとかなり性能差があります。 また動画の画像認識は、face detectionはDenseBox、adas_detectionはYOLO-V3、video analisysはSSDを用いていることがわかりました。以下の性能表によればそれぞれ133FPS、30FPS、33FPSとなっています。ほぼリアルタイムで認識していることがわかります。

認識ソフトウェアは、様々な動画フォーマットに対応しており、調べた限りではMOV, AVI, MP4に対して動作しました。また、解像度も柔軟に対応しています。ただしFPSは解像度により上下するため、比較する際には解像度を合わせないと、正しいネットワーク性能比較になりません。例えばデモ動画では、adas_detectionの動画は512x256の15FPS(640kbps)、video_analisysの動画は480x360の12FPS(954kbps)と微妙に異なっています。

認識率に関しては、YOLO-3はあまり問題を感じませんでしたが、SSDはかなりfalse positiveがあり、(バグかもしれません)このままでは使用できないと感じました。