|

8 |

6809の改造 - HALT端子の追加 (3) |

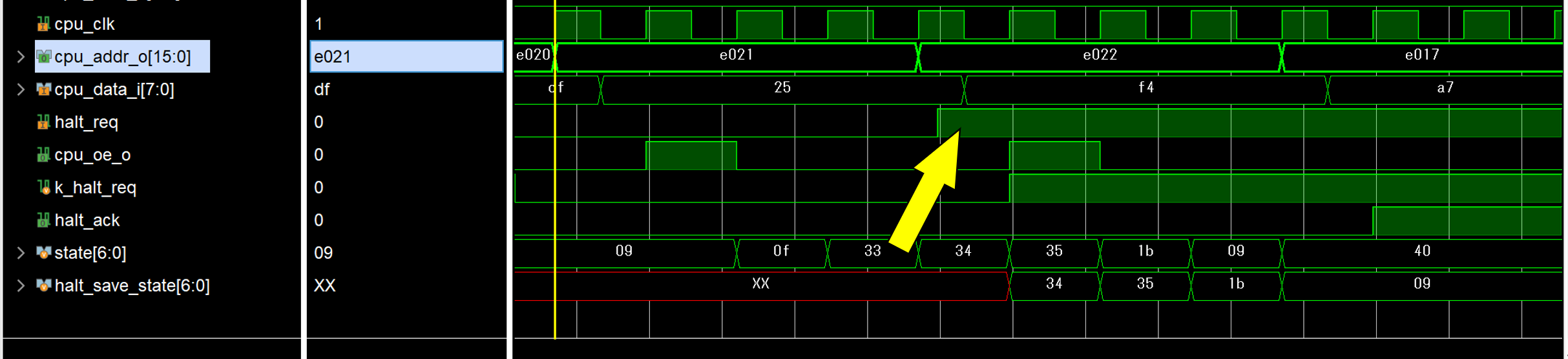

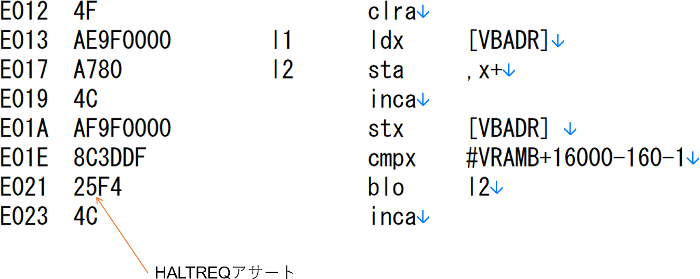

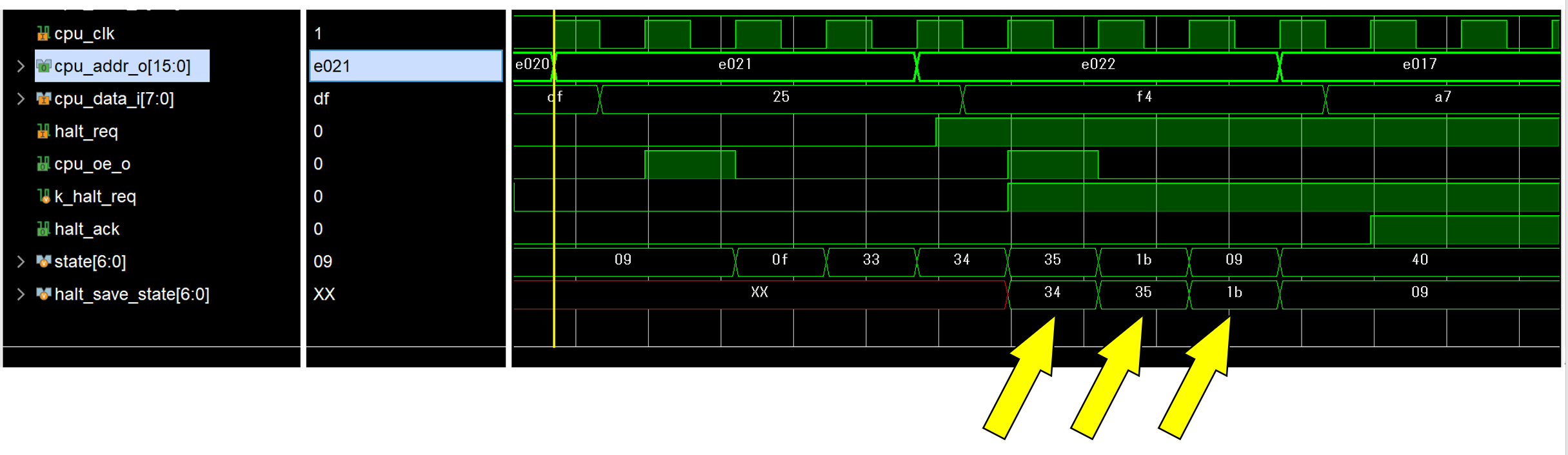

もう少し詳しく見てみます。HALTREQがアサートされたのは、たまたま\$E021のblo命令の第1バイト\$25をフェッチした直後でした。図143.2に示すように、blo命令の\$25と\$F4のフェッチの間に入ったことになります。

HALTREQが"blo l2"命令の間であるため、すぐにはHALTステートに遷移せず、blo命令の第2バイトである\$E022の\$F4のフェッチが行われます。

前稿で新設したhalt_save_stateは、HALTに入る直前のステートを保存するようにしたため、HALTステートに入るまではサイクル毎に書き換えられています。

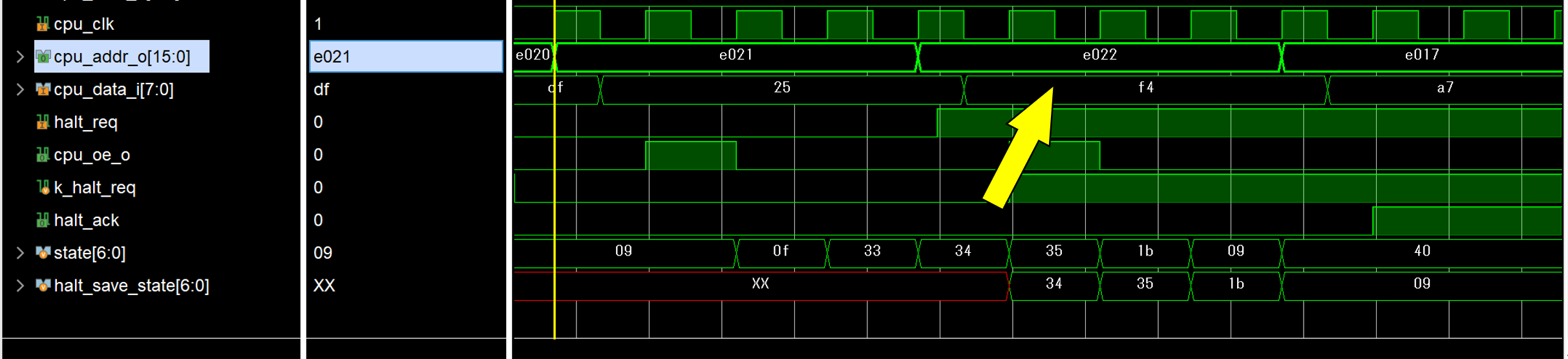

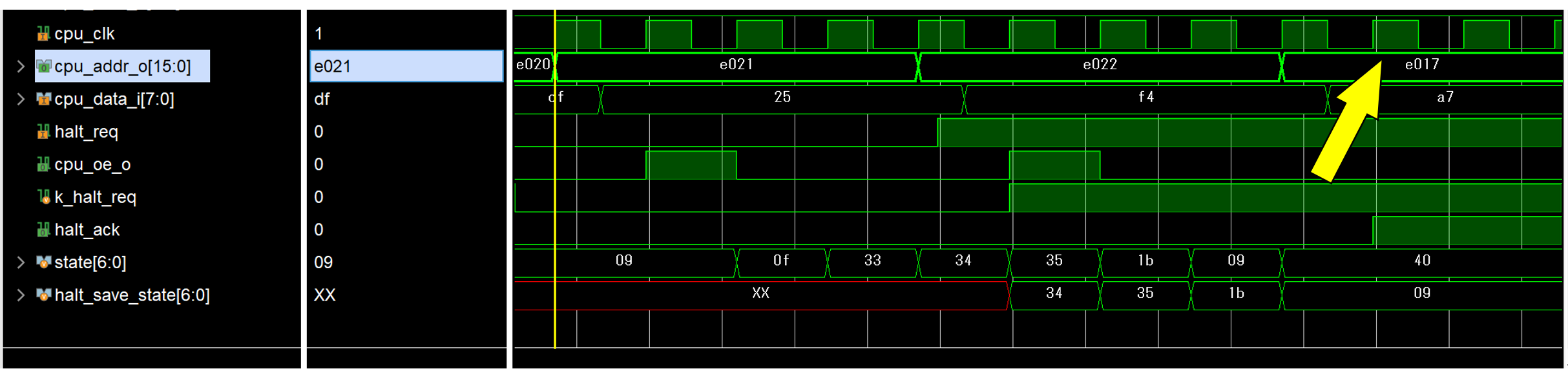

分岐命令をデコードし分岐が実行された後に、アドレスが分岐先である\$E017に変化しています。分岐命令はPCを変更するだけであり、これで分岐命令の実行は完了です。

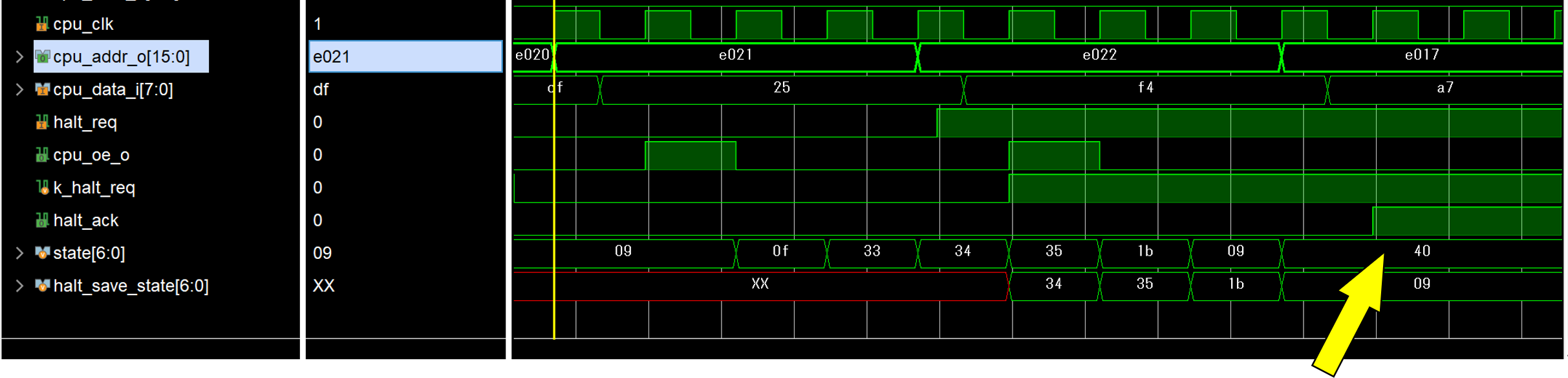

分岐先命令フェッチの前で新設のHALTステート(\$40)に遷移し、次のサイクルでHALTACKがアサートされています。HALTステートに遷移したので、halt_save_stateは、HALTステートの前の値(\$09)を保持し、更新は止まります。

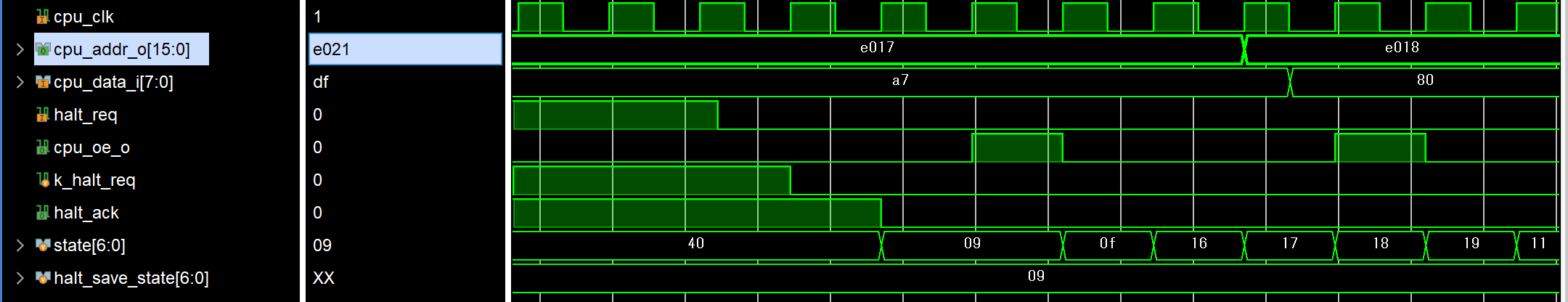

一方、HALTREQネゲート時の状態を観測すると、前稿でも見たように、内部ステートが回復され、分岐先である\$E017、\$E018の命令を順次フェッチしています。このように分岐先命令のフェッチが実行されており、命令の切れ目、具体的には分岐命令の実行後にHALTに入り、分岐先命令の実行前にHALTから出る動作を正しく実行しているようです。