|

28 |

サウンドコントローラの設計 (5) |

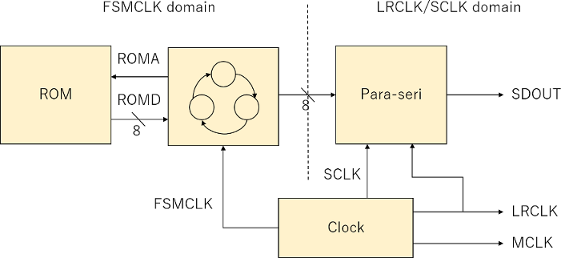

破裂音原因解析

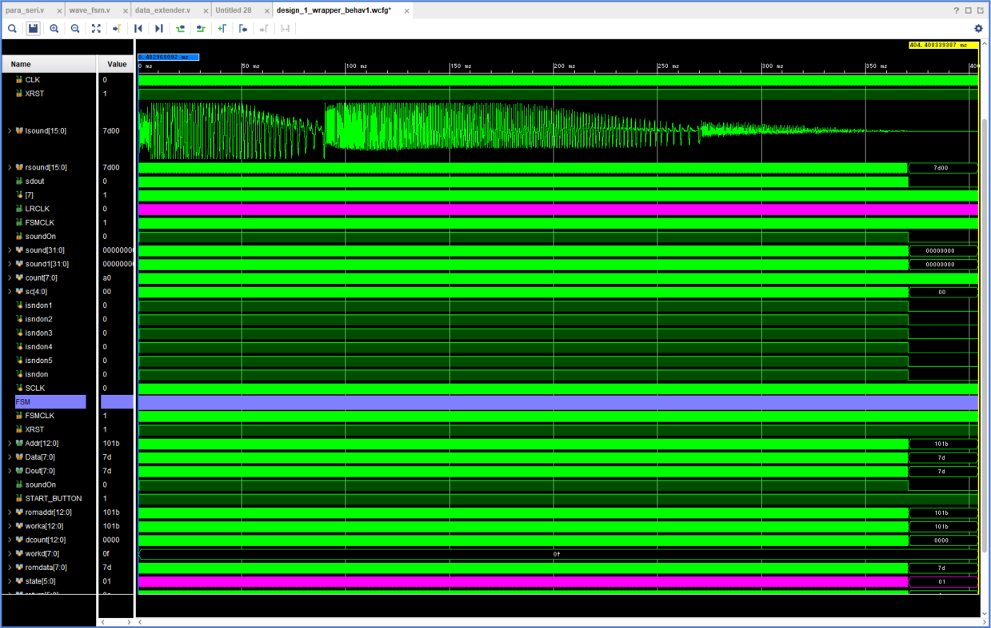

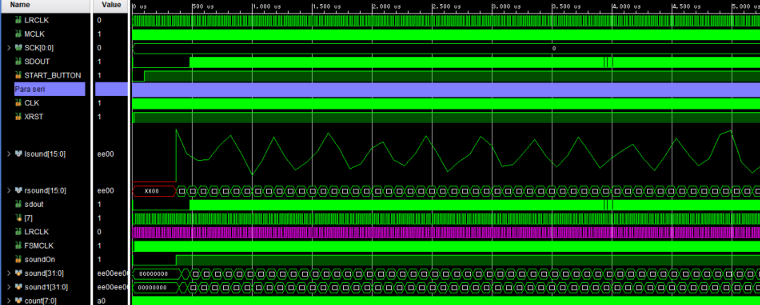

シミュレーション波形を確認すると、アナログ波形がなんだか尖っています。アナログとデジタルの一致性が必要で、そのためにはサンプリング周波数の1/2以上の周波数をカットする必要があります(標本化定理)。

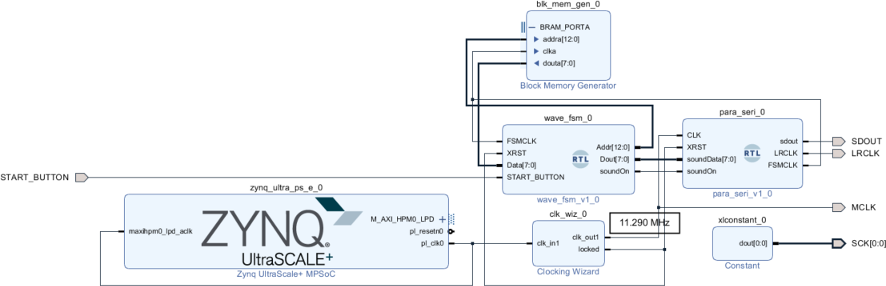

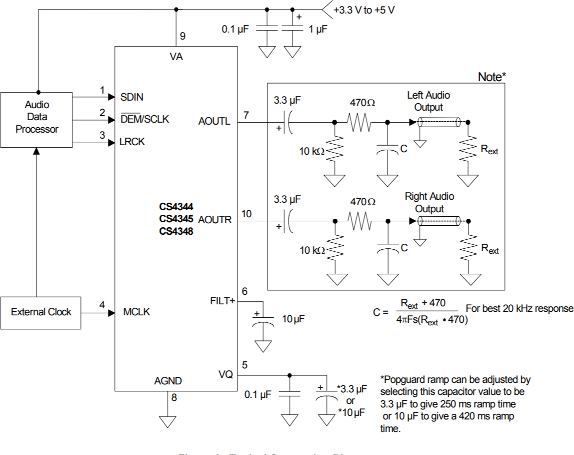

周波数帯域を制限するには22.05KHz以上をカットするロウパスフィルターを入れる必要がありますが、まずDACチップのデータシートの参考回路図を確認します。

図77.2のとおり、アナログ出力にRとCで構成されるロウパスフィルターが入っています。

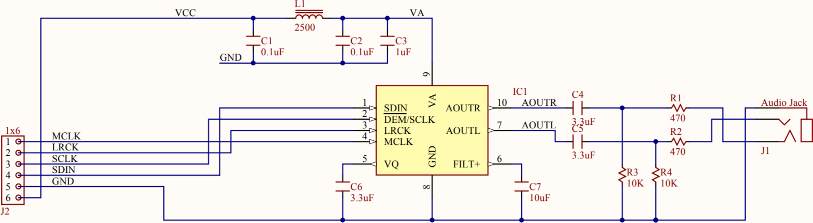

次にそれがどのように実装されているかを、PMOD DACモジュールのデータシートで確認します。

出力のロウパスフィルターが入っていないことがわかりました。 サンプリング周波数は44.1[KHz]であったので、ロウパスフィルターの時定数を決定します。 図77.2にCを求める式が書かれており、 $$ C=\frac{50+470}{4\pi\cdot 44.1\cdot 10^3\cdot 50\cdot 470}=40[nF]=0.04[\mu F] $$ となることから、アナログ出力に40nFのキャパシタ(0.04$\mu$Fのセラコン等)を挿入すれば良いことになります。