|

9 |

メイン・サブシステムI/Oアドレスデコード |

アドレスデコード及びレジスタ類を実装していきます。FM-7のI/Oの情報は参照場所にあります。メインシステムI/Oアドレスマップはその1から、サブシステムI/Oアドレスマップはその7からです。

メインシステム

FM-7メインシステムは64KbitDRAMが存在するため、フルデコードされています。

- $FD00 R キーボードデータ bit8

- $FD00 R キーボードデータ bit7-bit0

- $FD02 W 割込み(IRQ)マスクレジスタ(タイマ、キーボード)

- $FD03 R 割込み(IRQ)フラグレジスタ(タイマ、キーボード)

- $FD04 R 割込み(FIRQ)フラグ (ブレーク、アテンション)

- $FD05 R サブ状態 (busy)

- $FD05 W サブ・Z80制御 (HALT, Cancel, Z80)

- $FD37 W マルチページレジスタ (リセット時イネーブル)

- $FD38 R パレットレジスタ0から読み出し(初期値=黒)

- $FD38 W パレットレジスタ0へ書き込み

- $FD39 R パレットレジスタ1から読み出し(初期値=青)

- $FD39 W パレットレジスタ1へ書き込み

- $FD3A R パレットレジスタ2から読み出し(初期値=赤)

- $FD3A W パレットレジスタ2へ書き込み

- $FD3B R パレットレジスタ3から読み出し(初期値=マゼンタ)

- $FD3B W パレットレジスタ3へ書き込み

- $FD3C R パレットレジスタ4から読み出し(初期値=緑)

- $FD3C W パレットレジスタ4へ書き込み

- $FD3D R パレットレジスタ5から読み出し(初期値=シアン)

- $FD3D W パレットレジスタ5へ書き込み

- $FD3E R パレットレジスタ6から読み出し(初期値=黄)

- $FD3E W パレットレジスタ6へ書き込み

- $FD3F R パレットレジスタ7から読み出し(初期値=白)

- $FD3F W パレットレジスタ7へ書き込み

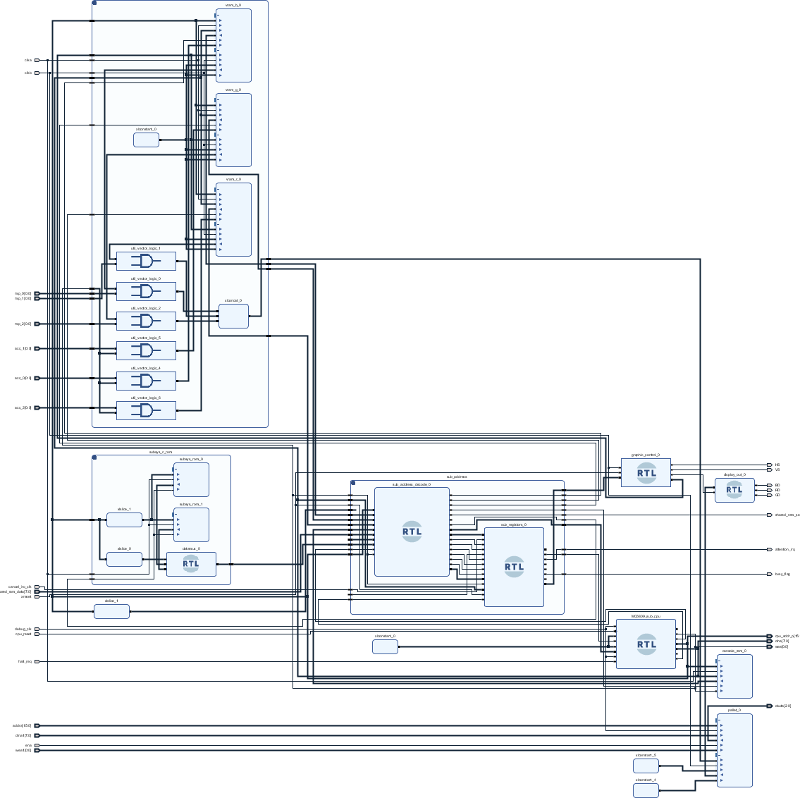

図144.1にメインシステムブロック図を示します。今回はアドレスデコーダとそれからアクセスされるレジスタを分離して設計しました。モジュラー化のためです。図では上方左側にアドレスデコーダ、上方右側にレジスタが配置されています。

サブシステム

FM-7サブシステムはフルデコードされていません。

- $D400 R キーボードデータ bit7-bit0

- $D401 R キーボードデータ bit8

- $D402 R キャンセルIRQ ACK

- $D404 R メインCPUへのアテンションIRQ

- $D408 R CRT ON

- $D408 W CRT OFF

- $D409 R VRAM Access Set

- $D409 W VRAM Access Reset

- $D40A R Ready

- $D40A W Busy

- $D40D R INS LED ON

- $D40D W INS LED OFF

- $D40E W VRAM Offset Address bit13-8

- $D40F W VRAM Offset Address bit7-0

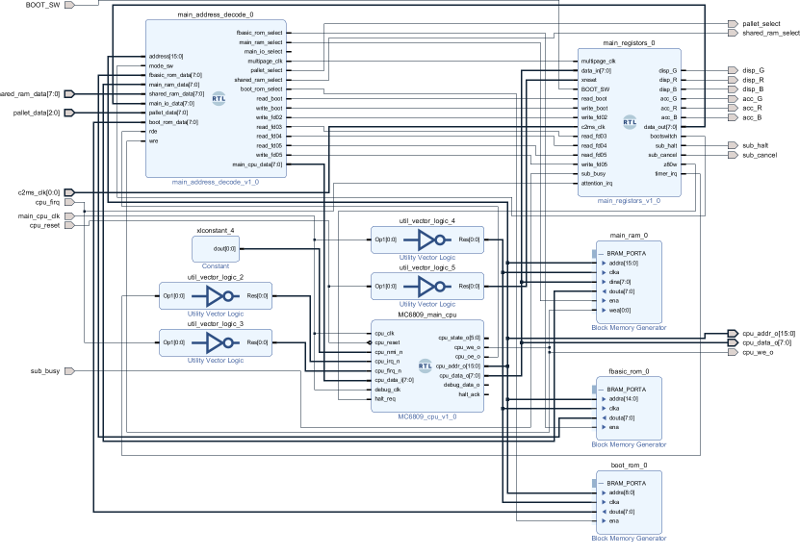

図144.2にサブシステムブロック図を示します。図では真ん中にアドレスデコーダとレジスタを階層ブロックにしたモジュールが配置され、その内部左側にアドレスデコーダ、右側にレジスタが配置されています。