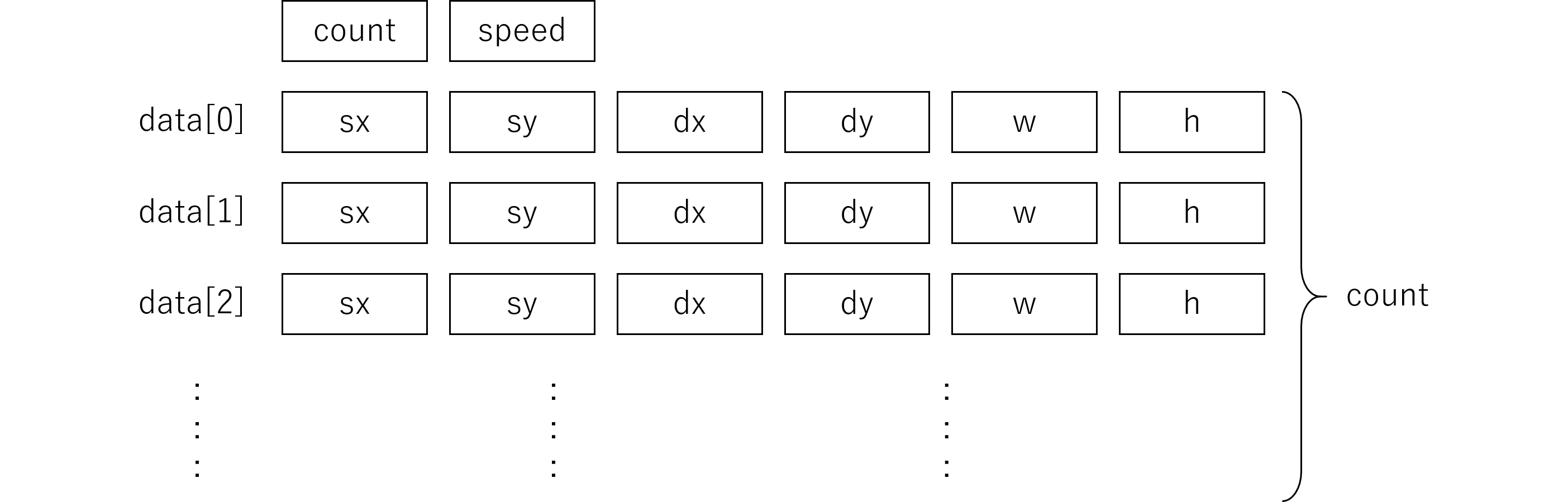

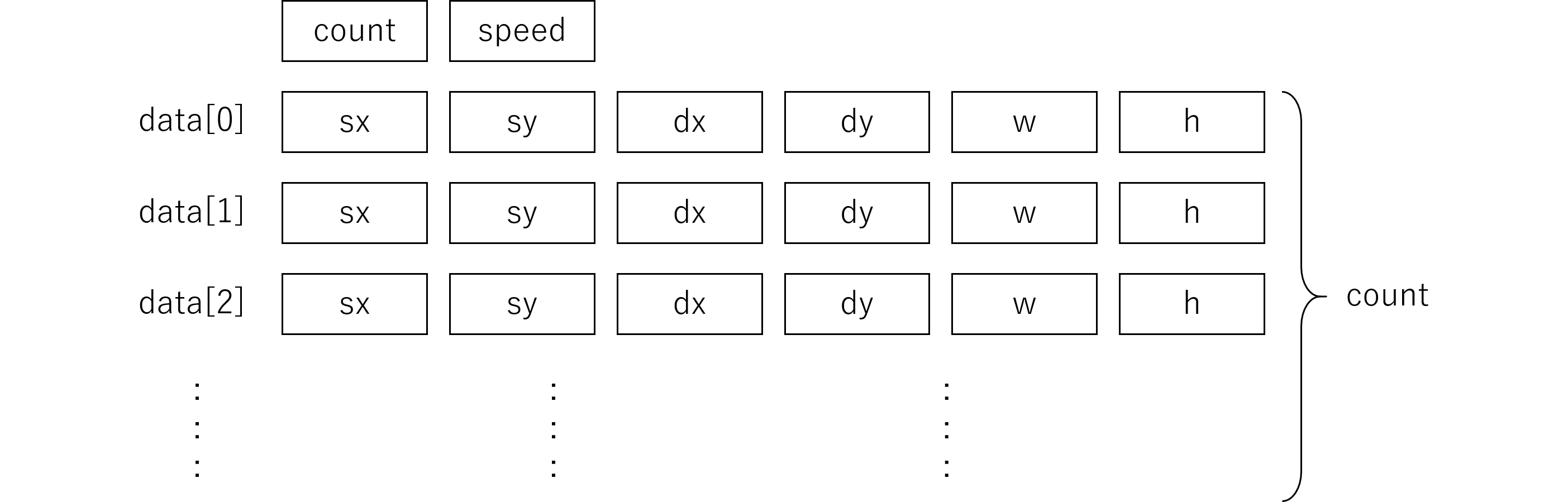

データ構造

以下にデータ構造を示します。

図417.1 構造体配列

図417.1 構造体配列

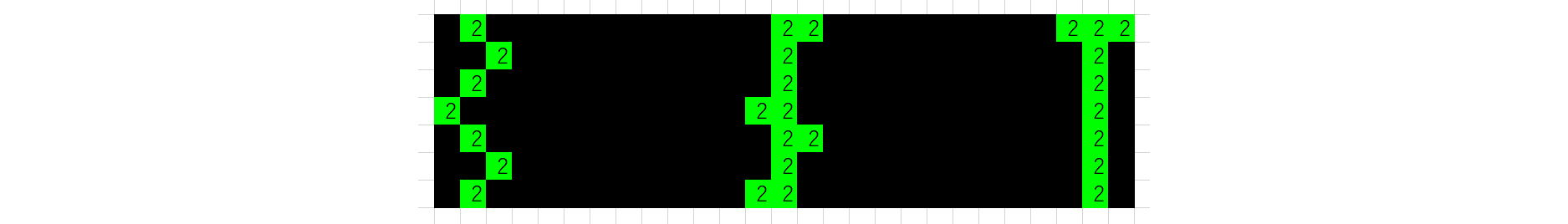

文字一つに対するパラメータは、図417.2のとおりです。

{sx, sy, dx, dy, w, h} = {パターンソースx, パターンソースy, デスティネーションx, デスティネーションy, 幅、高さ}

本来は図417.1及び図417.2のような構造体の配列としたかったのですが、bscでエラーとなるため、やむなく要素毎の配列に分解しました。構造体配列の実現は現在問い合わせ中です。

BSVコード

以下に分解したコードを示します。

UInt#(8) s1sx[19] = { 42, 50, 58, 77, 66, 42, 58, 74, 82, 42, 42, 90, 98,106, 58,114, 82,122, 66},

s1sy[19] = {137,137,137,126,137,137,137,137,137,129,129,137,137,137,137,137,137,137,137},

s1dx[19] = {112,120,128,136, 72, 80, 88, 96,104,112,120,128,136,144,152,160,168,176,184},

s1dy[19] = { 68, 68, 68, 68, 93, 93, 93, 93, 93, 93, 93, 93, 93, 93, 93, 93, 93, 93, 93},

s1w[19] = { 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5},

s1h[19] = { 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7};

UInt#(8) s2sx[23] = { 42, 50, 58, 66, 74, 82, 90, 98,106, 90,114, 58, 82,122, 90, 82, 90, 82, 42, 52, 68, 51, 2},

s2sy[23] = {145,145,145,145,145,145,145,145,145,145,145,145,145,145,145,162,162,145,145, 16, 64, 80, 80},

s2dx[23] = { 48, 56, 64, 72, 80, 88,104,112,120,128,136,144,152,168,176,184,192,200,208, 76, 80, 79, 78},

s2dy[23] = {125,125,125,125,125,125,125,125,125,125,125,125,125,125,125,125,125,125,125,142,155,169,184},

s2w[23] = { 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 16, 8, 11, 12},

s2h[23] = { 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 8, 8, 8};

UInt#(8) s3sx[40] = { 98,106, 42,114,122, 82, 90, 98,106,122, 98, 1, 9, 42,114,122, 82, 90, 90, 82, 98,106,114, 42, 82, 90, 98,106,114,122, 98,122,114, 42, 82, 90, 98,106,114,122},

s3sy[40] = {162,162,129,162,162,170,170,170,170,162,162,154,154,129,170,170,178,178,170,170,178,178,178,129,186,186,186,186,186,186,178,178,178,129,186,186,186,186,186,186},

s3dx[40] = { 96,104,112,120,128,136,144,152,160,168, 96,104,112,120,128,136,144,152,160,168, 96,104,112,120,128,136,144,152,160,168, 96,104,112,120,128,136,144,152,160,168},

s3dy[40] = {142,142,142,142,142,142,142,142,142,142,156,156,156,156,156,156,156,156,156,156,170,170,170,170,170,170,170,170,170,170,184,184,184,184,184,184,184,184,184,184},

s3w[40] = { 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5},

s3h[40] = { 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7, 7};

"SPACE INVADERS"の文字列を、最初は"SPACEINVADERS"とタイミングを空けずに場所を空けて表示していました。が、Youtubeを見ると、"SPACE△△INVADERS"と、空白(△)は場所だけでなくタイミングも空いているようだったので、文字列も"SPACE△△INVADERS"と設定しています。

もうひとつ注意点として、オープニングアニメーション中のウエイト中にSキー(Sボタン)が押された場合は直ちにゲームスタートとなることです。

前のブログ

次のブログ

前のブログ

次のブログ