|

25 |

BSVによるサウンドFSMの再設計 (5) |

プチ音の再修正

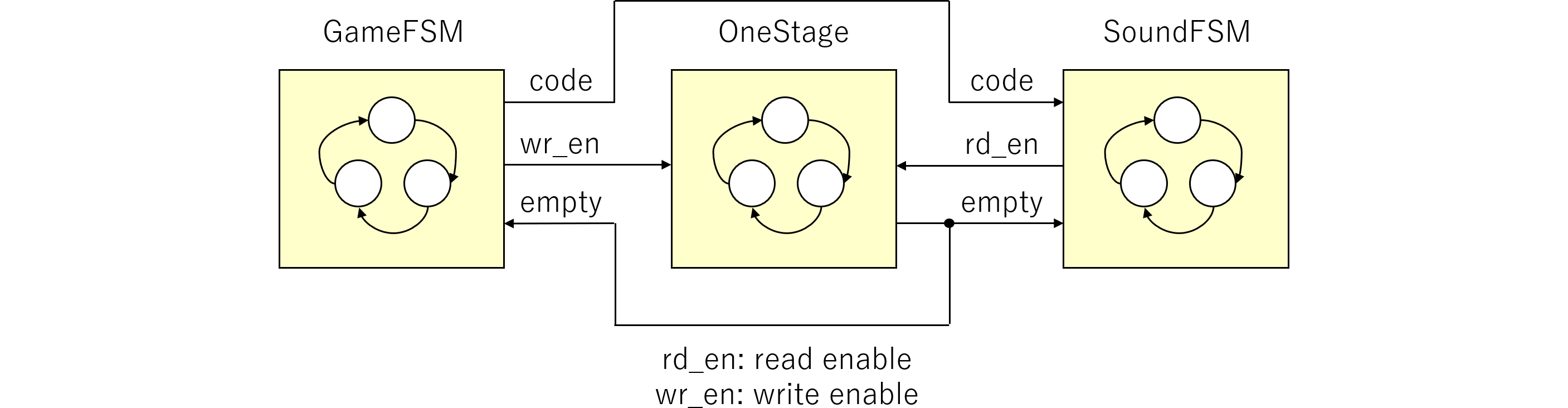

ゲームFSMからのコマンドにより、サウンドはサウンドFSMで演奏されます。サウンドとサウンドの間は、サウンドが鳴り続けないように、一旦OFFにします。

シミュレーション波形を観測している際に、UFO飛行音は連続して再生されるので、一旦サウンドをOFFにするとプチ音がするのではないかと思い、ONを継続するように変更したところ、却ってプチ音がするようになりました。

確かにステートベース設計の旧版では一旦サウンドをOFFにしていたため、そのように戻したところ、プチ音は聞こえなくなりました。

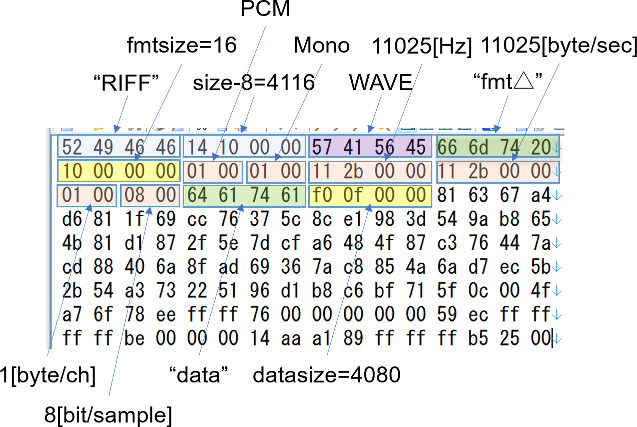

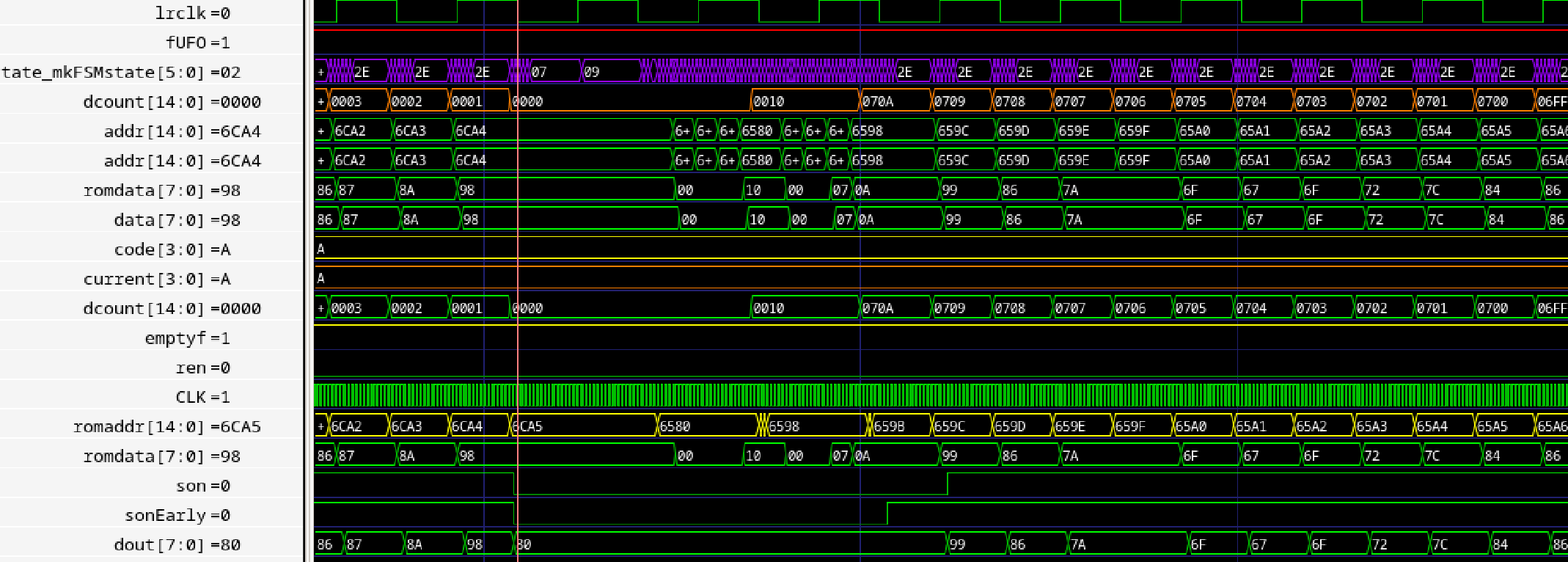

修正前はson=False、dout=NULLのためにプチ音が鳴っていると思い、son=True, dout=前データを継続としましたが、却ってプチ音が鳴るようです。波形は再修正後です。

サウンドFSM(UFO音チャネル#3)のアルゴリズム

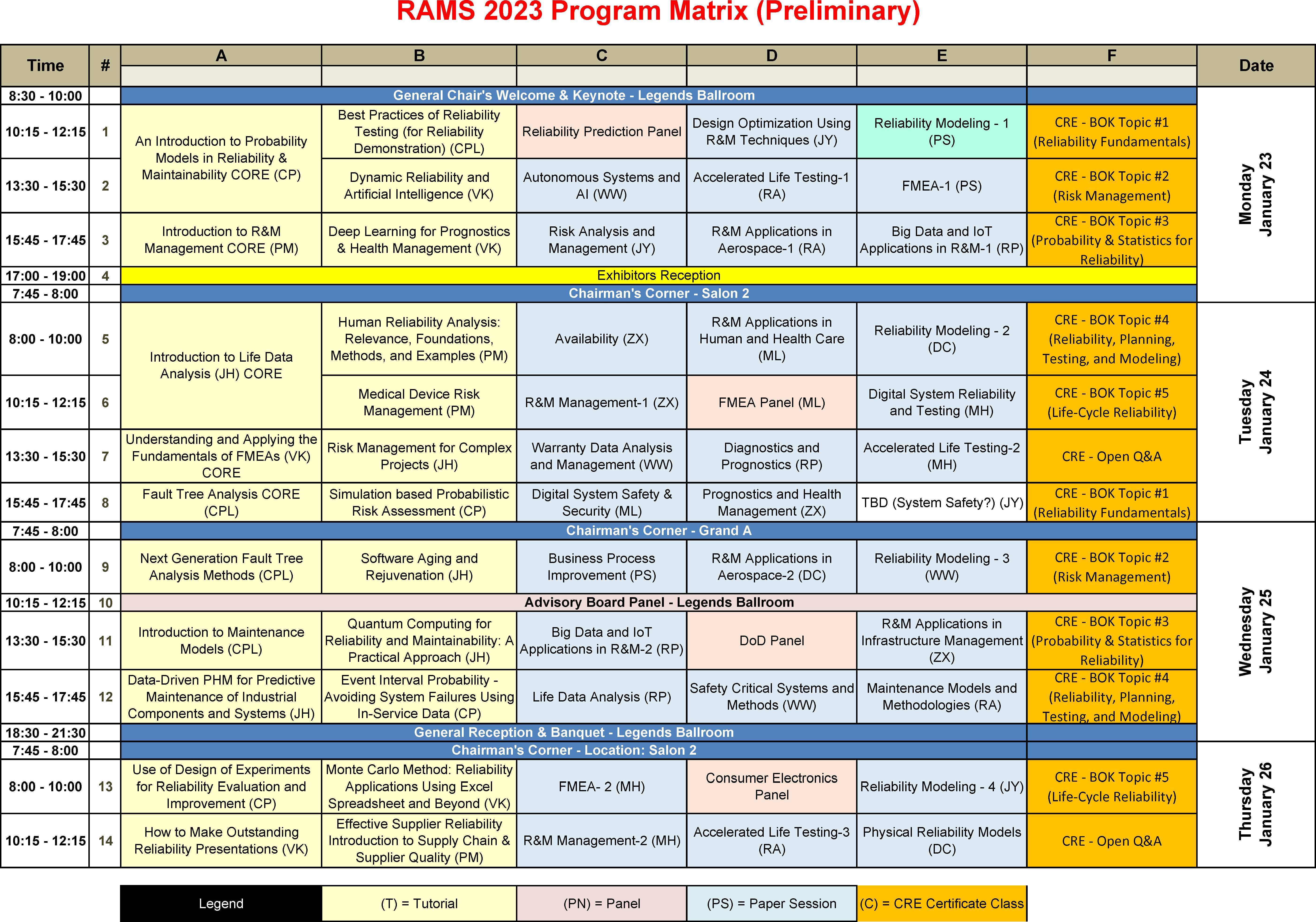

フラグのON/OFFアルゴリズムを表500.1にまとめました。

| No. | コード | キュー | ハンドシェーク(rd_en ) | サウンド間 | フォーマット&演奏 |

|---|---|---|---|---|---|

| 1 | UFO爆発, UFO飛行音 | !empty | rd_en <= True | son <= False | Play |

| 2 | UFO飛行音 OFF | !empty | rd_en <= True | son <= False | - |

| 3 | UFOフラグ | - | rd_en <= False | son <= False | UFO飛行音Play |

| 4 | 他FSMコード | !empty | rd_en <= False | son <= False | - |

上記でプチ音対策で修正した箇所は表500.1の緑色表示の部分です。一旦son <= TrueとONを継続するように修正しましたが、OFFに戻しました。

まず、通常のサウンドNo.1及び3は以下のフローとなります。

- GameFSMはempty == Trueの場合にコードを出力し、同時にOneStageFSMに対してwr_enを発行します。

- OneStageFSMはempty = False(=Full)とします。

- SoundFSMは正当コードかつempty == False (=Full)を待ち、入力されたらrd_en = TrueをOneStageFSMに返します。

- OneStageFSMはempty = Trueとします。

- GameFSMはempty == Trueを待ち、入力されたら終了です。

- SoundFSMもempty == Trueを待ち、入力されたらrd_en = Falseとします。

- SoundFSMはUFOオフコマンドならUFOフラグをOFFして終了します。

- SoundFSMはUFOオフコマンドでなければフォーマットをデコードします。

- SoundFSMはサウンドをカウント分演奏します。

次に、通常のサウンドで無い場合No.2は、UFOフラグがTrueの時であり、GameFSMのコードがキューに無くてもUFO飛行音を演奏し続けます。

- GameFSMはなにもしません。

- SoundFSMはUFOフラグ==Trueの場合には、実行しますがrd_en = Trueは返しません。これはキューに何もないためです。

- SoundFSMは内部的にはUFO飛行音と扱います。

- SoundFSMはフォーマットをデコードします。

- SoundFSMはサウンドをカウント分演奏します。