|

24 |

Pipeline processorの設計 (16) |

EIT処理

EIT処理は

- <MA>においてEITの優先度判定し、最弱のEITを識別

- EITスタックにEITの分岐先(EITハンドラ先頭アドレス)をストア

- EIT原因を無効化

以上を繰り返し、最後のひとつに対してはスタックに格納せずにEIT種別による分岐先をPCに格納します。

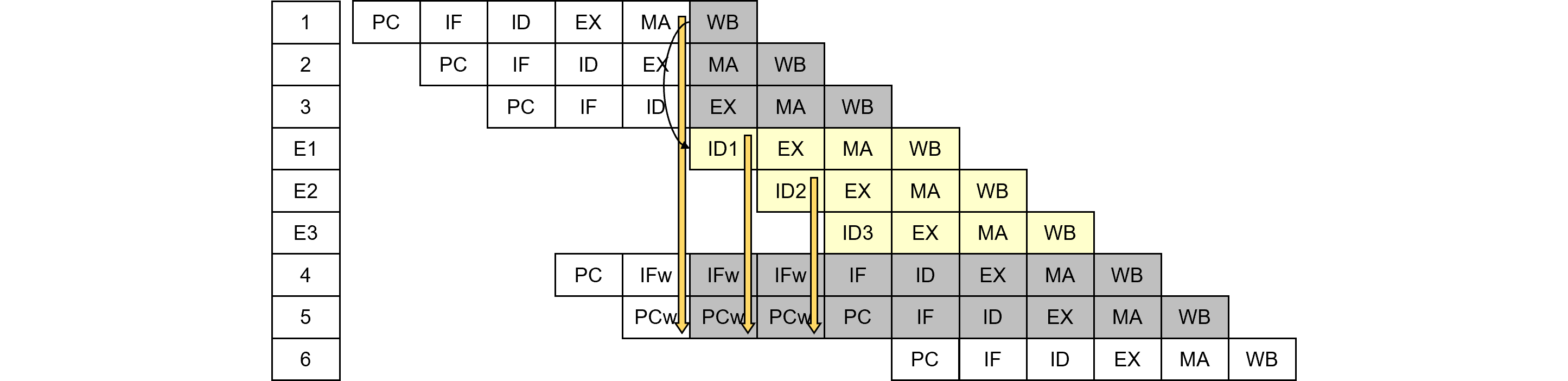

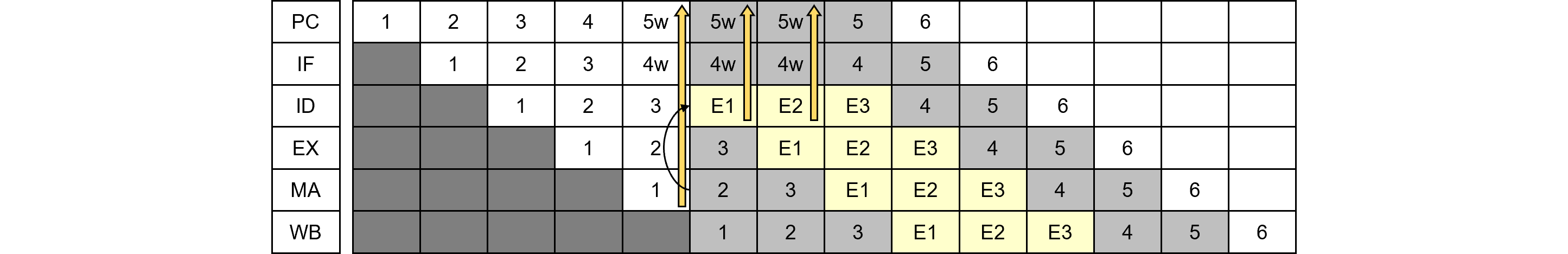

これはメモリアドレス計算やメモリアクセスを伴うので<ID>のFSMにより実行します。後続の命令はキャンセルされます。以下に具体例を示します。

- 1の命令の<MA>でそのパイプラインストリームで集められたEIT要因を判定します。前後のストリームは見ません。

- 後続命令ストリームをキャンセルします。具体的には2, 3, 4, 5までがパイプラインに入っているので全てキャンセルします。

- <MA>から<ID1>に乗り換えることから、<ID>より前の<IF>と<PC>を持つ、後続の4, 5の命令はキャンセルされるだけでなく、ウエイトされます。

- <ID1>のFSMが起動され、弱いEIT先行してEIT分岐先をスタックに格納します。この場合はE1が最弱でありスタックに格納すると同時にEIT要因を無効化します。同時にSPを+4します。

- 次に<ID2>のFSMが起動され、同様にEIT分岐先をスタックに格納します。SPは前パイプライン<EX>からバイパスします。同時にEIT要因を無効化し、SPを+4します。

- 最後に<ID3>のFSMが起動され、残った最強のEIT分岐先を<EX>で計算します。

- そのサイクルは分岐先の<PC>と同一であり、6のEITハンドラが起動されます。