|

21 |

Pipeline processorの設計 (13) |

キャンセル

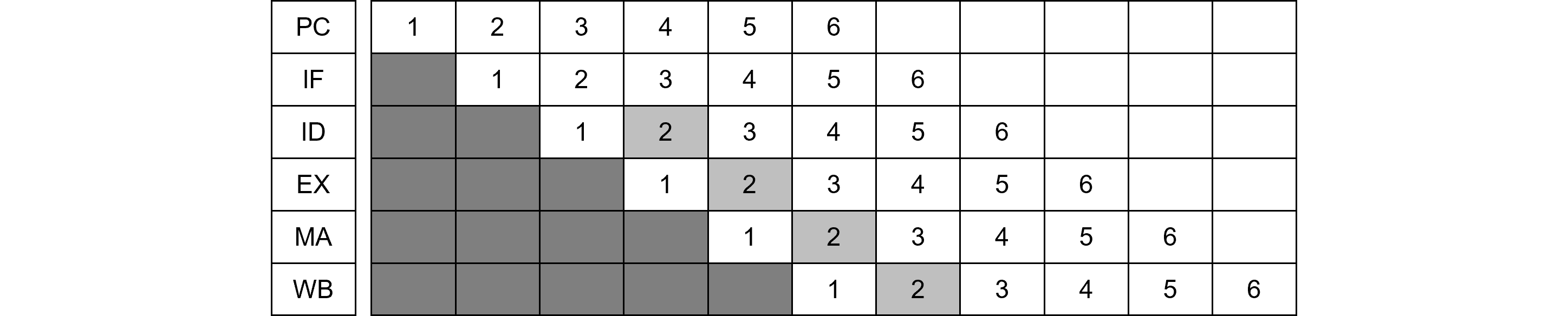

パイプラインウエイトと並んで重要な制御がパイプラインキャンセルです。パイプライン中に例外的な事象が起き、そのパイプラインストリームを無効化します。これは前稿で述べたバブルと同様に、あるステージを無効化(Valid信号=false)することで実現します。パイプライン中をinvalidが流れ、最後に<WB>においてレジスタに書き込まないことで実現します。<MA>においてはinvalidである場合にはメモリアクセスFSMは起動しません。

分岐キャンセル

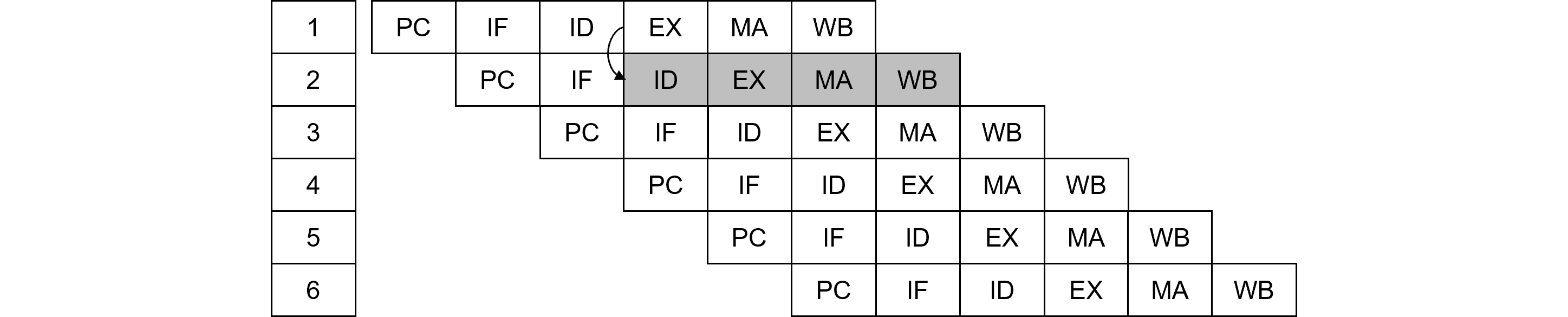

分岐の場合の具体例を示します。分岐先及び非分岐先(+4)を投機的に計算しておくことで、相対分岐の高速化を図ります。これは分岐命令をデコードした時点で既に前の命令で演算フラグが確定しているものとしています。

1の命令が相対分岐であったとき、<ID>において命令をデコードと並行して相対分岐だと思って分岐先を計算します。タイミングとしては3の命令の<PC>と同一です。その命令の最後に相対分岐かどうかが確定し、かつ条件分岐の成立が確定するので、PC選択のマルチプレクサにおいて、分岐先を選択します。同時に後続命令である2のパイプラインストリームにinvalidを流し、パイプラインキャンセルを実行します。