|

22 |

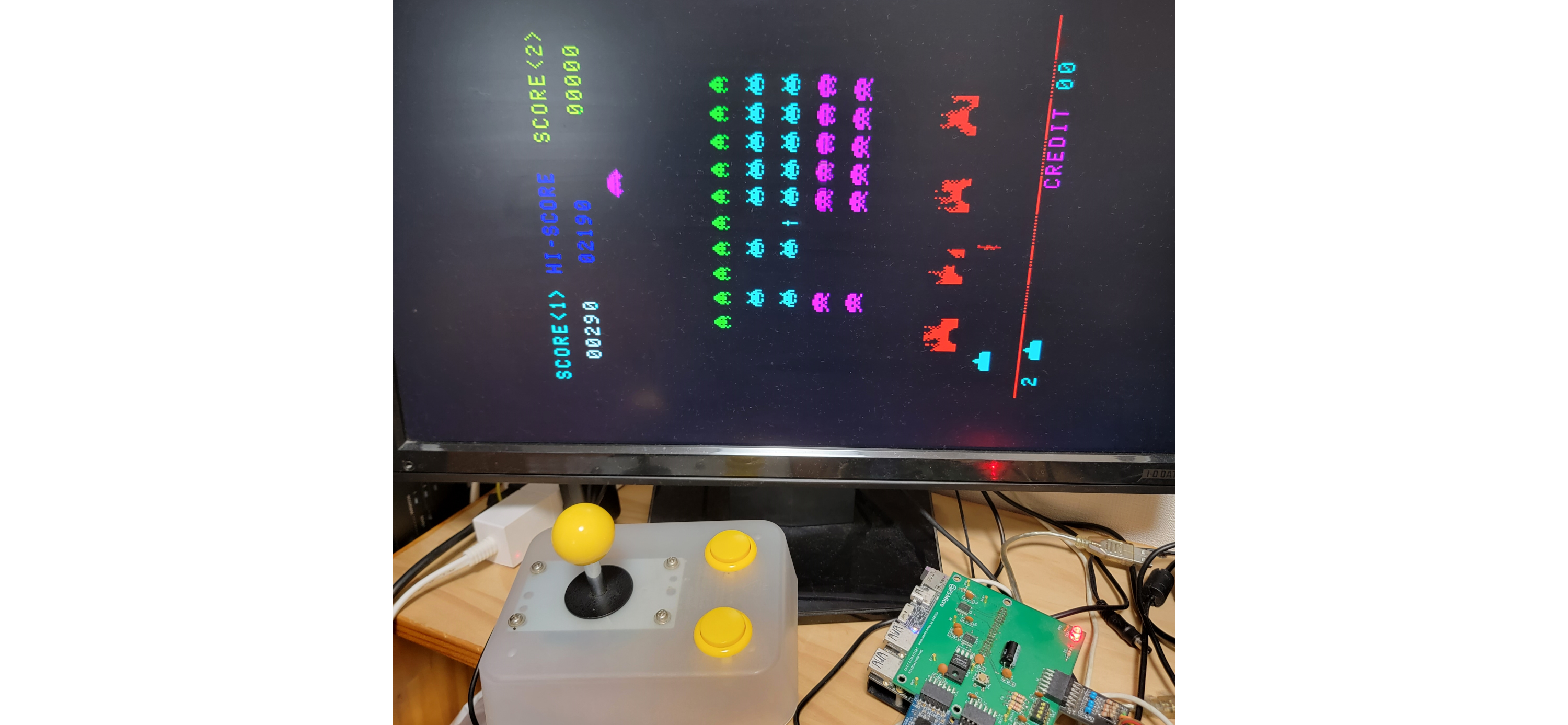

BSVによるSpace Invadersの変更 (6) |

|

オープニングアニメーションの追加

テスト用のソースを示します。コンパイル時間短縮のため、ゲーム部分をカットしています。

// メインフロー

Stmt main = seq

while (True) seq

while (!fbutton) seq

openingAnimation; // Fボタンによりブレーク

endseq // while

openingDisplay; // 表示のみ、ボタンを待たない

await(sbutton); // Sボタンによりブレーク

openingDisplay2; // タイマーによりブレーク

// game start

endseq // while

endseq;

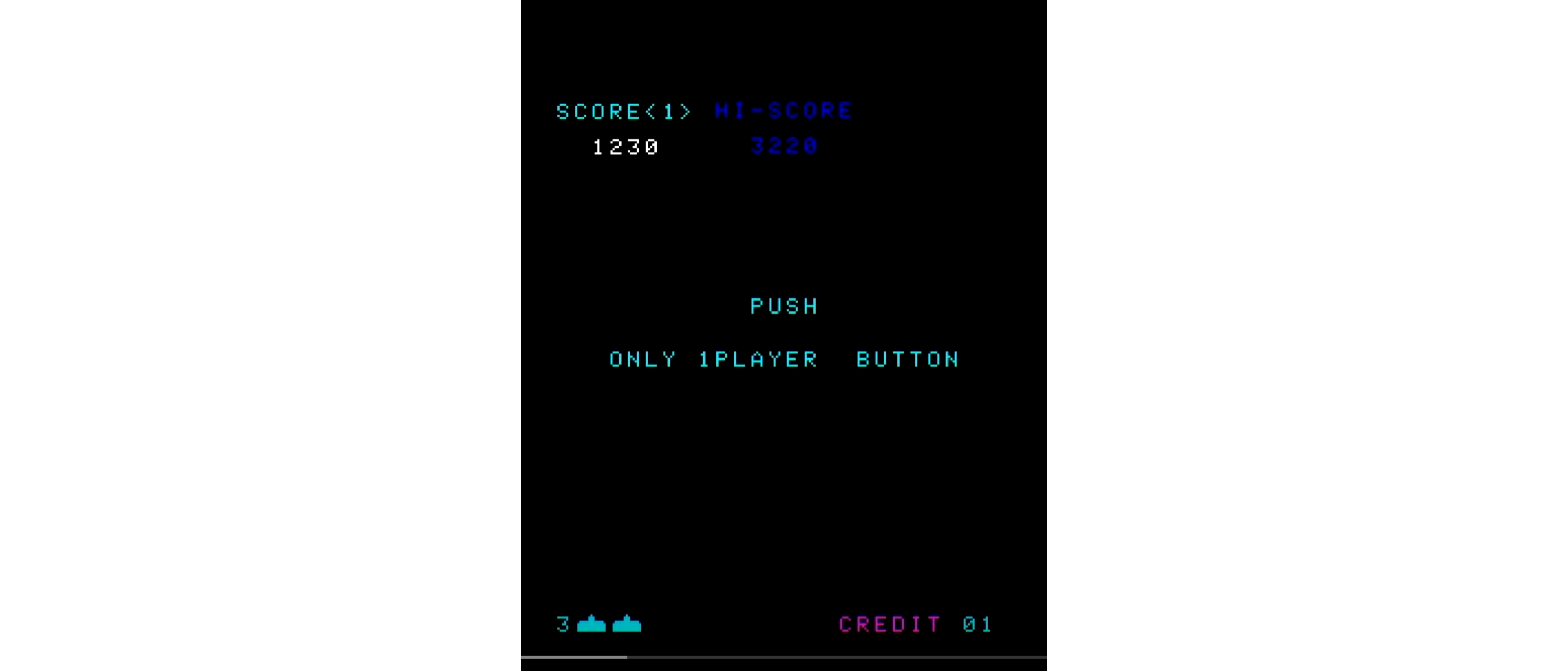

// CREDIT 01, "PUSH ONLY 1PLAYER BUTTON"

function Stmt openingDisplay;

return (seq

eraseArea( 0, 41, 255, 199); // erase screen

stringS5; // PUSH ONLY ...

copyArea(10, 162, 217, 241, 5, 7); // CREDIT 00->01

endseq);

endfunction

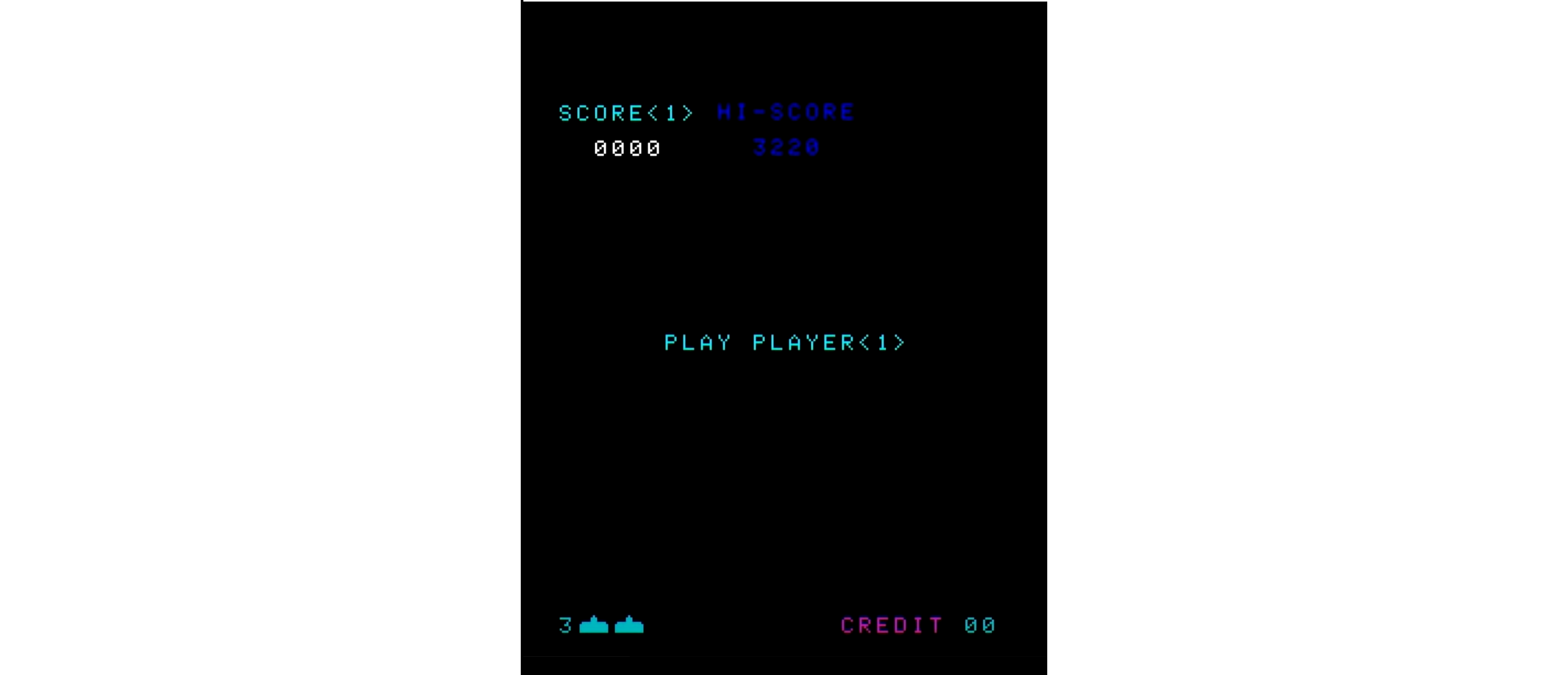

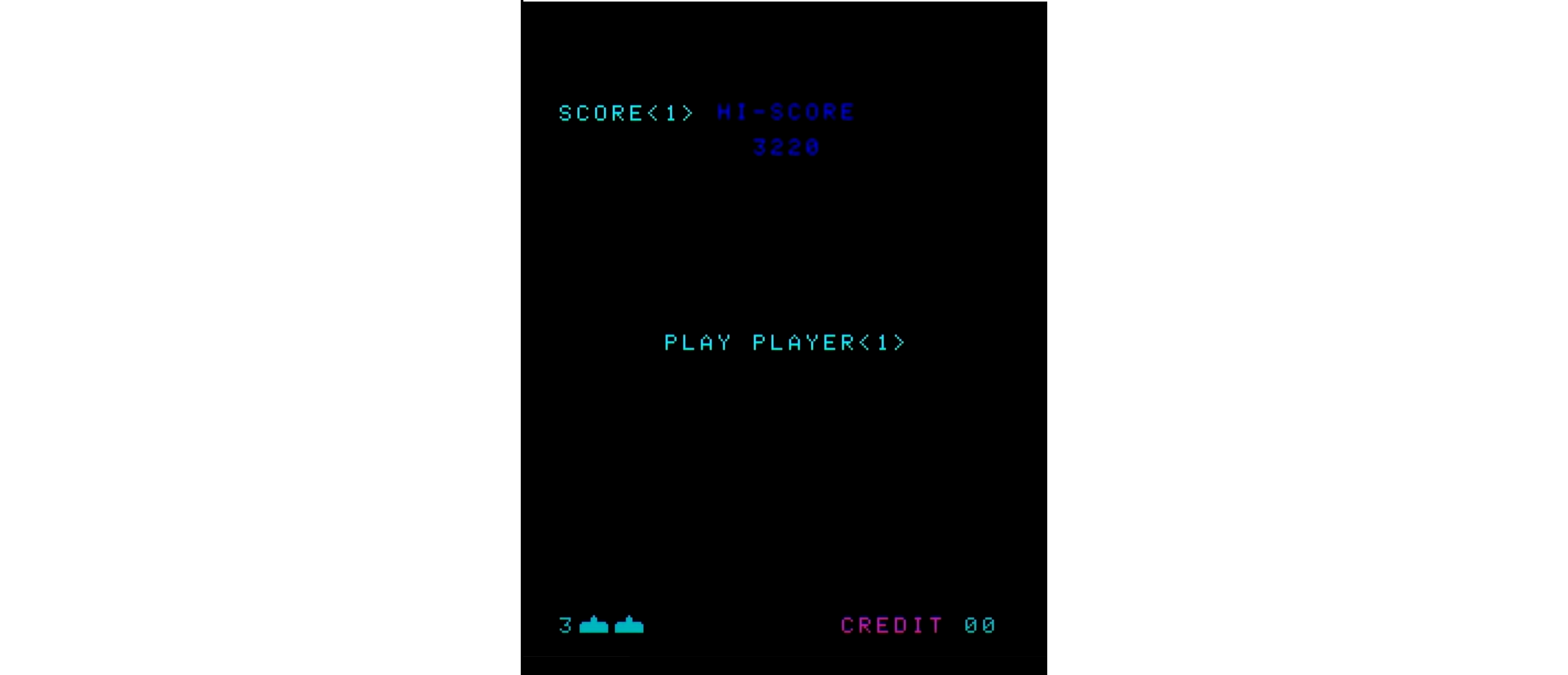

// CREDIT 00, "PLAY PLAYER<1>, 00000"

function Stmt openingDisplay2;

return (seq

eraseArea( 0, 41, 255, 199); // erase screen

stringS6; // PLAY PLAYER<1>

copyArea(2, 162, 217, 241, 5, 7); // CREDIT 01->00

for (i <= 1; i < 15; i <= i + 1) seq

// erase zero

eraseArea(40, 25, 37, 7);

wait_timer(`TICK_WAIT4); // wait 66.66msec

stringS7; // 00000

wait_timer(`TICK_WAIT4); // wait 66.66msec

endseq // for

endseq);

endfunction