|

10 |

サウンドコントローラの設計 (3) |

設計指針

設計指針を記述していきます。

- サウンドデータはwaveフォーマットでROMに8bit単位で格納する。フォーマットは非圧縮PCM、8bit、モノラル、11.025KHzサンプリング

- FSMはFSMCLKで動作する。FSMCLK=176.4KHz(=1/8*SCK)。

- 8bitサウンドデータの読み出しは、FSMからアドレスを与えることで行う。

- FSMから並列直列変換(以降パラシリ)にROMデータを供給する。

- パラシリでは8bitデータをDACの要求する16bitデータに伸長する。具体的にはROMデータを上部8bitに詰め、下部8bitはゼロを詰める。

- パラシリのシフトはSCK(=BCLK)で行う。SCK=1.4112MHz。ただし、これを出力しなければ自動的にDACの内部クロックモードとなり、MCLKから適当にシフトクロックを生成するとのこと。

- パラシリの1フレームはLRCLKの立下りで開始する。LRCLK=44.1KHz(=1/32*SCK)。

- マスタークロックはMCLK=11.2896MHz

- 変換されたシリアルデータは1SCK遅らせてDACに出力する。

アーキテクチャ設計

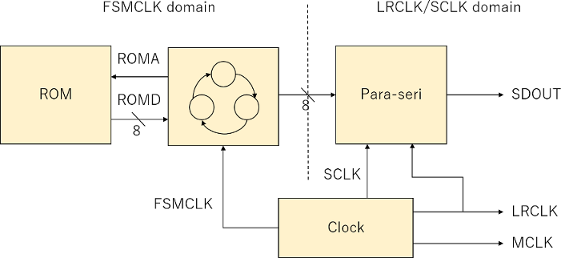

以上の指針からブロック図を書くと以下のようになります。

詳細設計

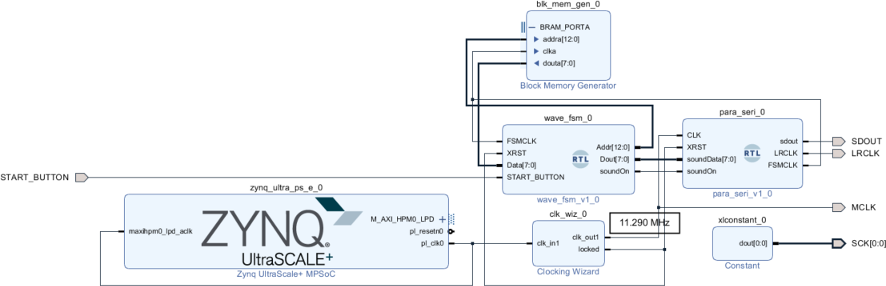

上記ブロック図(アーキテクチャ設計)をもとに、ブロック内部をRTLで記述したものを下図に示します。 SCKはシリアルクロック(=ビットクロック)ですが、内部クロックモードを使用するために、コンスタント出力としています。基本的にZynqを除き、ブロック図と一致しています。