|

21 |

BSVによるメモリダンプモジュールの設計 (6) |

|

Posts Tagged with "FPGA"

既に発行済みのブログであっても適宜修正・追加することがあります。We may make changes and additions to blogs already published.

|

20 |

BSVによるメモリダンプモジュールの設計 (5) |

|

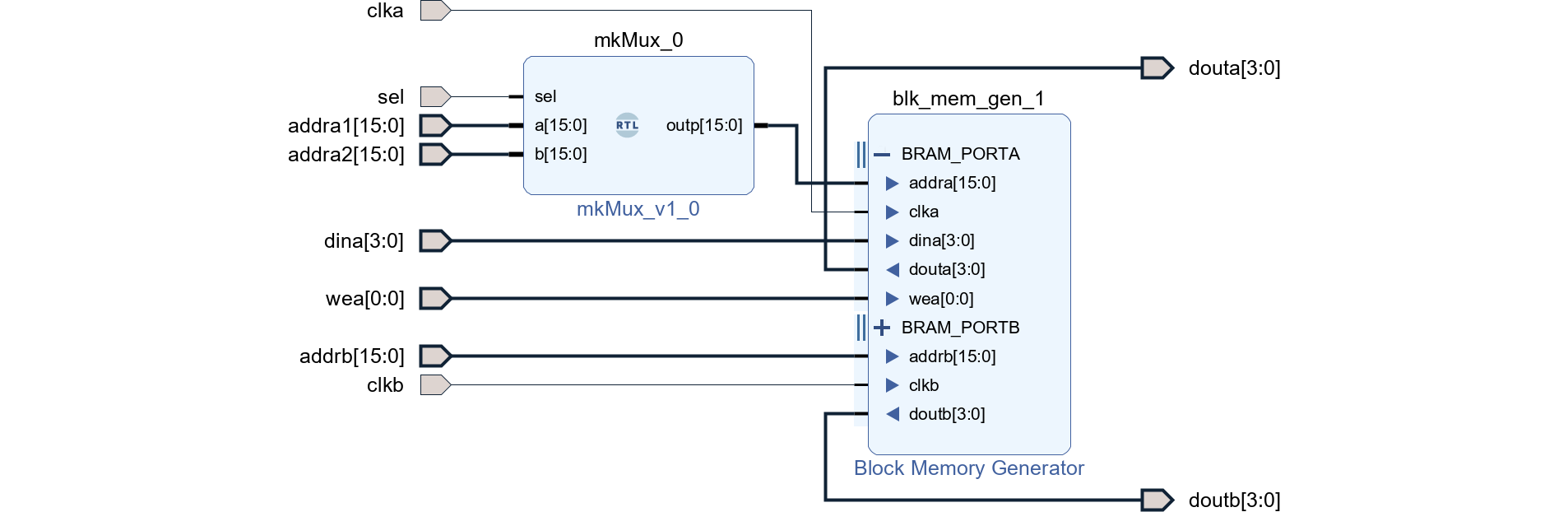

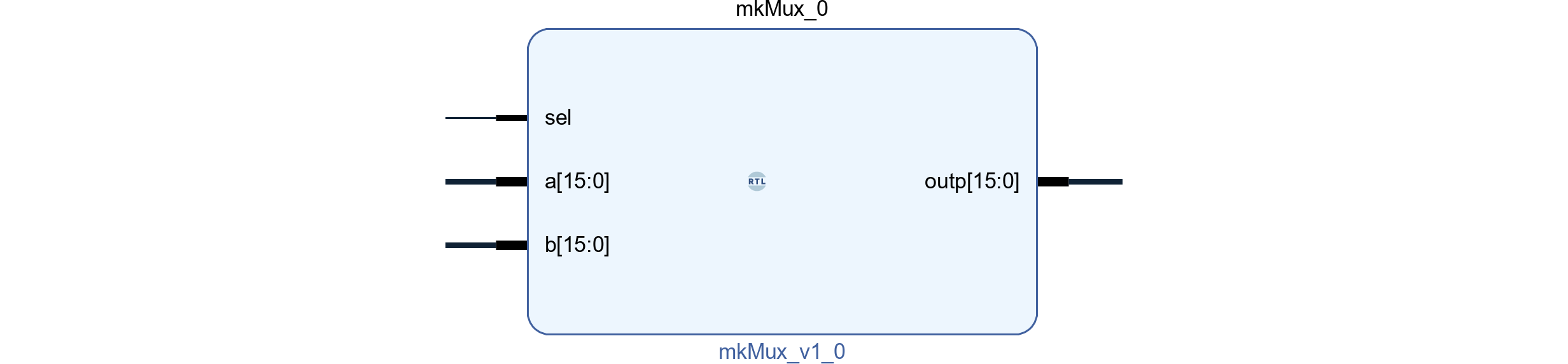

RAMアドレスマルチプレクサの設計

VRAMアクセスするマスタに、FSM、CRTCに加えてメモリダンパが加わりました。しかしながらBRAMのポートが2つまでなので、FSM側のアドレスバスをシェアします。CRTCは常にアクセスしているのに比べて、メモリダンパはFSMが動作していない時のメモリ状態を観測するためだからです。アドレスシェアのためのマルチプレクサを設計します。

Mux.bsv

typedef Bit#(16) Addr_t;

interface Mux_ifc;

(* prefix="" *)

method Addr_t outp(Bool sel, Addr_t a, Addr_t b);

endinterface

(* synthesize, always_ready = "outp", no_default_clock, no_default_reset *)

module mkMux(Mux_ifc);

method Addr_t outp(Bool sel, Addr_t a, Addr_t b);

if (sel) return b;

else return a;

endmethod

endmodule

出力のハンドシェーク端子は不要であるため、

(* synthesize, always_ready = "outp" *)

を指定して削除しています。さらに、組み合わせ回路であるため、clock, resetを使用していないので、それらポートを削除するために、

(* no_default_clock, no_default_reset *)

を指定しています。また、入力ピン名が、メソッド名_変数名、例えばoutp_a等のように複雑になるのを防止するため、

(* prefix="" *)

を指定してメソッド名を消しています。

これを合成すると以下のようなVerilogになります。

mkMux.v

//

// Generated by Bluespec Compiler (build 38534dc)

//

// On Thu May 20 14:21:23 JST 2021

//

//

// Ports:

// Name I/O size props

// outp O 16

// sel I 1

// a I 16

// b I 16

//

// Combinational paths from inputs to outputs:

// (sel, a, b) -> outp

//

//

`ifdef BSV_ASSIGNMENT_DELAY

`else

`define BSV_ASSIGNMENT_DELAY

`endif

`ifdef BSV_POSITIVE_RESET

`define BSV_RESET_VALUE 1'b1

`define BSV_RESET_EDGE posedge

`else

`define BSV_RESET_VALUE 1'b0

`define BSV_RESET_EDGE negedge

`endif

module mkMux(sel,

a,

b,

outp);

// value method outp

input sel;

input [15 : 0] a;

input [15 : 0] b;

output [15 : 0] outp;

// signals for module outputs

wire [15 : 0] outp;

// value method outp

assign outp = sel ? b : a ;

endmodule // mkMux

わずか、 assign outp = sel ? b : a ; という一行のverilogを得るためにいろいろと記述していますが、これはBSVの練習のためでもあります。

|

13 |

BSVによるメモリダンプモジュールの設計 (4) |

|

以下のスクリプトでVerilogシミュレーションを実行します。

bsc -verilog -u Tb.bsv

cp top-original.v top.v

emacs -nw top.v

// emacsでautomodeにより、top.vを生成

iverilog -y /usr/local/lib/Bluespec/Verilog/ top.v mkTb.v mkUart.v -o mkTb.exe

./mkTb.exe

gtkwave -A verilog.vcd

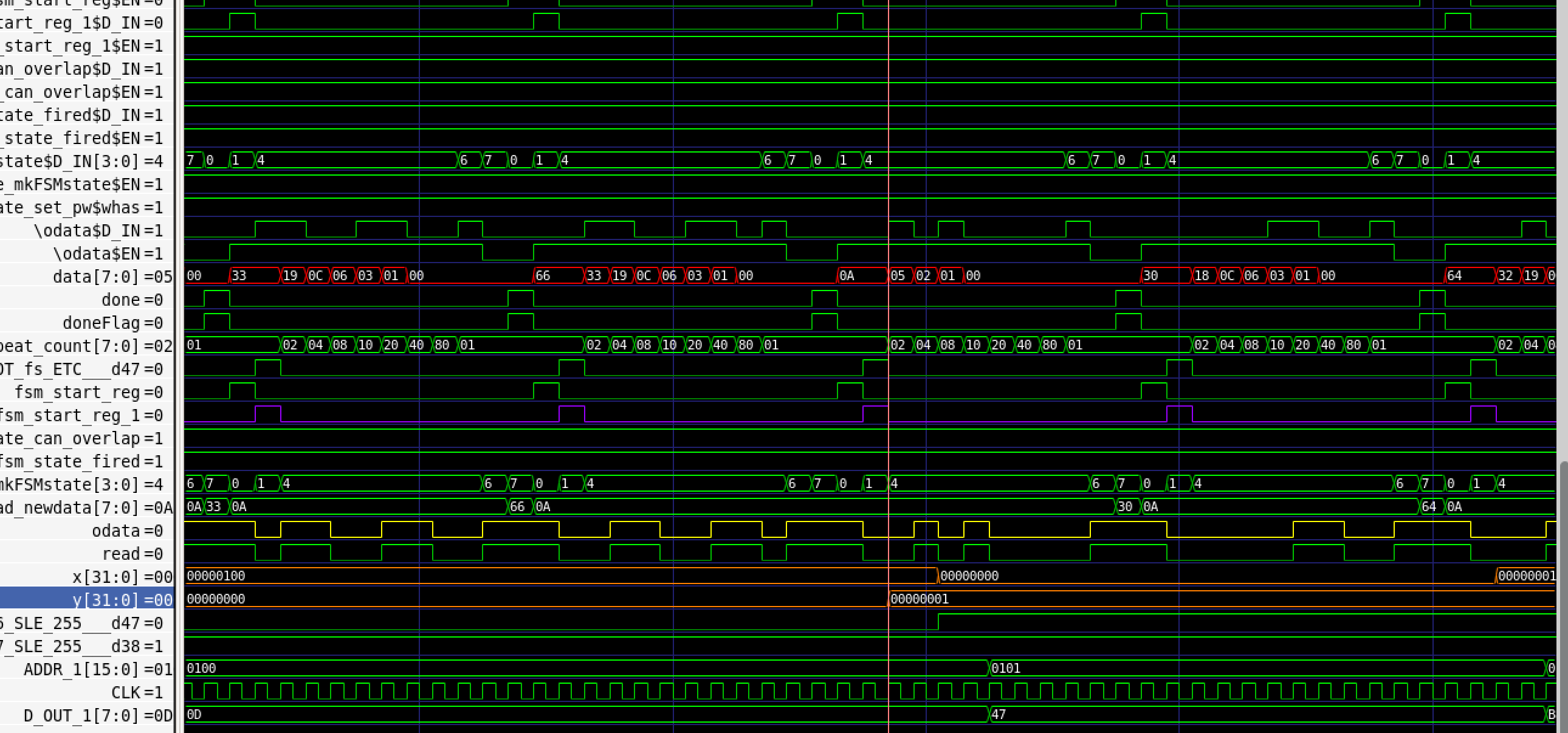

図はちょうど1行を送信したところで、横方向のxが256(xは255までだがチェックサム出力の際に256となる)から0に戻り、縦方向のyが0から1になった時点の波形です。データを0x33, 0x66, 0x0a, 0x30, 0x64と送信しています。

ストップビットを1ビットに削ったところ、1,582,090サイクルとなりました。1アスキーバイトあたり12サイクルなので、8bitの他、スタートが1bit、ストップが3bit相当となっています。送信時間は

- 115,200bpsでは6.9秒

- 230,400bpsでは3.4秒

- 460,800bpsでは1.7秒

- 921,600bpsでは0.9秒

となります。バイナリだとこれの半分の時間となるはずですが、デバッグの都合上アスキーコードの転送とします。

|

12 |

BSVによるメモリダンプモジュールの設計 (3) |

|

前稿の疑似コードをBSVに変換します。作成したBSVプログラムを以下に示します。

Tb.bsv

import StmtFSM::*;

import mkUart::*;

import RegFile::*;

typedef Bit#(16) Addr_t;

typedef Bit#(4) Data_t;

typedef Bit#(8) Byte;

(* synthesize *)

module mkTb();

RegFile#(Addr_t, Data_t) rom <- mkRegFileLoad("data.hex", 0, 65535);

Reg#(Addr_t) address <- mkReg(0);

Reg#(Data_t) data <- mkReg(0);

Reg#(Byte) byteData <- mkReg(0);

Reg#(int) x <- mkReg(0);

Reg#(int) y <- mkReg(0);

Reg#(Data_t) checksum <- mkReg(0);

Uart_ifc uart <- mkUart();

function Stmt nibbleOut(Data_t nibble);

return (seq

byteData <= extend(nibble) + (nibble >= 10) ? (- 10 + 8'h61) : 8'h30;

uart.load(byteData);

// $write("%c", byteData);

endseq);

endfunction: nibbleOut

Stmt test = seq

for (y <= 0; y <= 255; y <= y + 1) seq

checksum <= 0;

for (x <= 0; x <= 255; x <= x + 1) seq

data <= rom.sub(address);

address <= address + 1;

checksum <= checksum + extend(data);

nibbleOut(data);

endseq

nibbleOut(truncate(checksum >> 4));

nibbleOut(truncate(checksum));

uart.load(8'h0a); // LF

// $display("");

endseq

await (uart.done());

$finish;

endseq;

mkAutoFSM(test);

endmodule

|

11 |

BSVによるメモリダンプモジュールの設計 (2) |

|

上位モジュールの最適化

メモリダンプアルゴリズムが疑似コードにより記述できたので、最適化を実施します。以下のような処理が3回出てくるので、nibbleOutという関数にまとめます。

lower += (lower >= 10) ? (-10 + "a") : "0";

この共通化を実施した全体の動作を疑似コードにより示します。

疑似コード

int x, y, address;

byte byteData, checksum;

address = 0;

for (y=0 to 255) {

checksum = 0;

for (x = 0 to 255) {

data = memory[address++];

checksum += data;

nibbleOut(data);

}

nibbleOut(checksum>>4);

nibbleOut(checksum);

uart.load(LF);

}

function nibbleOut(nibble) {

byteData = nibble + (nibble >= 10) ? (- 10 + "a") : "0";

uart.load(byteData);

}

|

7 |

BSVによるメモリダンプモジュールの設計 |

|

上位モジュールの設計

1バイトの送信はうまく行ったようなので、上位モジュールMemoryDumpを設計します。概略仕様を以下に示します。

- 1ワードが4bitで構成されるメモリをダンプします。

- メモリのアドレス0からの内容を65536ワード送信します。

- 256行×256列で送信し、1行毎にチェックサムを送信します。

- 1バイトのバイナリは表示可能な2バイトのアスキーコードに変換します。

- 行末は改行します。

メモリ空間は64Kバイトあります。以下にアルゴリズムをC likeの疑似コードにより示します。

疑似コード

int x, y, address;

byte data, checksum, upper, lower;

address = 0;

for (y=0 to 255) {

checksum = 0;

for (x = 0 to 255) {

data = memory[address++];

checksum += data;

data += (data >= 10) ? (-10 + "a") : "0";

uart.load(data);

}

upper = (checksum >> 4) & 8'h0f;

upper += (upper >= 10) ? (-10 + "a") : "0";

uart.load(upper);

lower = checksum & 8'h0f;

lower += (lower >= 10) ? (-10 + "a") : "0";

uart.load(lower);

uart.load(LF);

}

|

6 |

BSVによるUARTの設計 (7) |

|

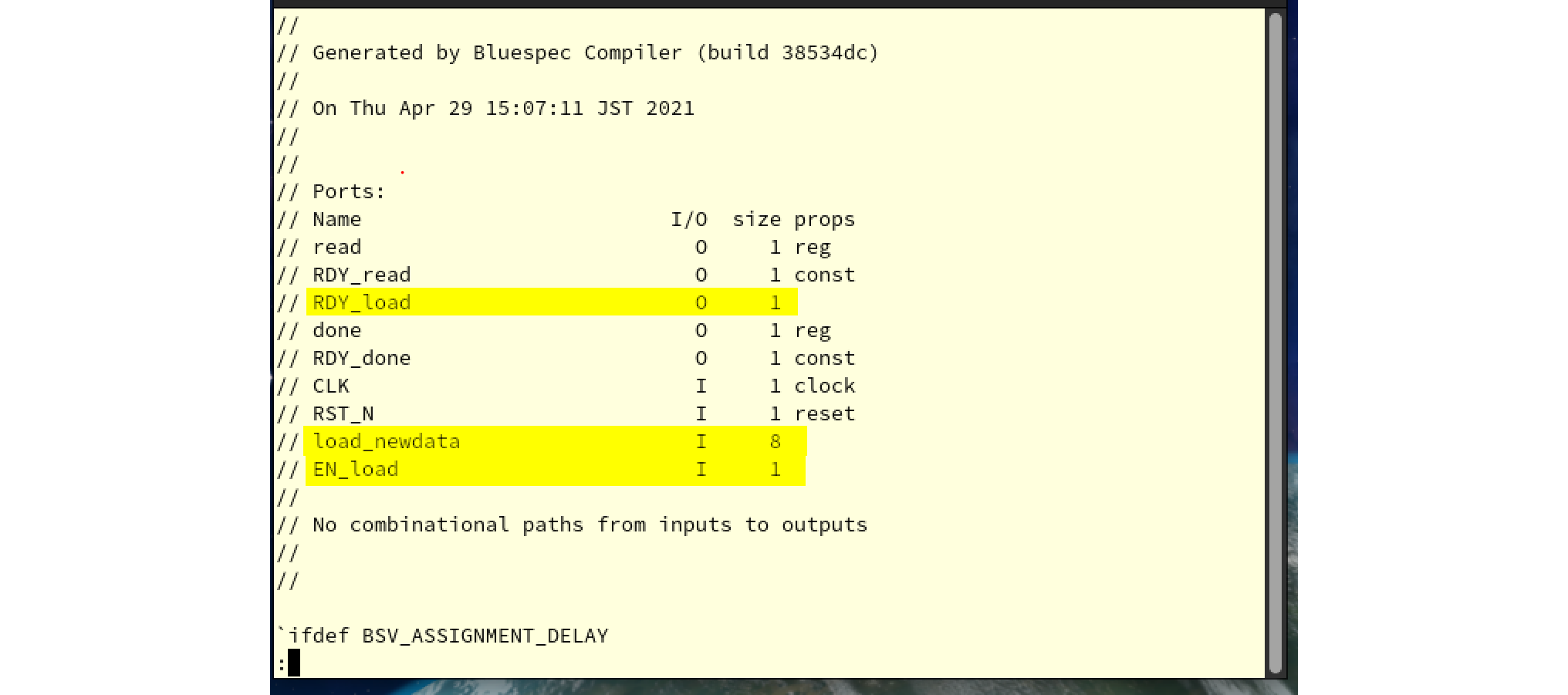

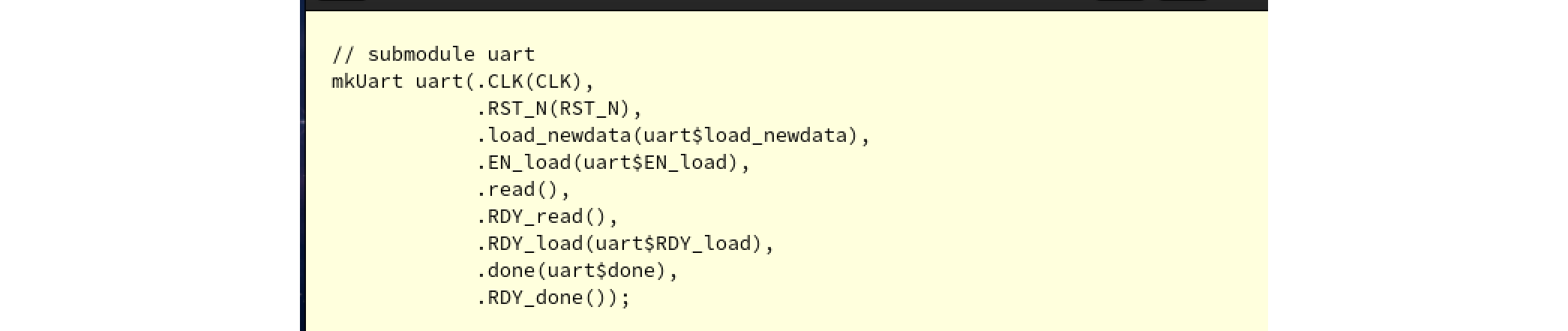

UARTのインタフェース

UARTのポート定義は次の図のようになります。

- データ: load_newdata (8bit, 入力)

- Ready: RDY_load (1bit, 出力)

- Enable: EN_load (1bit, 入力)

の3種があり、ReadyとEnableは自動生成されています。ここでReadyはモジュールの受信可能なタイミングを表し、一方EnableはテストベンチからのデータがValidであることを表します。

テストベンチでのモジュール呼び出しは次の図のようになります。

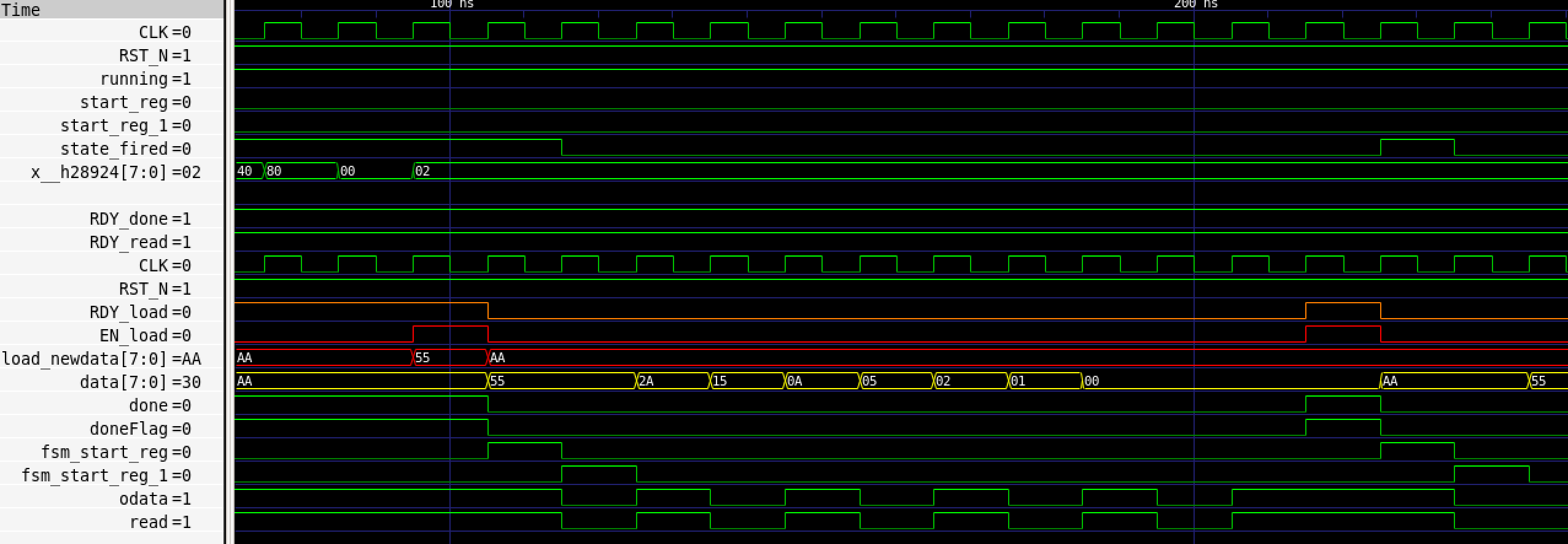

シミュレーション波形は次の図のようになります。

まずRDY_load(オレンジ)がアサートされて受信可能状態になっているとき、55H(赤)というデータが準備できた際にEN_load(赤)がアサートされます。すると次のサイクルで55H(黄)がUART内部に受け付けられ、同時にRDY_load(オレンジ)がネゲートされ、EN_load(赤)もネゲートされます。

テストベンチはすぐにRDY_load(オレンジ)のアサートを待っていますが通信時にはRDY_load(オレンジ)はネゲートされています。次にRDY_load(オレンジ)がアサートされた時点でEN_load(赤)を出力し同時にデータAAH(赤)を出力します。次のサイクルでデータAAH(黄)が受けつけられます。

このようなハンドシェークが自動的に、誤りなく生成されることもBSVの魅力です。

|

5 |

BSVによるUARTの設計 (6) |

|

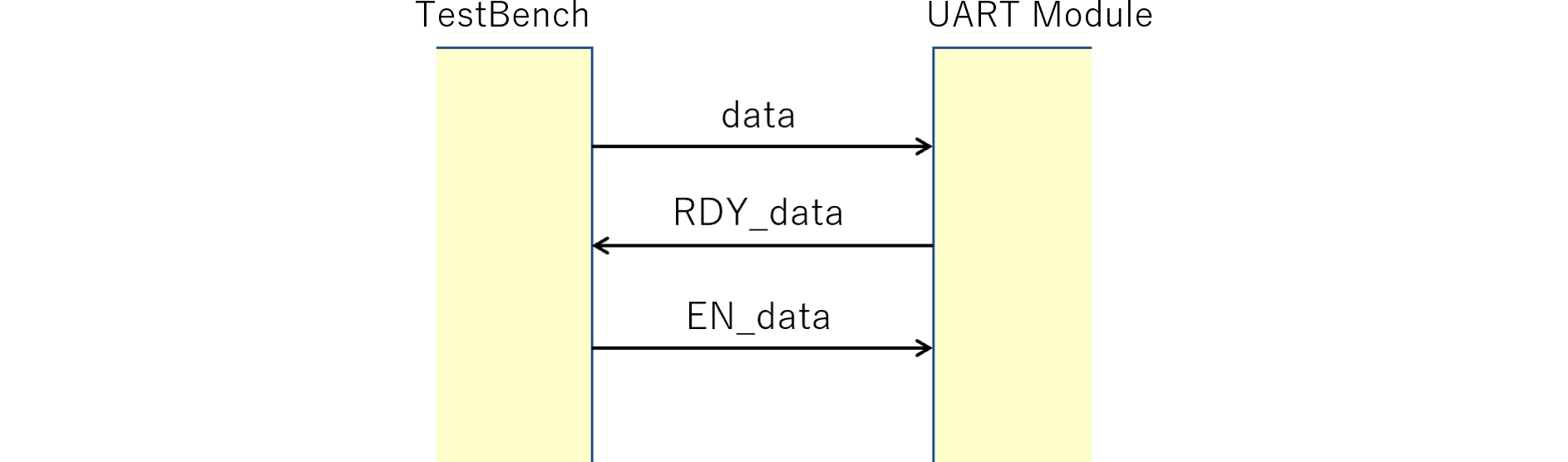

BSVによるインタフェース生成

BSVによるハンドシェークインタフェース信号の生成を細かく見ていきます。 注目するのは、テストベンチからUARTに与える8ビットデータとそのハンドシェーク信号です。記述はデータ(data)だけですが、ハンドシェーク信号(RDY_data, EN_data)が自動的に生成されます。その様子を図396.1に示します。左側がテストベンチで、右側がUARTモジュールです。

右側のモジュールから見た信号は以下のようになります。

- データ: data (8bit, 入力)

- Ready: RDY_data (1bit, 出力)

- Enable: EN_data (1bit, 入力)

ここでRDY_dataはモジュールの受信可能なタイミングを表し、一方EN_dataはテストベンチからのデータがValidであることを表します。

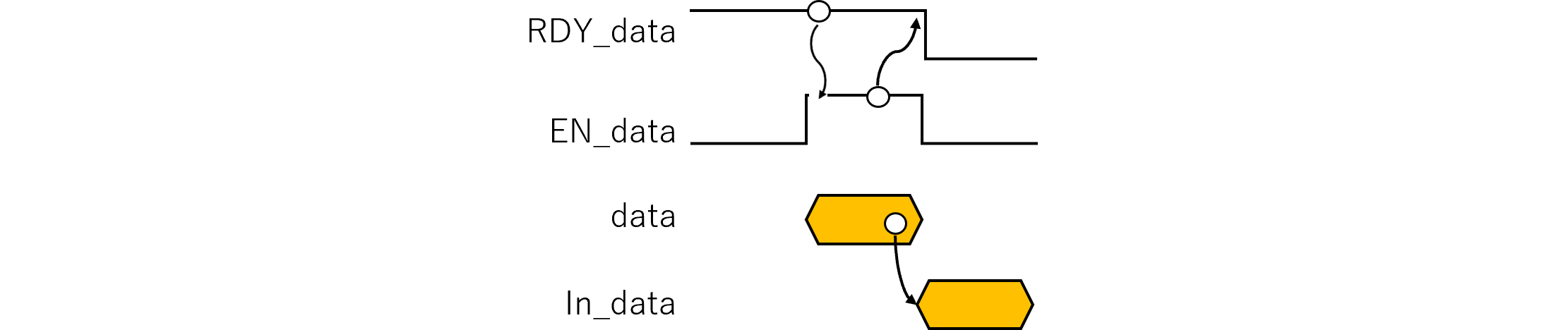

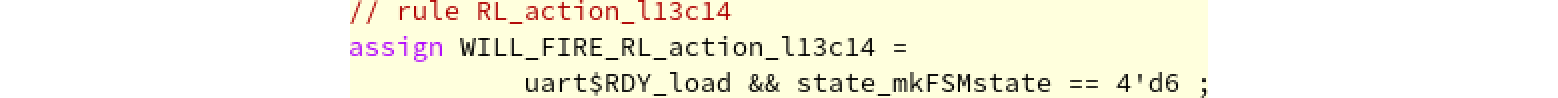

RDYの確認とENのアサートが同サイクルであることに注意します。通常のFF受けの設計だと、RDYを確認した次のサイクルからENのアサートになりそうですが、ENは次のようにRDYを含む組み合わせ回路により構成されています。そのため、ENはRDYと同タイミングでアサートされます。

ENはFF受けされるので、組み合わせ回路出力でヒゲが有っても良いという考えなのでしょうか。このほうがレイテンシが短縮されるため、上手な設計と言えます。

|

4 |

BSVによるUARTの設計 (5) |

|

Verilogシミュレーション

bscにより階層的にverilogファイルを生成し、iverilogによりverilogシミュレーションを行います。さらに波形を観測します。太字は入力文字を示します。

$ bsc -u -verilog Tb.bsv

checking package dependencies

compiling ./Uart.bsv

code generation for mkUart starts

Verilog file created: mkUart.v

compiling Tb.bsv

code generation for mkTb starts

Verilog file created: mkTb.v

All packages are up to date.

$ iverilog top.v mkTb.v mkUart.v -o mkTb

$ ./mkTb

VCD info: dumpfile mkTb.vcd opened for output.

$ gtkwave -A mkTb.vcd

GTKWave Analyzer v3.3.107 (w)1999-2020 BSI

[0] start time.

[630] end time.

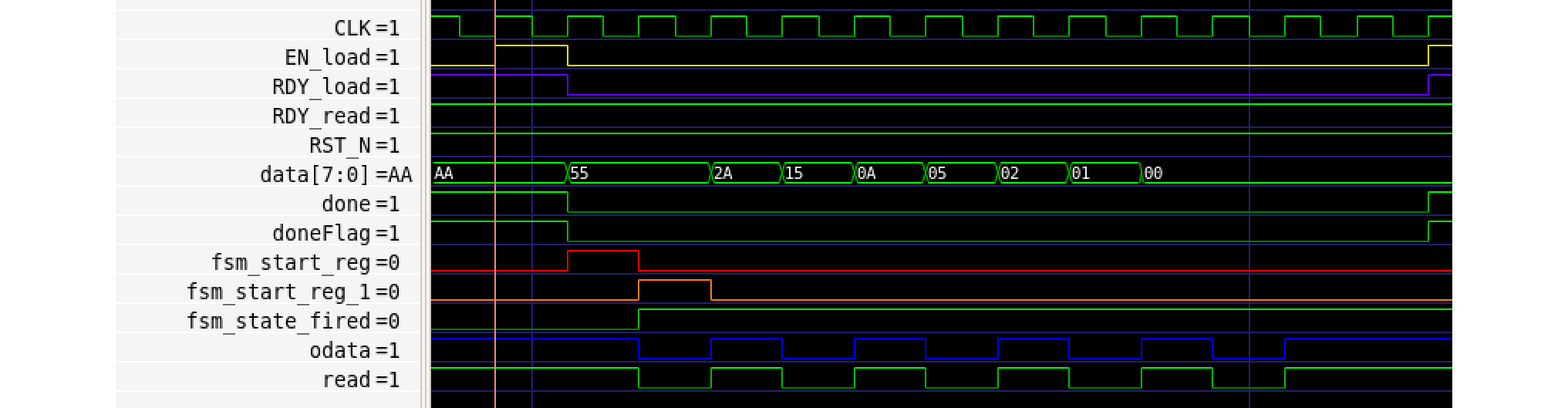

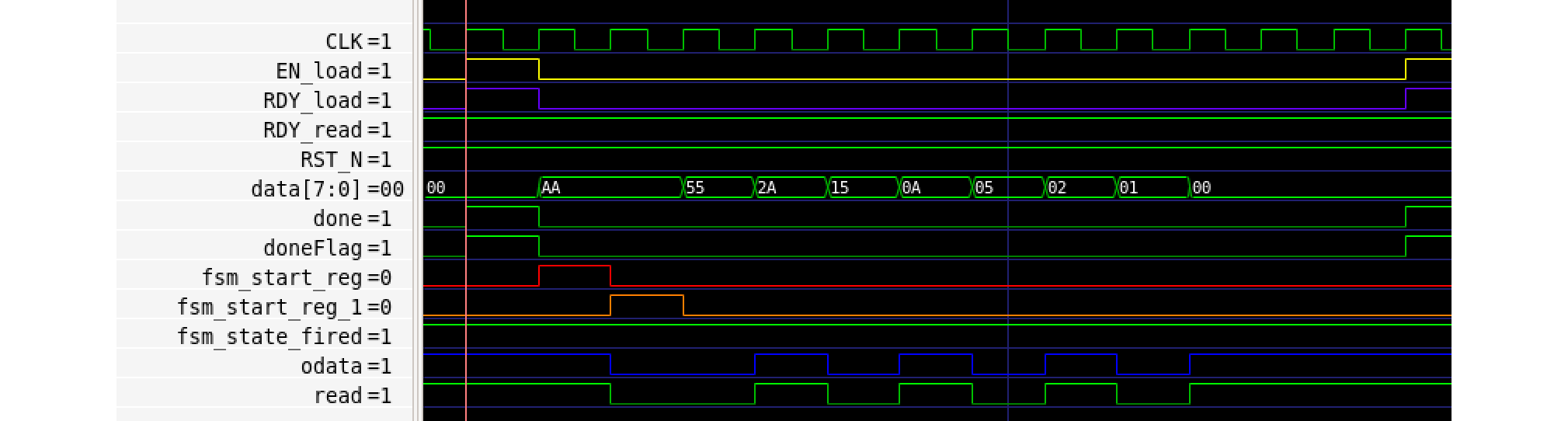

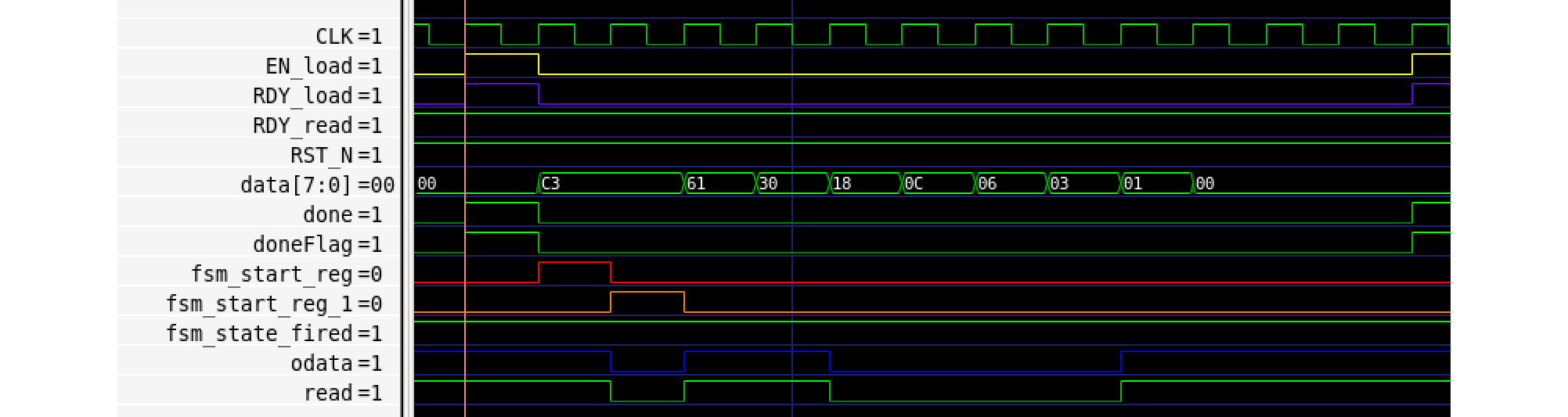

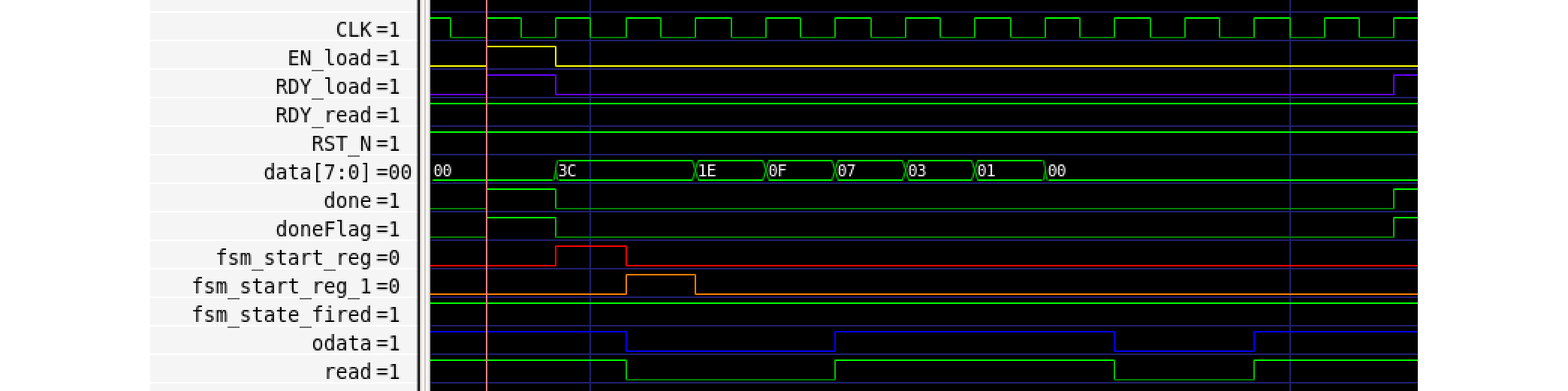

前記事に示すように、データ55H, AAH, C3H, 3CHを順に送信する場合の、モジュールの内部の波形です。

- 最初にデータがAAHになっていますが、BSVでは不定値をAAHで表しています。最初の送信データは55Hです。

- モジュールからRDY_load(青)がアサートされているので、テストベンチからデータが出力されると同時にEN_load(黄)がアサートされます。

- 次に内部レジスタdata(緑)が55Hに変化します。同時にdoneがネゲートされます。同時にFSMの開始レジスタfsm_start_reg(赤)がアサートされます。

- 次にfsm_start_reg_1(赤)がアサートされ、FSMが開始します。そのタイミングでodata(青)のスタートビット(=L)を出力します。

- 次にodata(青)の8bitをLSBから順に10101010と出力します。これはデータが55Hであるためです。

- 最後にストップビット(=H)を2bit出力します。

- 次にdone(緑)がアサートされ、同時にRDY_load(青)がアサートされます。

- 次の送信データはAAHです。

- 次にモジュールからRDY_load(青)がアサートされているので、テストベンチからデータが出力されると同時にEN_load(黄)がアサートされます。

- 次に内部レジスタdata(緑)がAAHに変化します。同時にdoneがネゲートされます。

- 次にFSMの開始レジスタfsm_start_reg(赤)がアサートされます。

- 次にfsm_start_reg_1(赤)がアサートされ、FSMが開始します。そのタイミングでodata(青)のスタートビット(=L)を出力します。

- 次にodata(青)の8bitをLSBから順に01010101と出力します。これはデータがAAHであるためです。

- 最後にストップビット(=H)を2bit出力します。

- 次にdone(緑)がアサートされ、同時にRDY_load(青)がアサートされます。

- 次の送信データはC3Hです。

- 次にモジュールからRDY_load(青)がアサートされているので、テストベンチからデータが出力されると同時にEN_load(黄)がアサートされます。

- 内部レジスタdata(緑)がC3Hに変化します。同時にdoneがネゲートされます。同時にFSMの開始レジスタfsm_start_reg(赤)がアサートされます。

- 次にfsm_start_reg_1(赤)がアサートされ、FSMが開始します。そのタイミングでodata(青)のスタートビット(=L)を出力します。

- 次にodata(青)の8bitをLSBから順に11000011と出力します。これはデータがC3Hであるためです。

- 最後にストップビット(=H)を2bit出力します。

- 次にdone(緑)がアサートされ、同時にRDY_load(青)がアサートされます。

- 次の送信データは3CHです。

- 次にモジュールからRDY_load(青)がアサートされているので、テストベンチからデータが出力されると同時にEN_load(黄)がアサートされます。

- 次に内部レジスタdata(緑)が3CHに変化します。同時にdoneがネゲートされます。同時にFSMの開始レジスタfsm_start_reg(赤)がアサートされます。

- 次にfsm_start_reg_1(赤)がアサートされ、FSMが開始します。そのタイミングでodata(青)のスタートビット(=L)を出力します。

- 次にodata(青)の8bitをLSBから順に00111100と出力します。これはデータが3CHであるためです。

- 最後にストップビット(=H)を2bit出力します。

- 次にdone(緑)がアサートされ、同時にRDY_load(青)がアサートされます。

- テストベンチはdoneを監視しているので、doneがアサートされると終了です。

|

3 |

BSVによるUARTの設計 (4) |

|

トップモジュールの修正

同様にC-c C-aを実行することにより、トップモジュールを修正します。クロックとリセットのレジスタが生成され、呼び出すモジュールのクロックとリセットにそれぞれ接続されます。以下にソースの変化点だけを示します。

top.v

`timescale 1ns/1ns

module top();

/*AUTOREGINPUT*/

// Beginning of automatic reg inputs (for undeclared instantiated-module inputs)

reg CLK; // To mkTb_inst of mkTb.v

reg RST_N; // To mkTb_inst of mkTb.v

// End of automatics

/*AUTOWIRE*/

mkTb mkTb_inst(/*AUTOINST*/

// Inputs

.CLK (CLK),

.RST_N (RST_N));

ページ: