|

6 |

BSVによるUARTの設計 (7) |

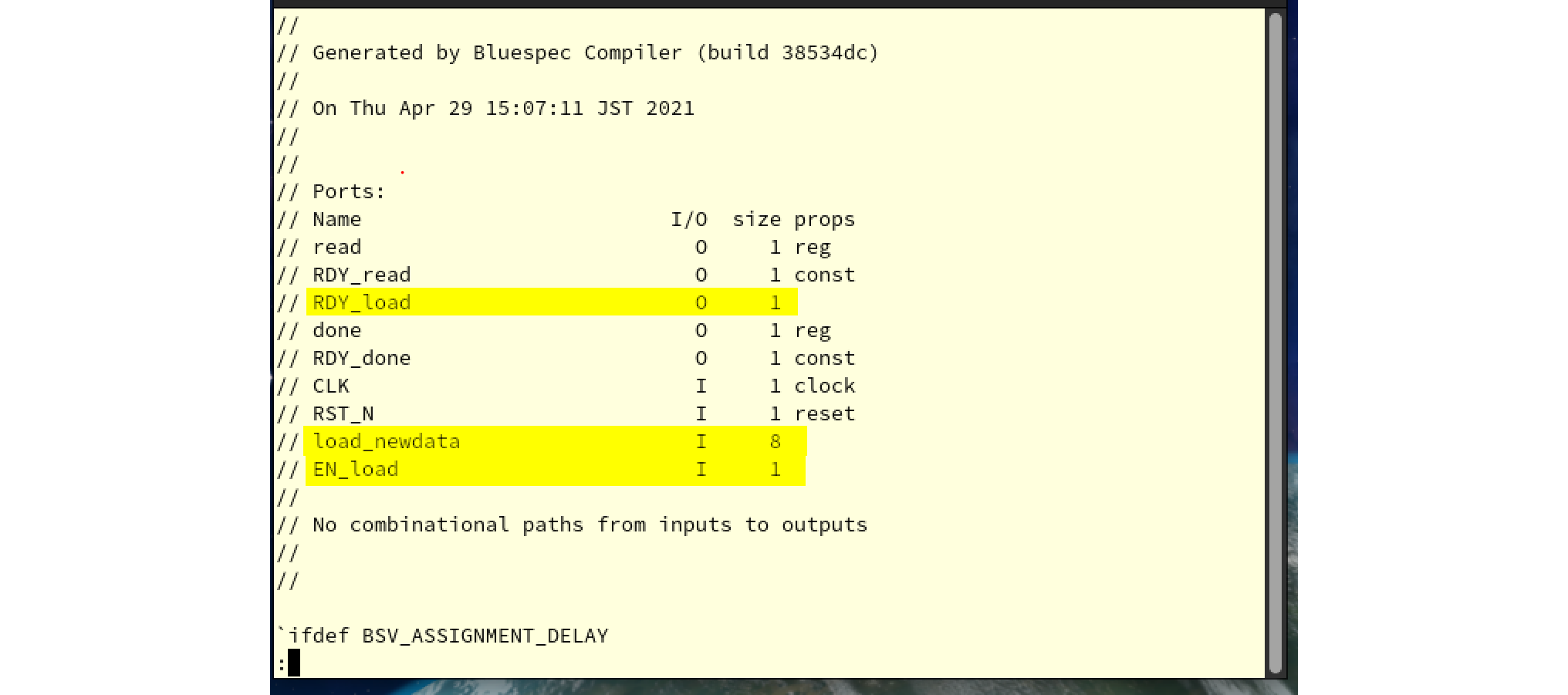

UARTのインタフェース

UARTのポート定義は次の図のようになります。

- データ: load_newdata (8bit, 入力)

- Ready: RDY_load (1bit, 出力)

- Enable: EN_load (1bit, 入力)

の3種があり、ReadyとEnableは自動生成されています。ここでReadyはモジュールの受信可能なタイミングを表し、一方EnableはテストベンチからのデータがValidであることを表します。

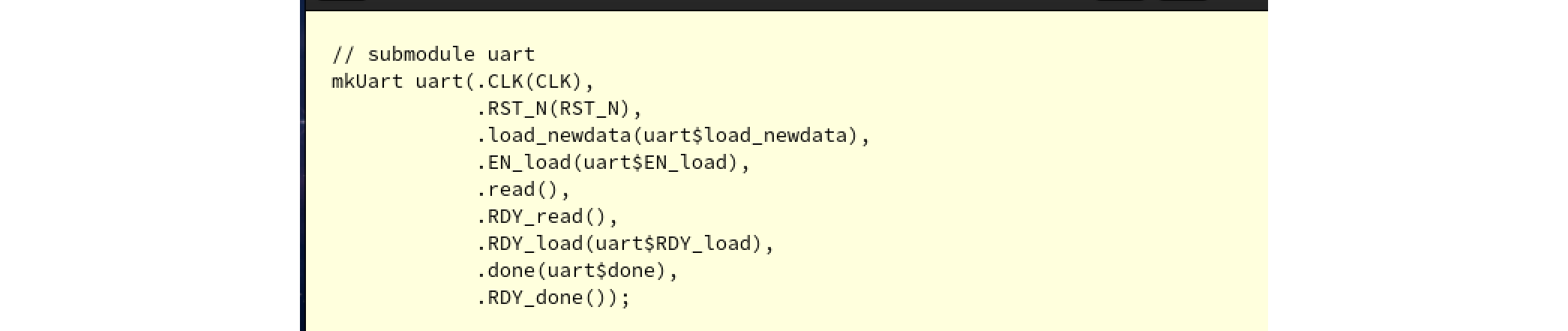

テストベンチでのモジュール呼び出しは次の図のようになります。

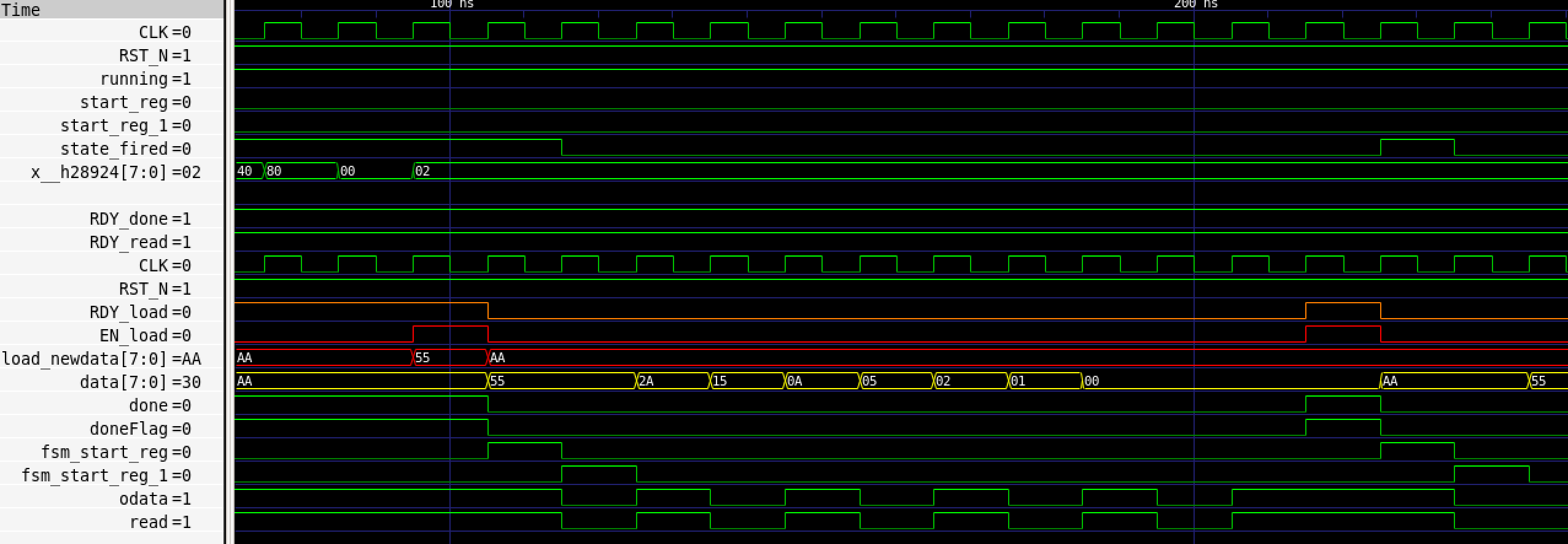

シミュレーション波形は次の図のようになります。

まずRDY_load(オレンジ)がアサートされて受信可能状態になっているとき、55H(赤)というデータが準備できた際にEN_load(赤)がアサートされます。すると次のサイクルで55H(黄)がUART内部に受け付けられ、同時にRDY_load(オレンジ)がネゲートされ、EN_load(赤)もネゲートされます。

テストベンチはすぐにRDY_load(オレンジ)のアサートを待っていますが通信時にはRDY_load(オレンジ)はネゲートされています。次にRDY_load(オレンジ)がアサートされた時点でEN_load(赤)を出力し同時にデータAAH(赤)を出力します。次のサイクルでデータAAH(黄)が受けつけられます。

このようなハンドシェークが自動的に、誤りなく生成されることもBSVの魅力です。

Leave a Comment