|

23 |

Pongと強化学習 (62) |

|

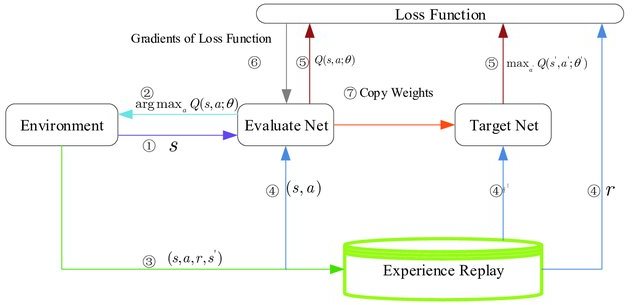

図867.1に基づき、リプレイメモリからの出力信号を聞いてみます。

リプレイメモリからの出力とそれぞれのコンポーネント(Q-network、Target Q-network、DQN損失)への入力に関して、具体的に明確化しましょう。

リプレイメモリからの出力と各コンポーネントへの入力

リプレイメモリに保存される経験は、タプル$(s, a, r, s', done)$の形式で、それぞれ現在の状態$s$、選択された行動$a$、得られた報酬$r$、次の状態$s'$、そしてエピソードが終了したかどうかを示すフラグ$done$を含みます。

Q-networkへの入力: Q-networkは現在の状態$s$と行動$a$を入力として受け取り、その組み合わせに対するQ値$Q(s, a; \theta)$を出力します。ここで、$\theta$はQ-networkのパラメータです。

Target Q-networkへの入力: Target Q-networkは次の状態$s'$を入力として受け取り、その状態におけるすべての可能な行動$a'$に対するQ値の最大値$\max_{a'} Q(s', a'; \theta^-)$を出力します。ここで、$\theta^-$はTarget Q-networkのパラメータです。

DQN損失の計算に使用される情報: DQN損失の計算には、現在の状態$s$と行動$a$に対するQ値$Q(s, a; \theta)$、次の状態$s'$における最大Q値$\max_{a'} Q(s', a'; \theta^-)$、即時報酬$r$、および終了フラグ$done$が使用されます。DQN損失は以下の式で表されます:

$$L(\theta) = \mathbb{E}\left[\left(r + \gamma \max_{a'} Q(s', a'; \theta^-) - Q(s, a; \theta)\right)^2\right]$$

ここで、$\gamma$は割引率です。$done$フラグがTrueの場合(つまり、エピソードが終了した場合)、次の状態における報酬は考慮されず、損失は$r - Q(s, a; \theta)$の差のみを基に計算されます。

このように、リプレイメモリからの出力は、Q-networkとTarget Q-networkの学習、およびDQN損失の計算において、異なる形で使用されます。このプロセスを通じて、エージェントは最適な行動ポリシーを学習し、パフォーマンスを向上させていきます。