|

1 |

BSV(Bluespec SystemVerilog) (6) |

|

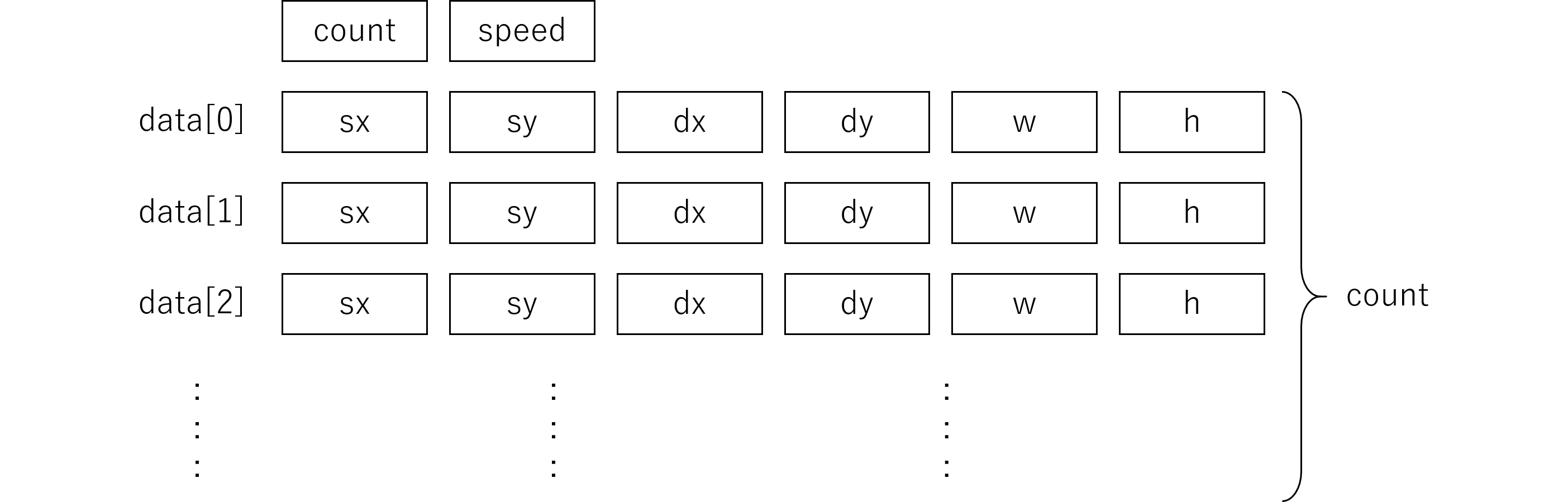

だいぶ前の記事ですが、テストベンチのBSVと、モジュールのBSVからVerilogを生成し、Verilogシミュレーションを実施しました。BSVではテストベンチにおいてクロックとリセットが自動生成され、暗黙的にモジュールに供給されます。一方、Verilogでは明示的にテストベンチにクロックとリセットを供給する必要があります。前の記事では、テストベンチ内にその処理を行う記述をインクルードする方法を用いました。

ここでは、最上位からそれらの信号を供給する手法をとります。これにより、よりスマートにVerilogシミュレーションが実行できます。まず、原始最上位ファイルを用意します。最上位からはテストベンチを呼び出しています。

最上位ファイル:mkTop.v

module mkTop () ;

/*AUTOREGINPUT*/

mkTb Tb_inst(/*AUTOINST*/);

initial begin

RST_N = 1'b0;

#30;

RST_N = 1'b1;

end

initial begin

CLK = 1'b0;

forever begin

#5 CLK = ~CLK;

end

end

endmodule // mkTop

これに対して、Verilog-modeのオートコネクションコマンドであるC-c C-aを用いてポートの追加を行えば、

最上位ファイル:mkTop.v

module mkTop () ;

/*AUTOREGINPUT*/

// Beginning of automatic reg inputs (for undeclared instantiated-module inputs)

reg CLK; // To Tb_inst of mkTb.v

reg RST_N; // To Tb_inst of mkTb.v

// End of automatics

mkTb Tb_inst(/*AUTOINST*/

// Inputs

.CLK (CLK),

.RST_N (RST_N));

initial begin

RST_N = 1'b0;

#30;

RST_N = 1'b1;

end

initial begin

CLK = 1'b0;

forever begin

#5 CLK = ~CLK;

end

end

endmodule // mkTop

のように、テストベンチに対してクロックとリセットが接続されます。

最上位、テストベンチ、モジュールを結合した実行ファイルを生成します。エラーが出ることもなく実行ファイルが生成され、実行ファイルによりVerilogシミュレーションを実行すれば、

$ iverilog mkTop.v mkTb.v mkFibOne.v -o mkFibOne.exev

$ ./mkFibOne.exev

1

1

2

3

5

8

13

21

34

55

89

144

233

377

610

987

1597

2584

4181

6765

10946

このように、正しくVerilogシミュレーションが行われ、前記事と同じ結果となります。

結論としては、この記事のように自動結合を使用すれば、前記事のようにincludeを埋め込む必要はありませんでした。

追記:bscによりverilogをリンクし+bscvcd=verilog.vcdとフラグをつけることでvcdダンプができることがわかりました。これを使えばmkTop.vもiverilogも不要となります。