|

18 |

デザインのボード間移植 |

ArtyボードからUltra96ボードへ

RTLにはボード依存性はありませんが、トップモジュールやIPにはボード依存性があるため、その移植が必要となります。まずトップ配線(ブロック間配線)は、Export Block Designにより、配線情報がTCLにより得られるので、それを入力したいところです。しかし、ボード依存性があるようで、新ボードを設定した上で旧ボードのTCLを読み込むとエラーになってしまいます。そのため、

- 旧ボードの環境でデザインを構築しておき、新規ボードに変換する

方法により、デザインのボード間移植を実施しました。

新規プロジェクトの生成

最初に旧ボードでプロジェクトを生成します。この段階で必要なものはVerilogソースが全て含まれているsrcディレクトリ、ブロックデザインのTCL、新ボードのXDCのひな形です。

- Vivadoの下にプロジェクトフォルダを作成します。その下に、Verilogソースが全て含まれているsrcディレクトリ、ブロックデザインのtcl及び、xdcを配置します。

- Vivadoを起動し、Create Project⇒Next⇒RTLプロジェクトを選択し、Verilogソースフォルダを選択します。

- 次にconstraintファイルとしてxdcを設定します。

- Boardsとして旧ボードを選択します。

- FinishによりProjectが生成されます。

- IP Integrator⇒Create Block Designを実行します。

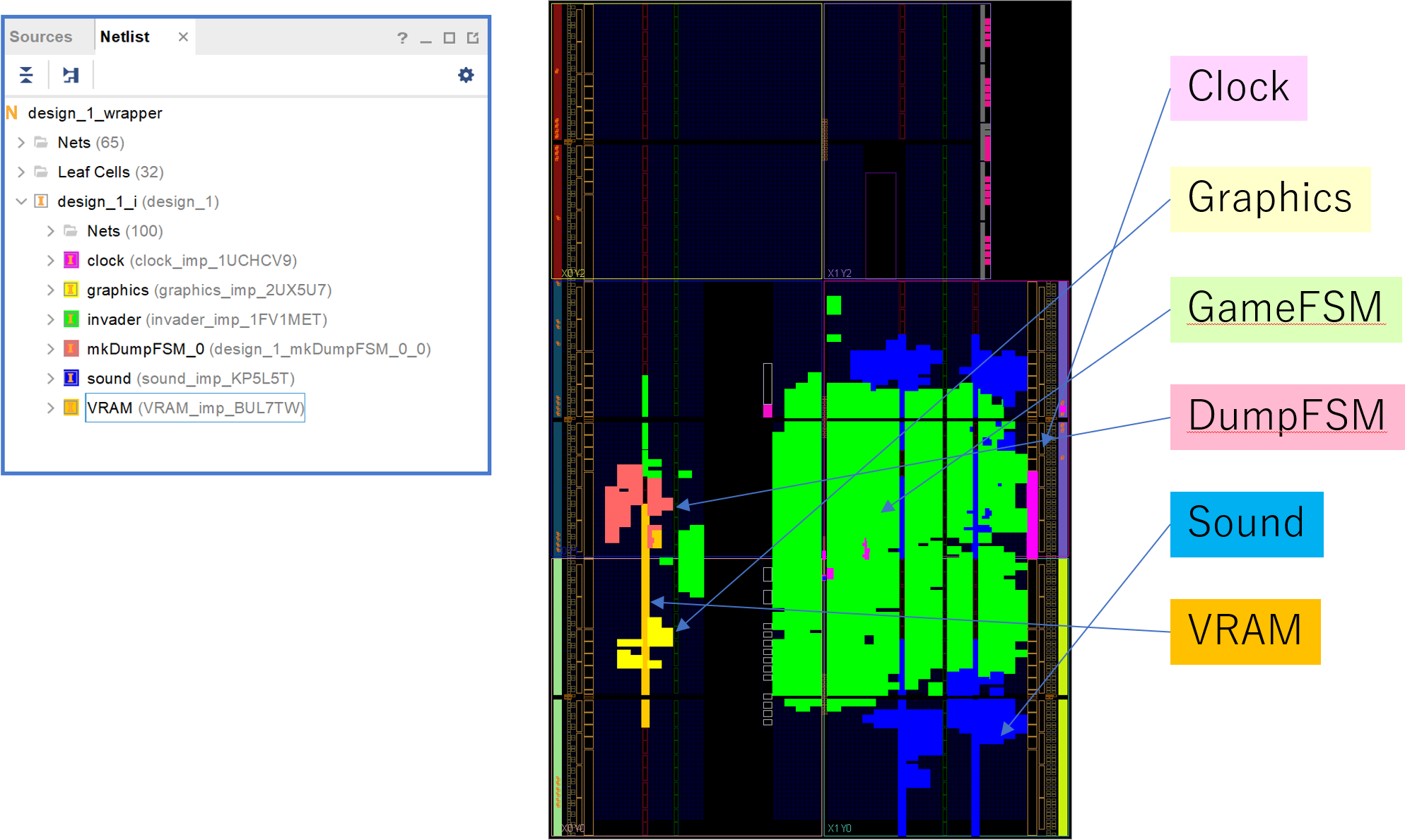

- BLOCK DESIGN⇒Sources⇒Design sourcesのトップデザインであるdesin_1に対してラッパを生成します。

- design_1を選択して右クリックでCreate HDL wrapperを実行するとダイアログが現れます。

- Let Vivado ...を選択してOKをクリックします。

- オレンジの階層だったものが、design_1_wapperというグリーンの階層が生成されます。

- それを右クリックし、Set as topにより、トップ階層とします。

- 最下段のTCL Console内で、source C:/Users/<ユーザ名>/Vivado/<プロジェクト名>/design_1.tclを実行します。

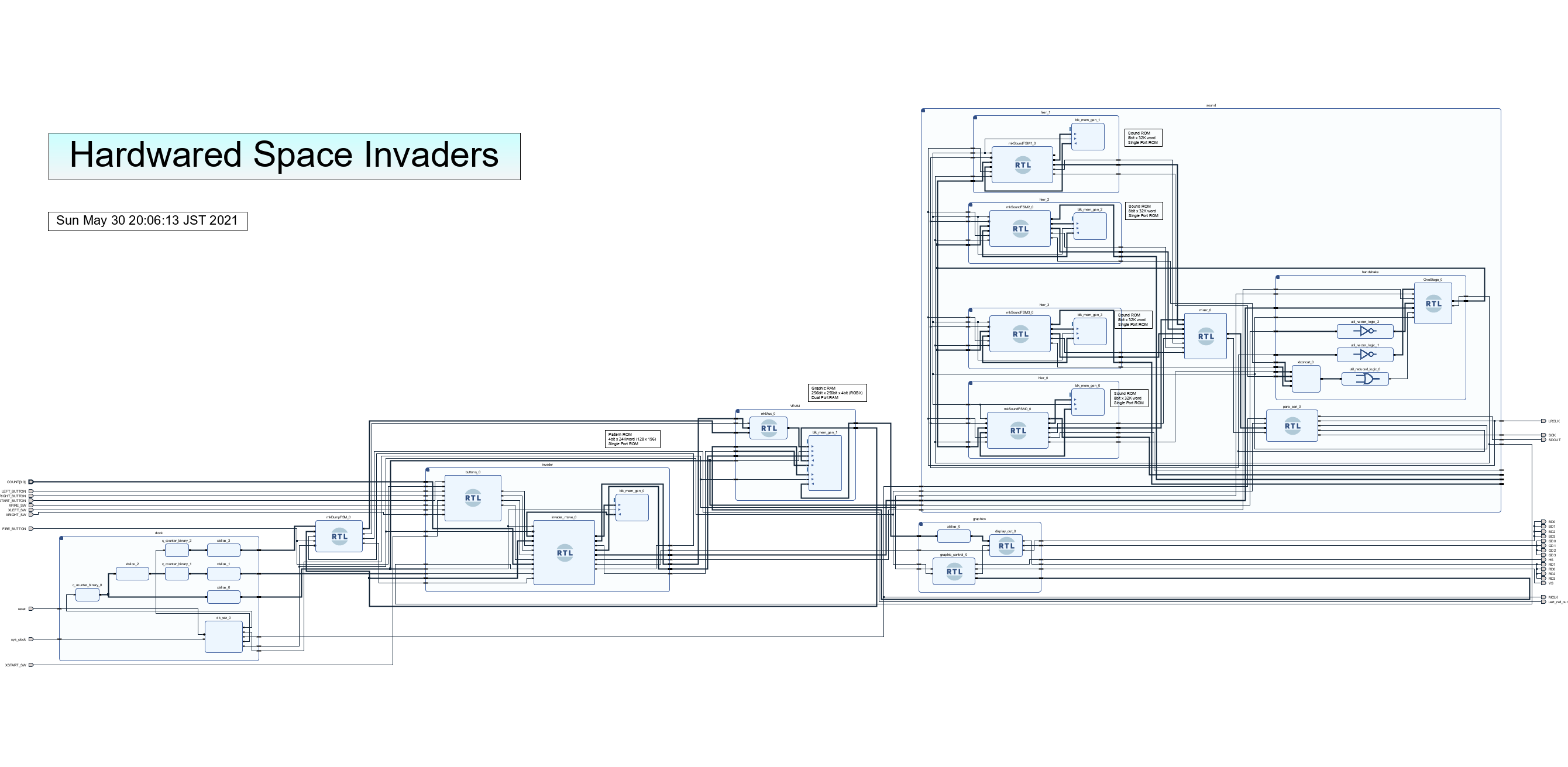

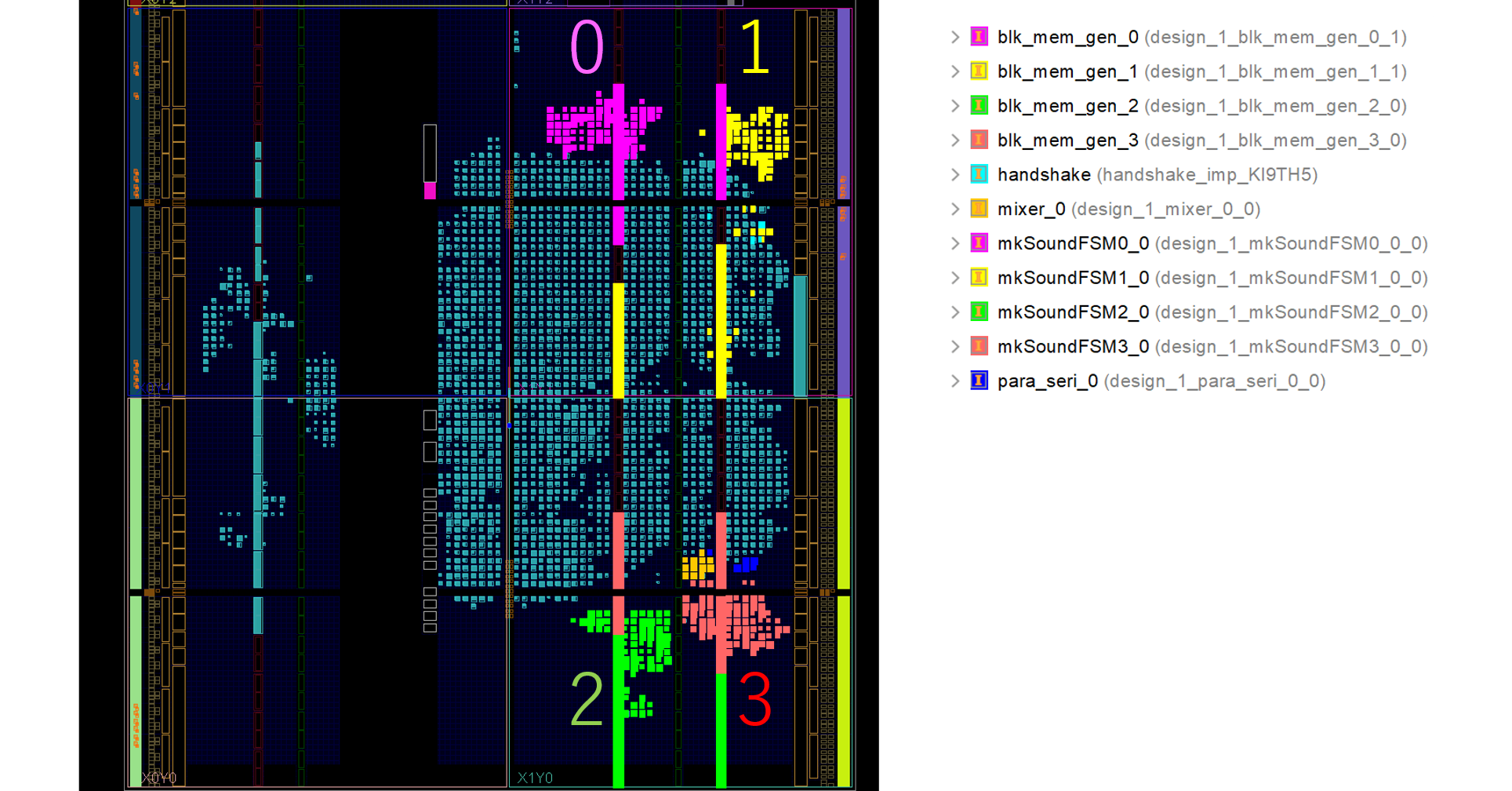

- ブロックが配置され、ブロック間に配線されます。Diagramを右クリックしてExpand Allし、Regenerate Layoutをクリックします。

- タイトルコメントのText sizeを64、Box fill colorを204,255,255とします。

新ボードへ移行

- ボードが旧ボードになっているので、PROJECT MANAGER⇒Settingsでダイアログを立ち上げ、Project Settings⇒General⇒Project device:によりボードを新ボードに変更します。

- BLOCK DESIGNに、IPのアップグレードを促す指示が出るため、個数をクリックします。Show IP Statusをクリックします。

- 最下段のUpgrade SelectedをクリックしIPのアップグレードを実施します。

- IPによっては結線が外れていることがあるため、良く見直して、外れていれば接続しなおします。

注意点

coeファイルは相対ディレクトリで記録されますが、tclスクリプトからうまく参照できないようなので、全て絶対ディレクトリ(例:e:\file.coe)として参照できるようにしました。