|

2 |

ソフトブロック解説 |

ソフトブロック解説

ここから、簡単に各ソフトブロック階層の解説をします。全体ブロック図は過去記事に挙げてあります。全体ブロック図において、左から順に、clock階層、メモリダンプモジュール(ソフトブロック階層無し)、invader階層、VRAM階層、graphics階層、sound階層となっています。

clock階層

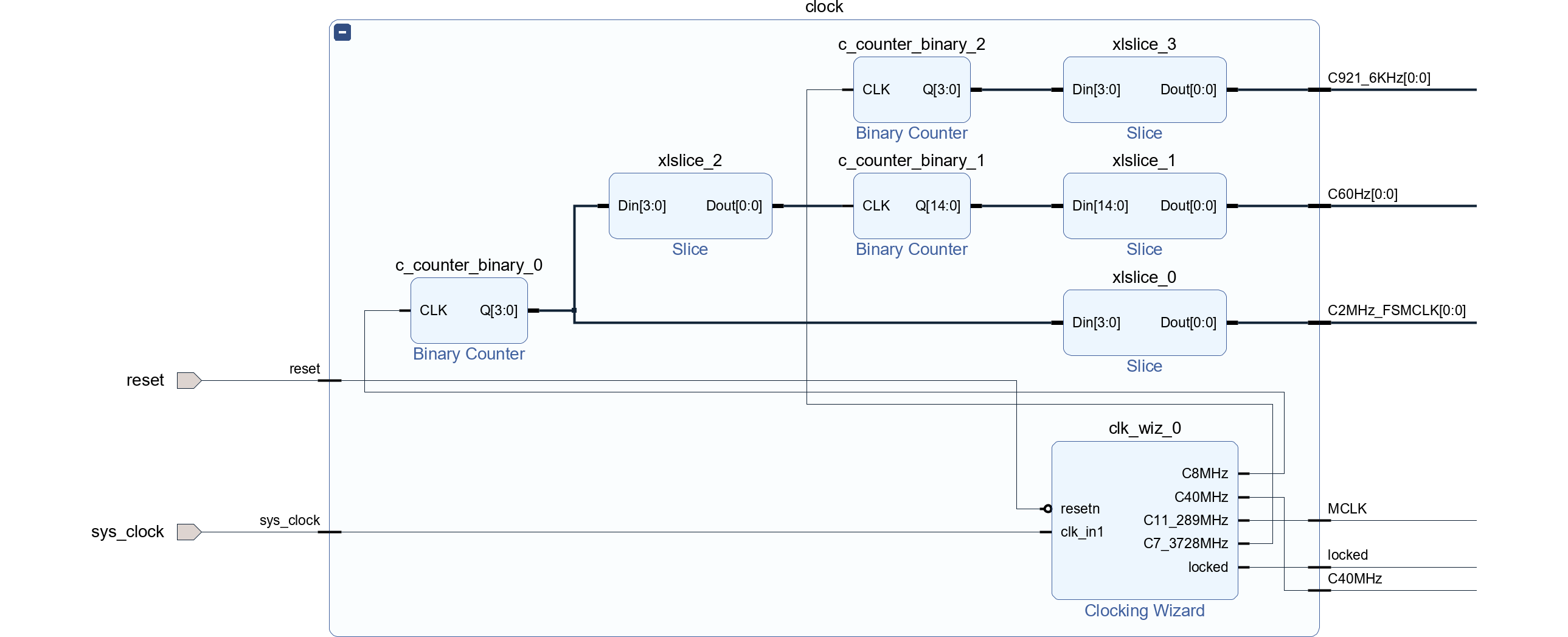

図411.1にclock階層の構造を示します。使用されているモジュールは全てXilinx IPです。

- sys_clock --- 100MHzクロック

- reset --- 負論理リセット

の2本です。出力は、

- C921_6KHz --- 921.6KHzクロックであり、UARTのボーレートクロック

- C60Hz --- 60Hzクロックであり、動画の1フレーム(tick)を決める基準クロック

- C2MHz_FSMCLK --- 文字通り2MHzのFSMクロック

- MCLK --- 11.289MHzクロックであり、サウンド用のマスタークロック

- C40MHz --- 40MHzクロックであり、グラフィックのドットクロック

- locked --- 負論理のリセット信号

バイナリカウンタ説明

- c_counter_binary_0 --- clk_wizからの8MHzクロックを入力し、bit0(4MHz)、bit1(2MHz)、bit2(1MHz)と分周する。xslice_0はそのbit1(2MHz)を取り出し、C2MHz_FSMCLKとして出力する。

- c_counter_binary_1 --- c_counter_binary_0からxslice_2はそのbit2(1MHz)を取り出し、c_counter_binary_1で0x411a(=16666)を計数したらリセットする。xslice_1ではその14bit(16.667msec=59.9988Hz)を取り出し、C60Hzとして出力する。これはデューティは50%ではないが、エッジを見るため問題ない。

- c_counter_binary_2 --- clk_wizからの7.3728MHzクロックを入力し、bit0(3.6864MHz)、bit1(1.8432MHz), bit2(921.6KHz)と分周する。xslice_3はそのbit2(921.6KHz)を取り出しC921_6KHzとして出力する。

スライス値

- xslice_0 --- 4,1,1,1

- xslice_1 --- 15,14,14,1

- xslice_2 --- 4,2,2,1

- xslice_3 --- 4,2,2,1

Leave a Comment