|

12 |

RISC-Vプロセッサの設計 (15) |

2段FIFOの検討(2)

今までENQとDEQを別々に検討しましたが、次にENQとDEQが同時にアサートされる場合を考えます。 ここで思い出すのが図562.1であり、あるサイクルにおいてENQとDEQが同時とは、サイクルの最初でDEQを行い、サイクルの最後でENQを行うということであり、DEQ⇒ENQの順序が重要です。従って、1サイクル中にENQを行ったデータをDEQすることはできません。これができるのはBypassFIFOという特殊なFIFOを用いた時に限られるようです。

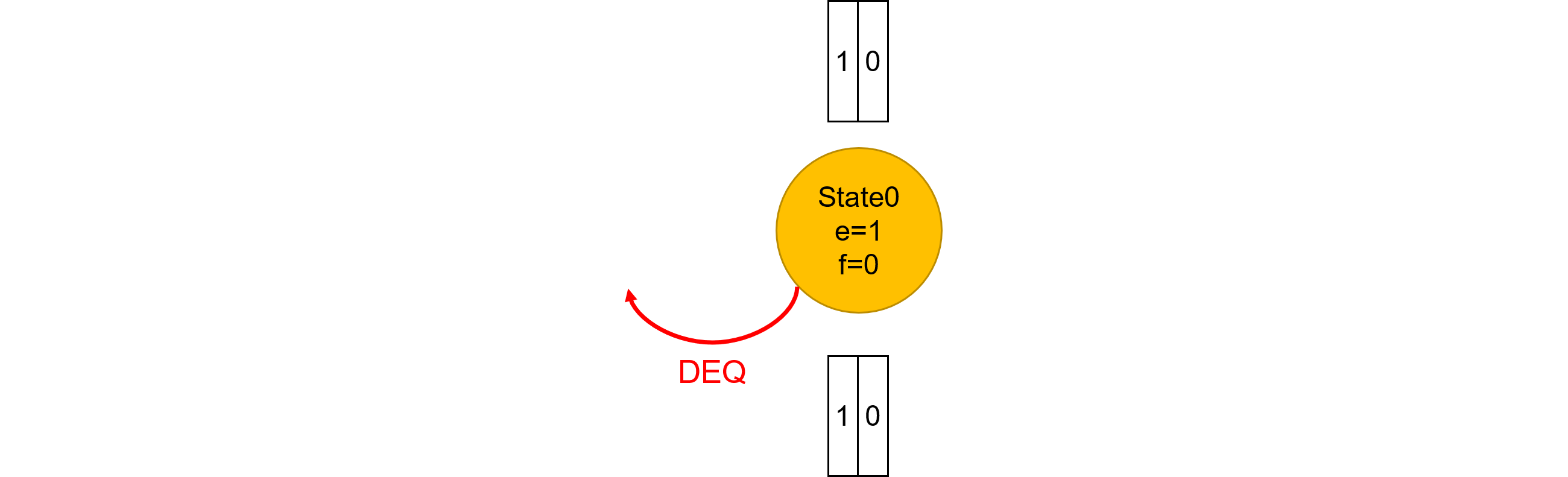

この原則を守れば、State0ではENQ/DEQの同時実行を考える必要は無くなります。State0でまずDEQをするのでエラーとなるからです。

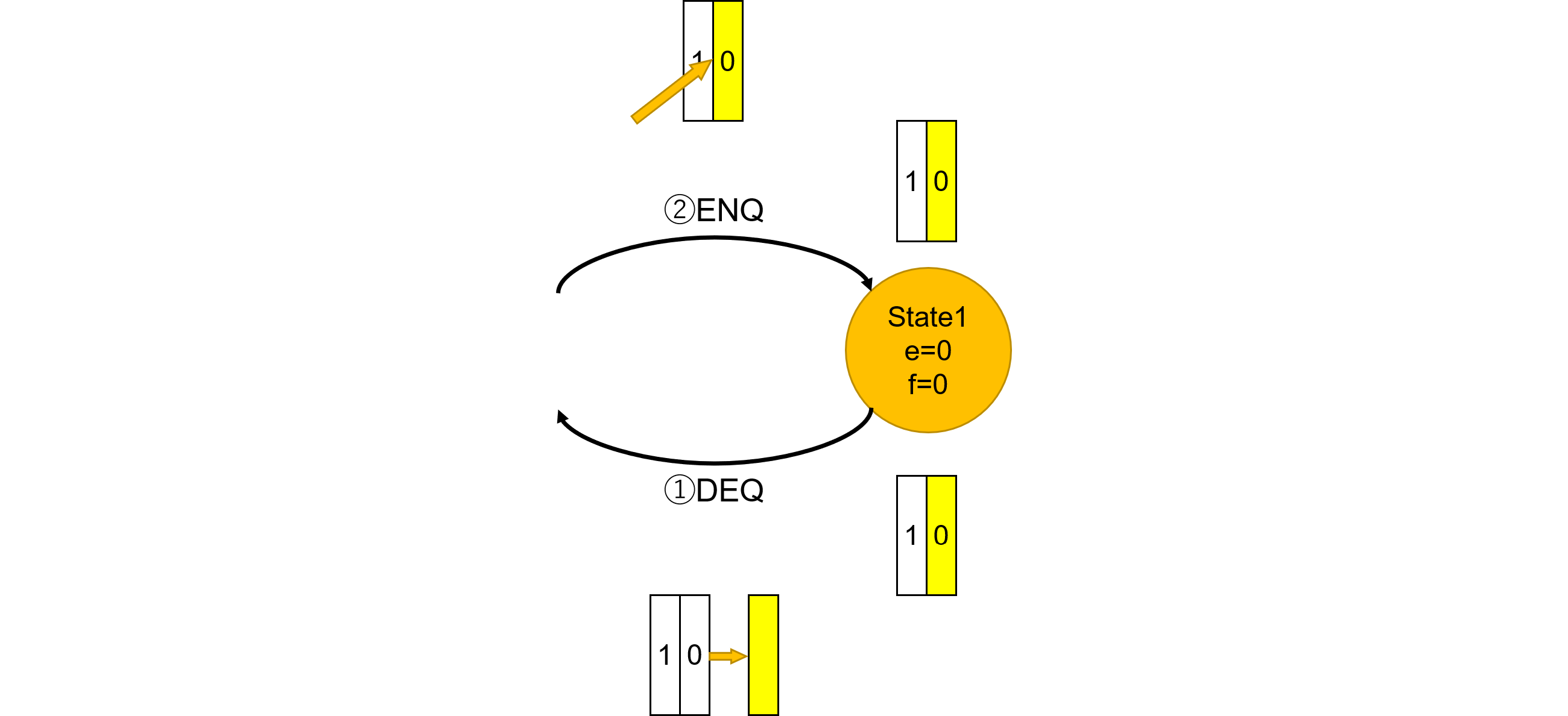

次にState1ではまずDEQを実行し、d0のデータを外に移します。本来はd0は無効化されますが、続いて外からENQされるので有効のままです。最終的にState1にとどまります。

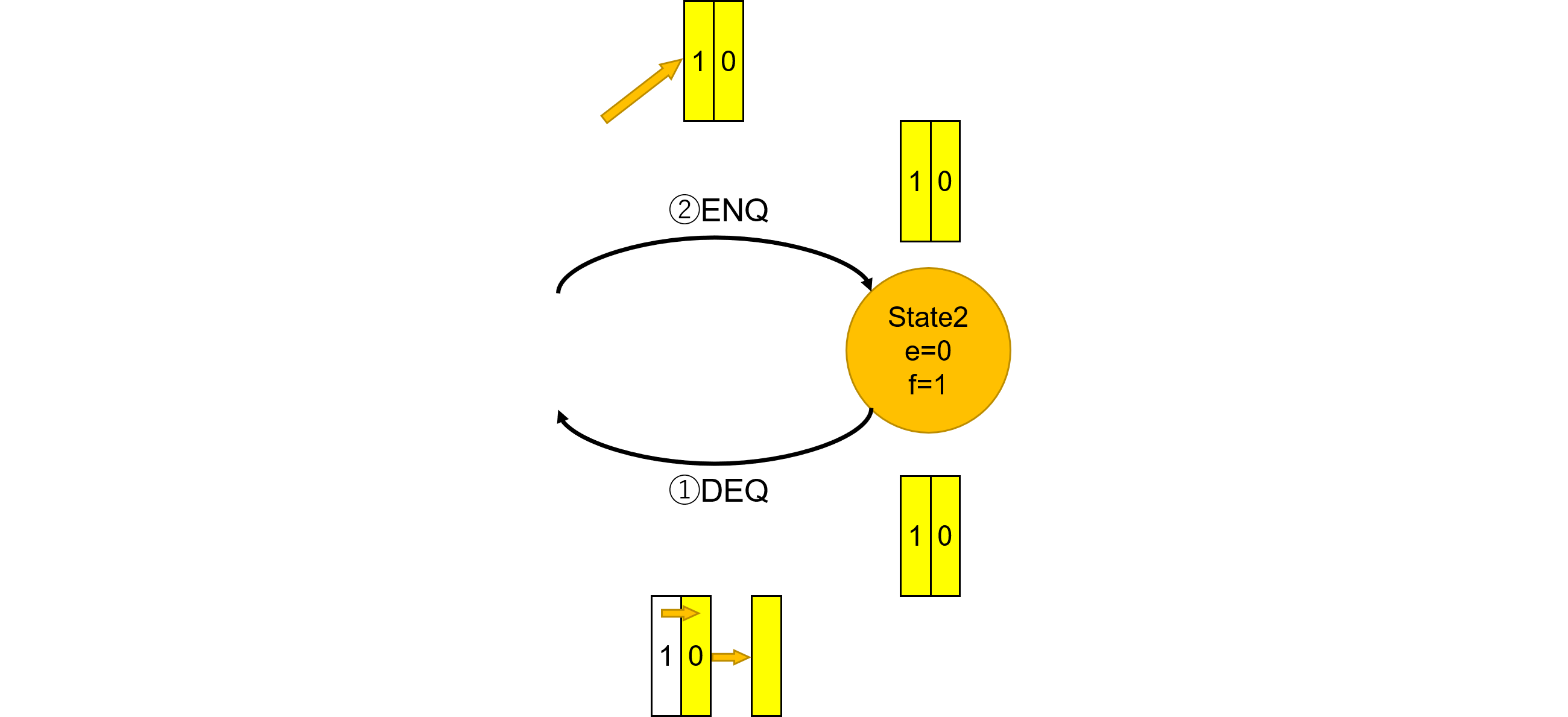

最後にState2ではまずDEQを実行し、d0のデータを外に移します。同時にd1のデータをd0に移します。同様にd0は無効化されず、続いて外からENQされるので有効のままです。最終的にState2にとどまります。