|

8 |

RISC-Vプロセッサの設計 (13) |

1段FIFOのシミュレーション

本来はFIFOは1段で良いはずですが、なぜ2段となっているのでしょうか?ここだけ見ると物量が倍になってしまいます。たいした物量ではないものの、1段で済ませないかを検討します。

前述のように、bscが出力するシミュレーションモデルではFIFO2という2段FIFOを使用しています。このモデルを1段FIFOに入れ替えたいのですが、bsimモデルは触ることができないので、verilogモデルのほうを修正します。上位において次のようにFIFO2を呼び出しているところをテキストエディタでFIFO1に修正します。

// submodule exs

FIFO2 #(.width(32'd32), .guarded(32'd1)) exs(.RST(RST_N),

.CLK(CLK),

.D_IN(exs$D_IN),

.ENQ(exs$ENQ),

.DEQ(exs$DEQ),

.CLR(exs$CLR),

.D_OUT(exs$D_OUT),

.FULL_N(exs$FULL_N),

.EMPTY_N(exs$EMPTY_N));

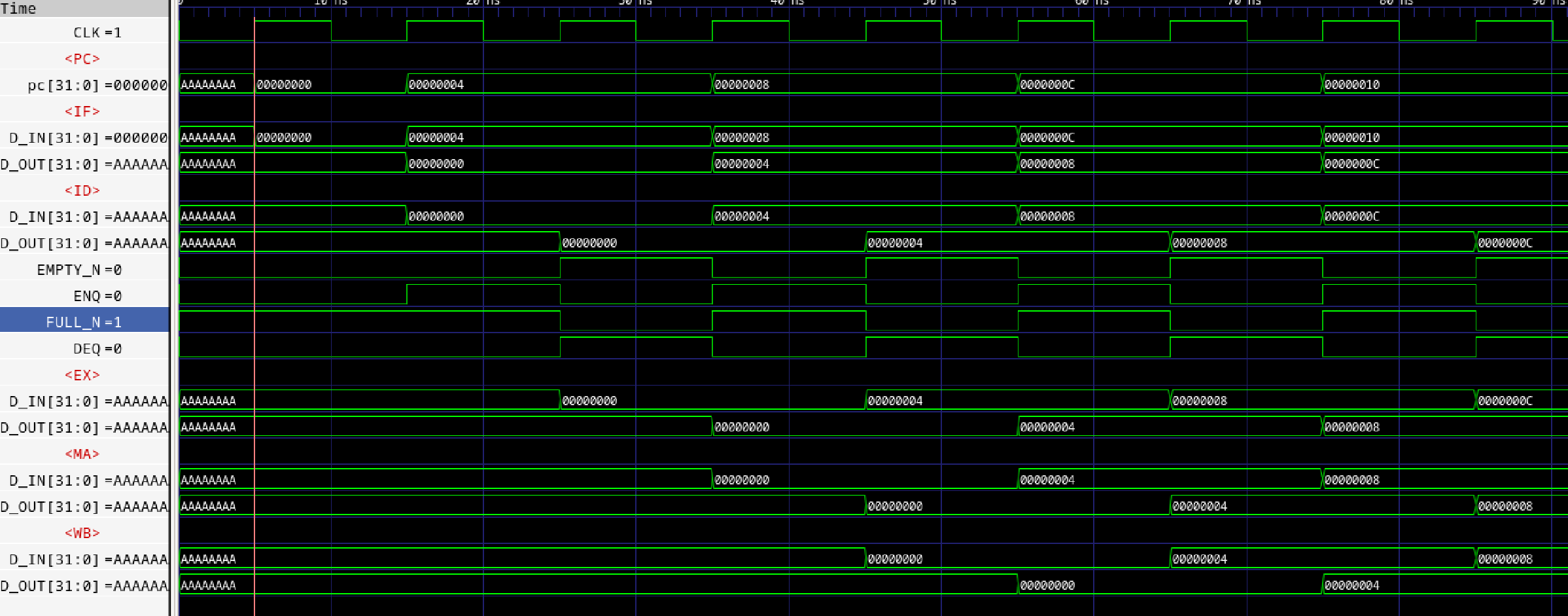

次にverilogシミュレーションを行うと、以下のような波形が得られます。

1ステージのレイテンシが2サイクルとなってしまいます。

これは、emtpyやfullは1サイクルおきにアサートされ、そのため2サイクルに1度しかキューに投入できないためです。従ってスループットが半分、レイテンシが倍になってしまいます。FIFOの動作上、空でないと上位からは詰められず、一方で詰まってないと下位からは引き取れないので、交互動作になるのは当然です。

通常のパイプラインはエンキューとデキューが同時に行えるので、これは改善できるかもしれません。