|

16 |

Part 5 Annex FのPMHF式 |

Annex F

ISO 26262-5:2018、すなわち規格Part 5のAnnex Fには「4.2に従った第9節の目的を満足するという論理的根拠の例」が掲載されています。

ここで、4.2とはPart 5の一般的な要件であり第9節とはランダムハードウエア故障による安全目標侵害の評価です。つまりPart 5の第9節の要請に従ったメトリクス評価の実例が書かれています。ここでメトリクスとはランダムハードウエア故障による安全目標侵害のメトリクスであり、PMHFを指します。

もっとも第9節では第1の手法として「ランダムハードウエア故障の確率的メトリック」すなわちPMHFの要件を挙げ、第2の手法として「安全目標侵害の各原因の評価」すなわちEECを挙げていて、メトリクスはいずれかとなりますが、第2の手法には弊社は疑念があるため、第1の手法であるPMHFを採用したほうが良いと考えます。

PMHF式

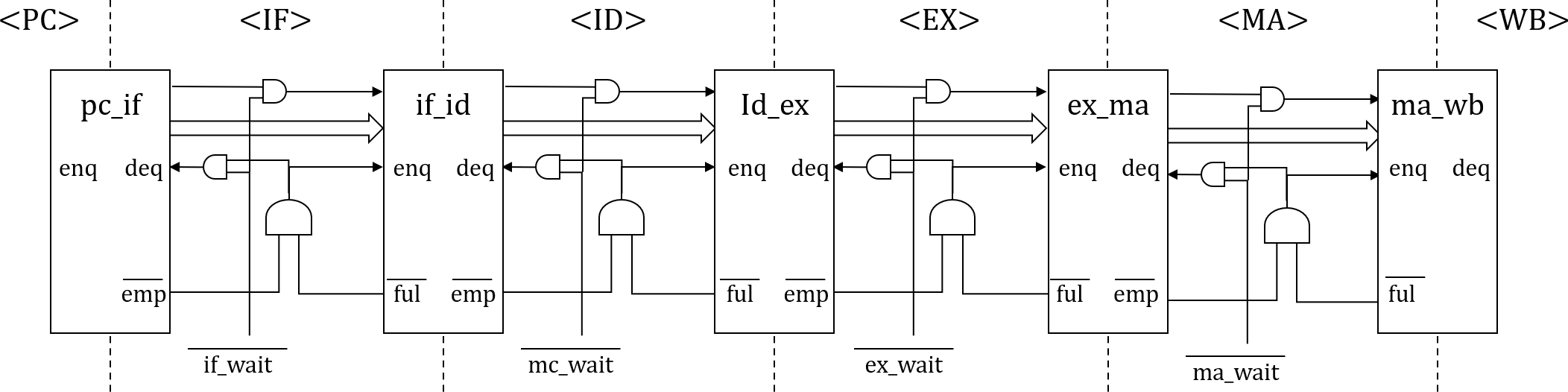

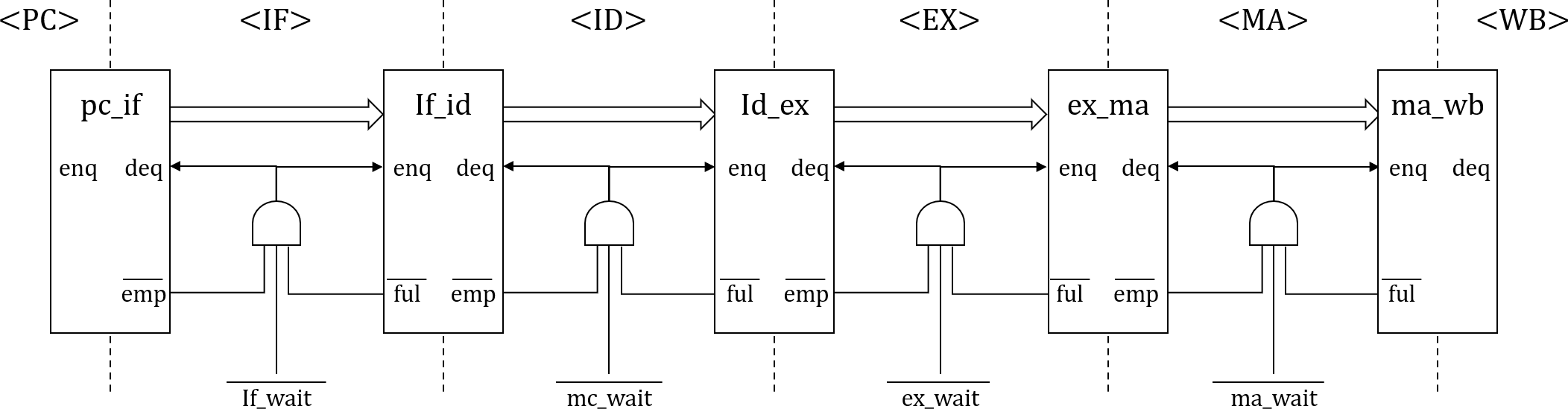

出発点はAnnex Eで実施したFMEDAによるSPFM/LFMの導出の表です。この例に基づき、Annex FではPMHFの簡易評価式を次のように定めています。

$$M_\text{PMHF,est}\equiv \lambda_\text{SPF}+\lambda_\text{RF}+\lambda_\text{DPF_det}\cdot\lambda_\text{DPF_latent}\cdot T_\text{Lifetime}\tag{678.1}$$

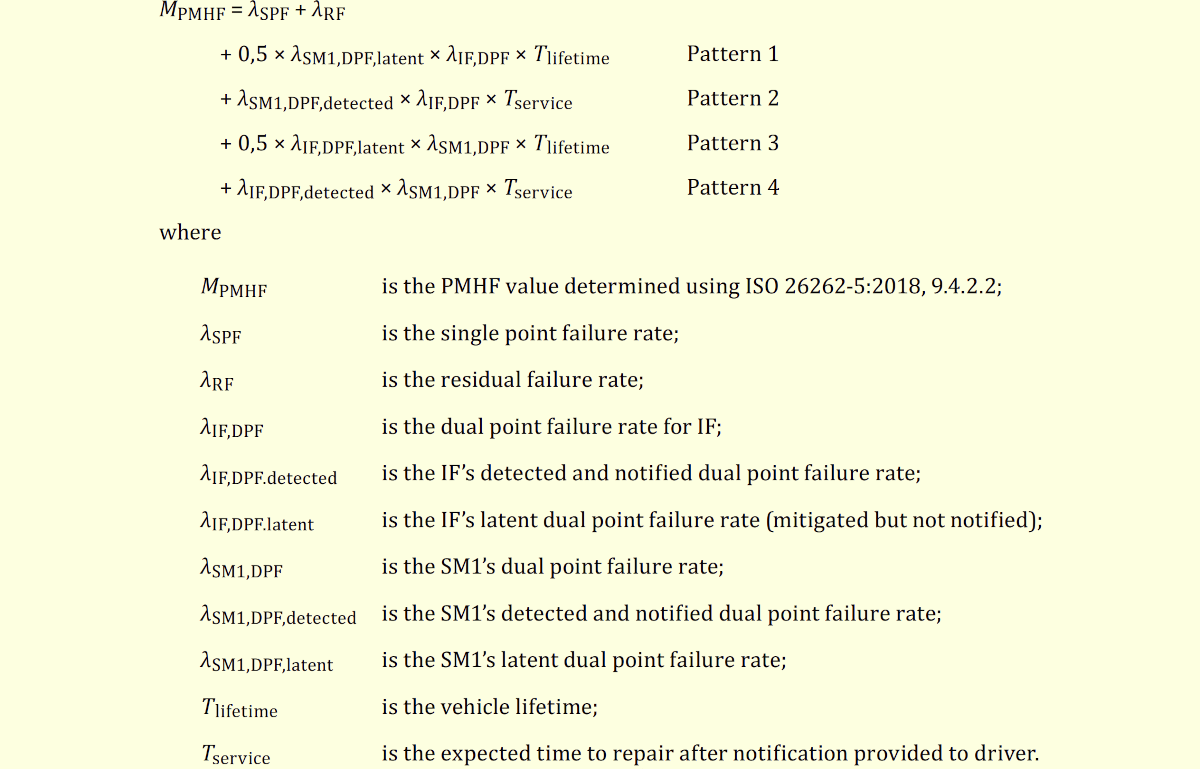

一方、本来のPMHF式は規格において

- 1st edition、すなわちISO 26262:2011のPMHFを適用する、もしくは

- 2nd editionのパターン3, 4をゼロとみなす

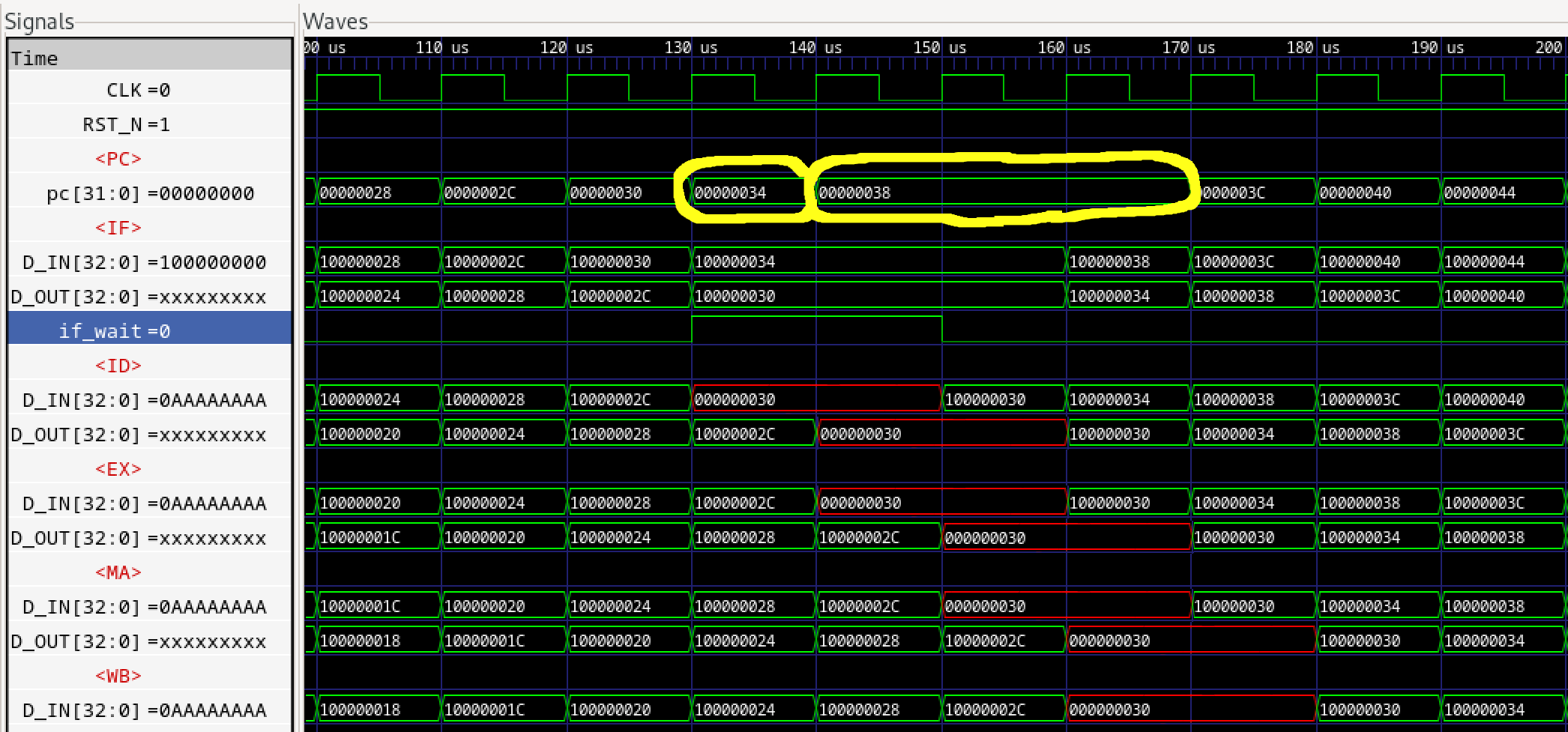

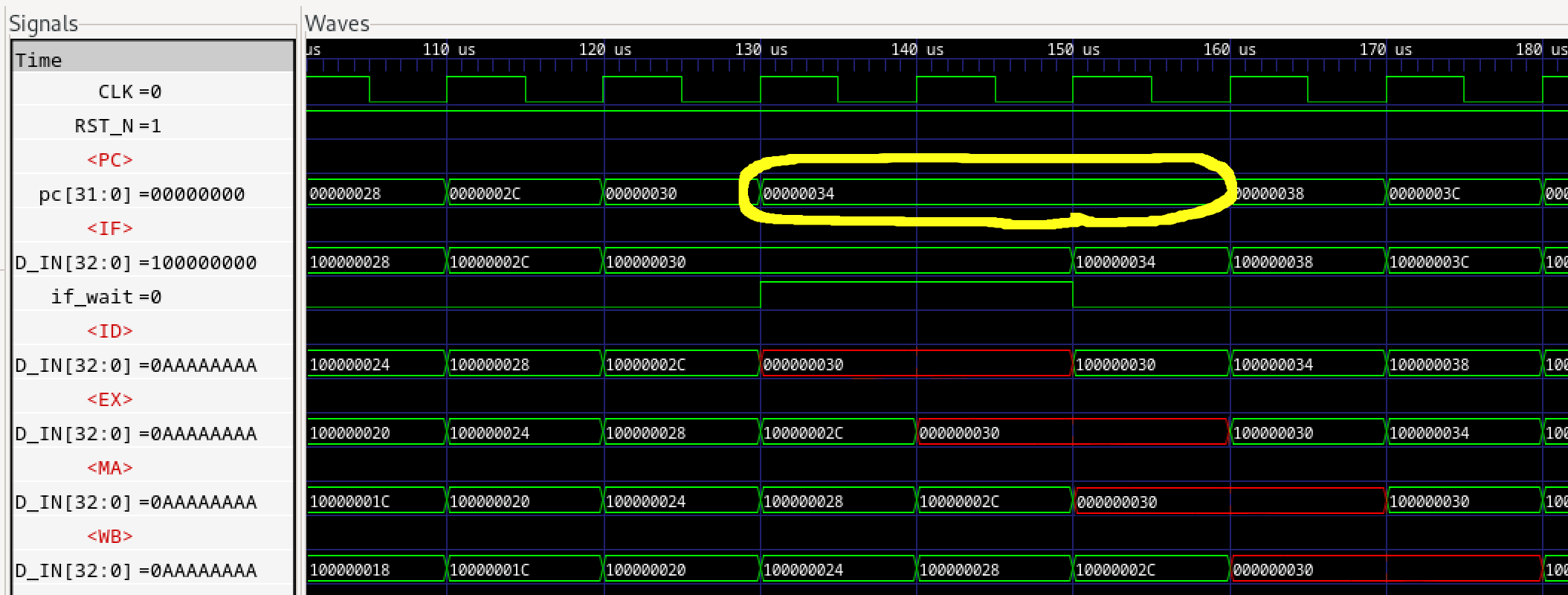

のいずれかを適用します。後者を用いるとPMHFは次の図329.1において、パターン3, 4を無視する形となります。

さらに、定期検査・修理期間内で発生するDPFによるVSG確率は小さいため無視します。つまり図329.1においてパターン2も無視します。すると図329.1はパターン1のみが残るため、

$$M_\text{PMHF}\equiv \lambda_\text{IF,SPF}+\lambda_\text{IF,RF}+\frac{1}{2}\lambda_\text{IF,DPF,det}\cdot\lambda_\text{SM,DPF,lat}\cdot T_\text{Lifetime}\tag{678.2} $$ ここで、(678.1)と(678.2)のSPF/RFに関する項は同一なので、DPFに関する項のみを比較すれば、

- $\lambda_\text{IF,DPF,det}$を$\lambda_\text{DPF_det}$とみなしている

- $\lambda_\text{SM,DPF,lat}$を$\lambda_\text{DPF_latent}$とみなしている

- $\frac{1}{2}$を無視している

の3つの近似を行っていることになります。それぞれを評価すれば、

- 本来 $$ \begin{eqnarray} \lambda_\text{DPF_det}&=&\lambda_\text{(IF+SM),DPF,det}\\ &=&\lambda_\text{IF,DPF,det}+\lambda_\text{SM,DPF,det} \end{eqnarray} $$ であるが、非冗長系ではIFに比べてSMの物量は一般に小さいことから $$\lambda_\text{IF,DPF,det}\gg\lambda_\text{SM,DPF,det}$$ 従ってSMに関する項は無視可能

- 本来 $$ \begin{eqnarray} \lambda_\text{DPF_latent}&=&\lambda_\text{(IF+SM),DPF,lat}\\ &=&\lambda_\text{IF,DPF,lat}+\lambda_\text{SM,DPF,lat} \end{eqnarray} $$ であるが、非冗長系ではIFのフォールトはLFにならないため、 $$\lambda_\text{IF,DPF,lat}=0$$ よってこの式は成立

- 係数$\frac{1}{2}$は近似のため無視

以上より、もともとDPF項はSPF/RF項と比較して小さいことから本近似式は成立するといえます。