|

19 |

RISC-Vプロセッサの設計 (20) |

1段FIFOの検討

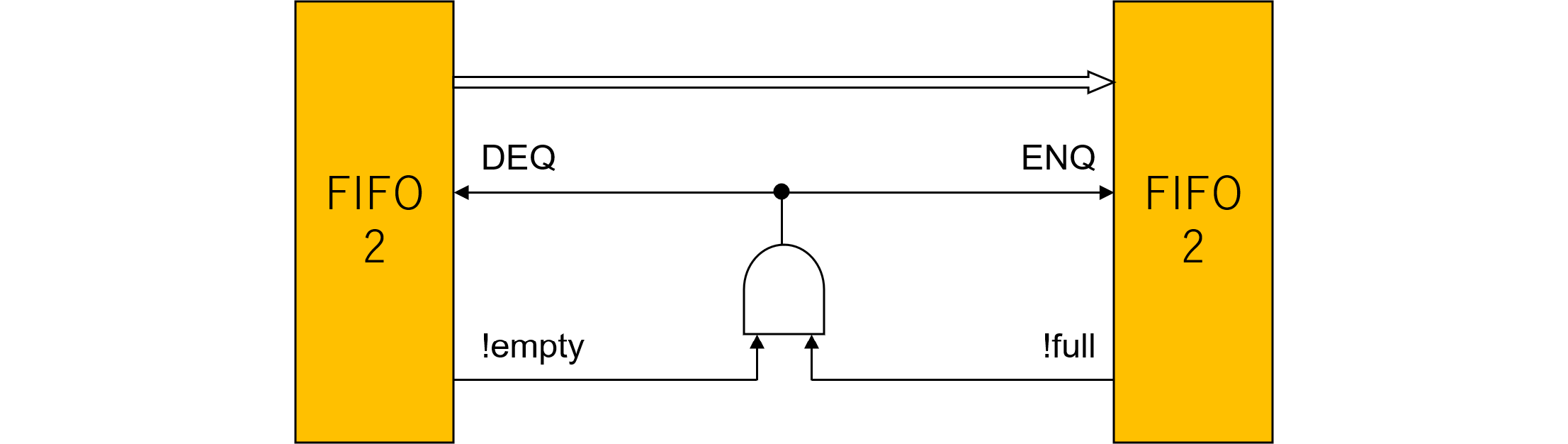

FIFOどうしを上位で接続する場合の結線を見ると、図573.1のようになっています。

上位ステージFIFOにデータが存在し(!empty)かつ下位ステージFIFOがフルでなければ(!full)上位ステージFIFOのDEQと下位ステージFIFOのENQが同時に実行されます。1段FIFOの実現性を考えると、下位のDEQが有れば上位に!fullになるように制御すれば良さそうです。

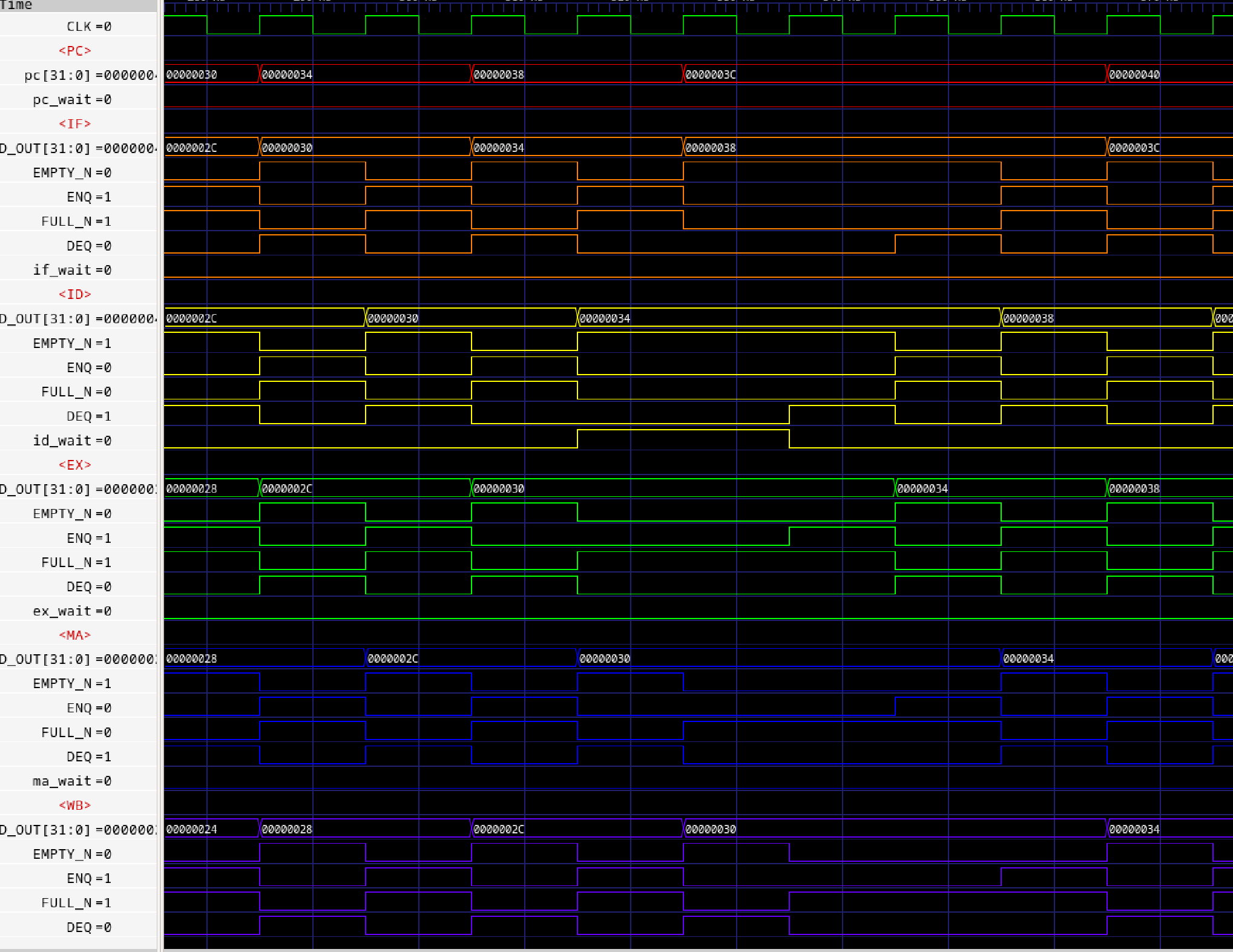

修正前の1サイクルおきの動作を示します。

元の論理はemptyとfullは背反論理であり、

assign FULL_N = !empty_reg;

assign EMPTY_N = empty_reg ;

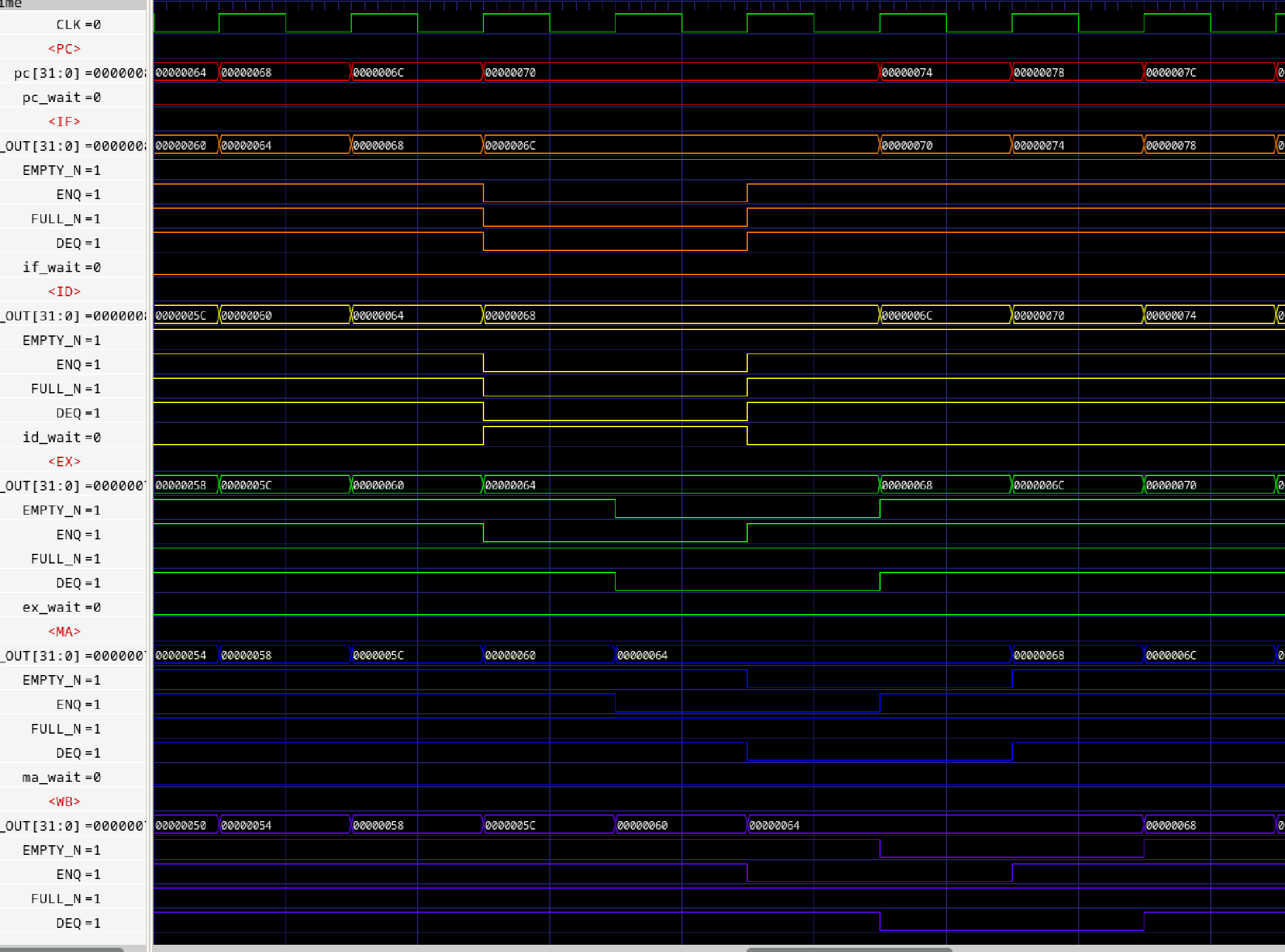

このようになっていましたが、これに対して、

assign FULL_N = !empty_reg || DEQ;

assign EMPTY_N = empty_reg ;

のように修正したシミュレーション結果を示します。

このように正しく動作しました。なお、この論理はパイプラインFIFOと呼ばれるLFIFOと全く同じであり、ソースに対して

FIFO#(int) ifs <- mkLFIFO;

のようにパイプラインFIFOを生成しても全く同じ動作を行います。

Leave a Comment