|

9 |

RISC-Vプロセッサの設計 (29) |

Maybeを使用した制御パイプラインをbscで合成し、生成されたverilogコードの一部を示します。

// submodule ifs

assign ifs$D_IN = { 1'd1, pc } ;

assign ifs$ENQ = ifs$FULL_N ;

assign ifs$DEQ = WILL_FIRE_RL_if_stage && !if_wait ;

assign ifs$CLR = 1'b0 ;

// rule RL_if_stage

assign WILL_FIRE_RL_if_stage = ids$FULL_N && ifs$EMPTY_N ;

// submodule ids

assign ids$D_IN = { !if_wait && ifs$D_OUT[32], ifs$D_OUT[31:0] } ;

assign ids$ENQ = WILL_FIRE_RL_if_stage ;

assign ids$DEQ = WILL_FIRE_RL_id_stage && !mc_wait ;

assign ids$CLR = 1'b0 ;

// rule RL_id_stage

assign WILL_FIRE_RL_id_stage = exs$FULL_N && ids$EMPTY_N ;

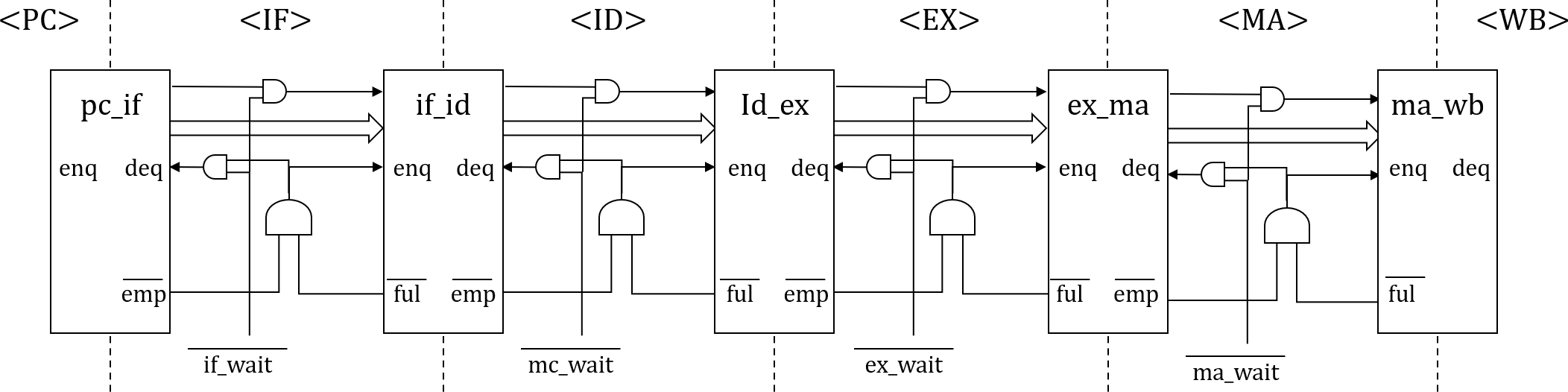

図674.2はこのコードを回路図に変換したものです。ハードウエア設計者はHDLコードよりもstaticな回路図のほうが理解し易いです。

各ステージ中のwait信号で上流方向は止めますが(中段左側のAND)、下流方向は止めずに(下段のAND)さらに下流にinvalidを流す(上段のAND)ところが、より単純な図673.1のデータパイプラインとの違いです。