|

8 |

Pongの開発 (14) |

|

QSPIプログラミング

FPGAプログラミングにはVivadoやPCやUSBケーブル等が必要ですが、電源を投入してアプリケーションをすぐに動作させるためにはCmodA7ボード上のQSPI Flashに書き込む必要があります。基本的には過去記事:Artyで実施したのと同じ手順ですが、異なる点だけを示します。

- Binファイルの作成: 過去記事どおりに実施します。

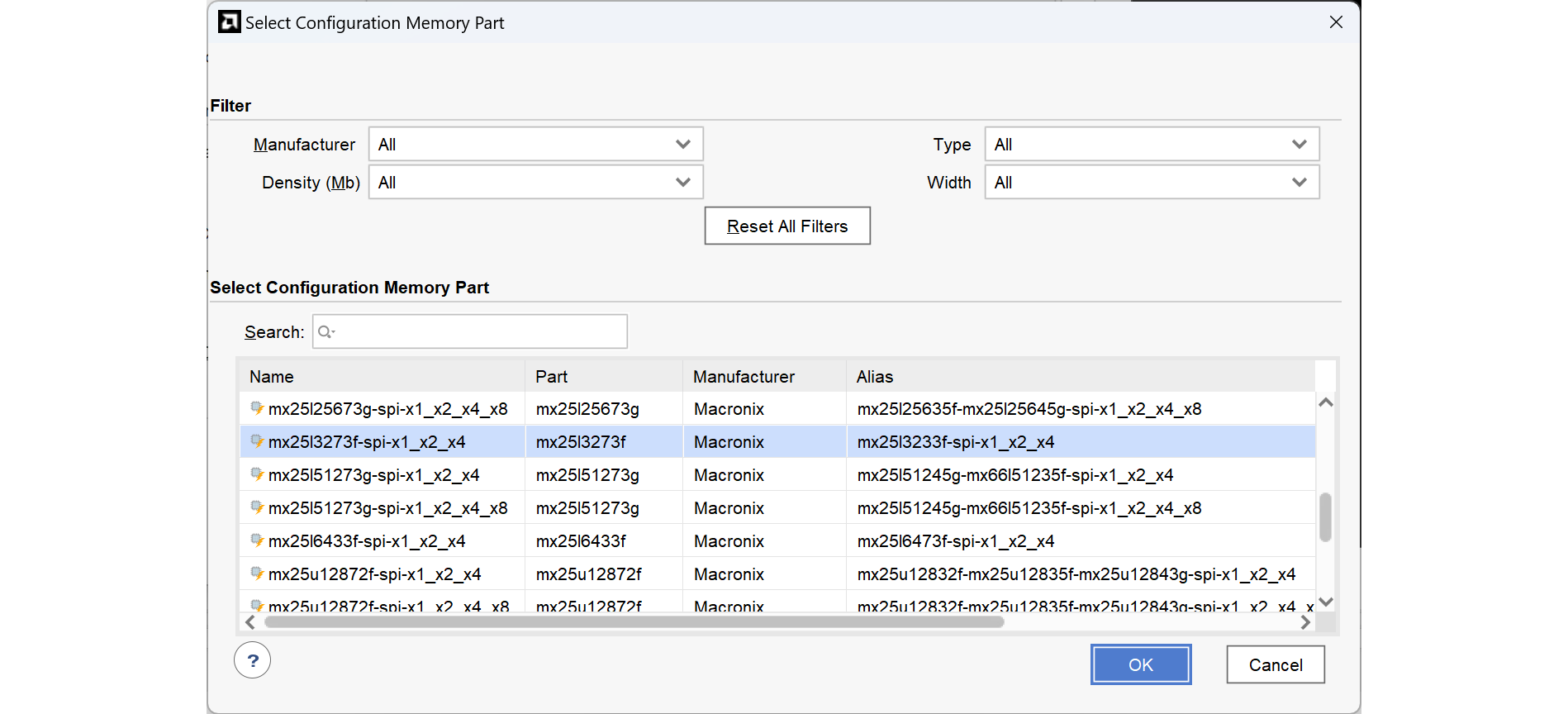

- Binファイルの焼きこみ: 選択するFlashの型格に注意します。以下の図のとおり、mx25I3273f-spi-x1_x2_x4を選択します。間違えて異なる型格を指定すると、Vivadoがエラーを出力し正しい型各を教えてくれます。