|

12 |

BSVによるSpace Invadersの変更 |

|

画面の縦横の入れ替え

Landscapeのモニタを使用しているため、Space Invadersは正立していますが、本来から比べると縦方向に縮んでいます。これを修正するには画面の縦と横を入れ替えます。VRAMの読み出しアドレスのxとyを入れ替えれば良いはずです。

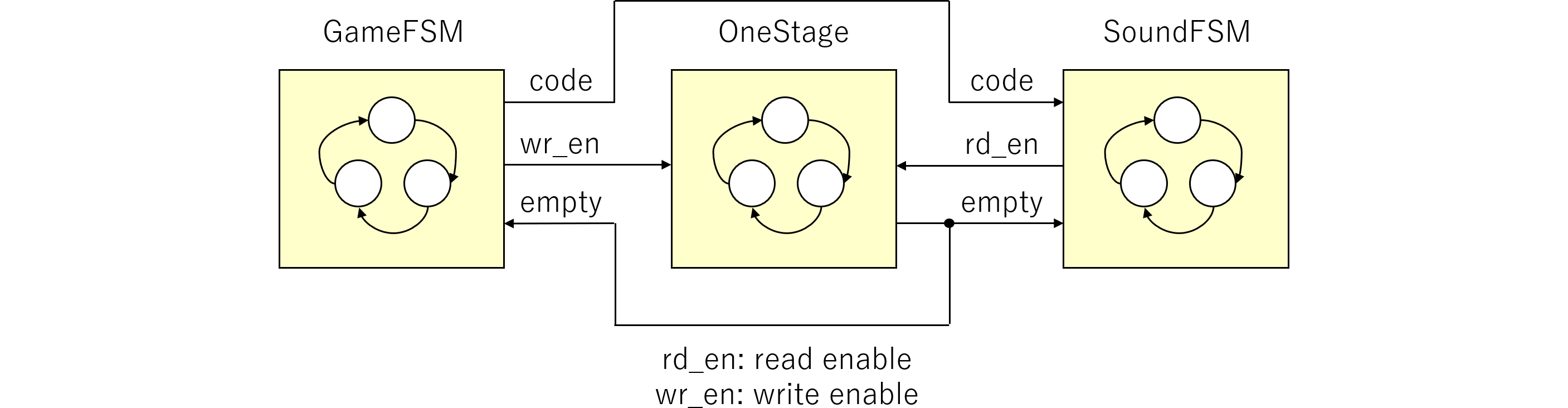

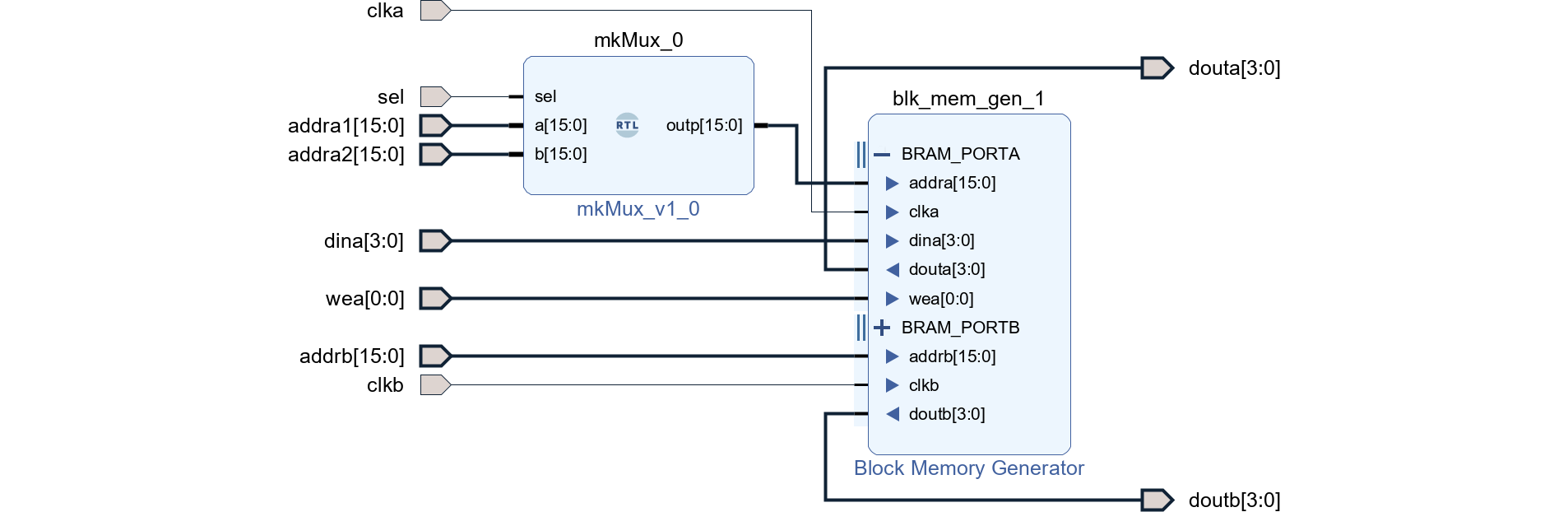

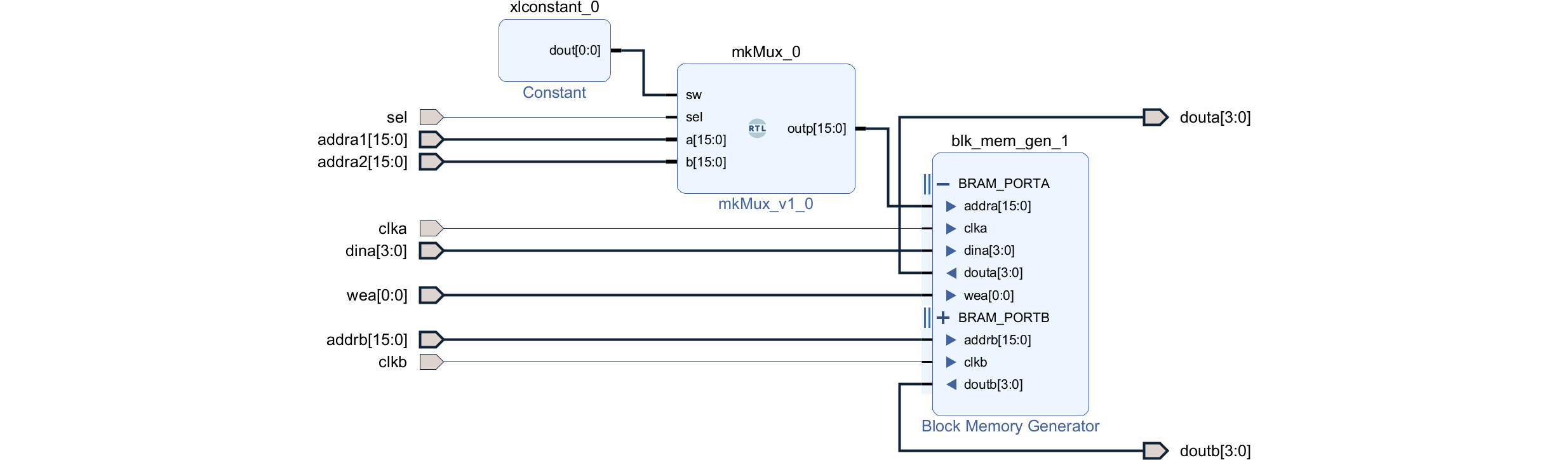

過去記事のVRAMのアドレス周りの図403.1を見ると、アドレスマルチプレクサが流用できそうです。これはFSMからのアドレスをメモリダンプ中にスイッチするものです。

元のMux.bsv:

typedef Bit#(16) Addr_t;

interface Mux_ifc;

(* prefix="" *)

method Addr_t outp(Bool sel, Addr_t a, Addr_t b);

endinterface

(* synthesize, always_ready = "outp", no_default_clock, no_default_reset *)

module mkMux(Mux_ifc);

method Addr_t outp(Bool sel, Addr_t a, Addr_t b);

if (sel) return b;

else return a;

endmethod

endmodule

このソースにおいて、中心部分はセレクタであり、

if (sel) return b;

else return a;

このようにselがtrueならb(メモリダンプFSMによるアドレス)、falseならa(ゲームFSMによるアドレス)を選択していました。

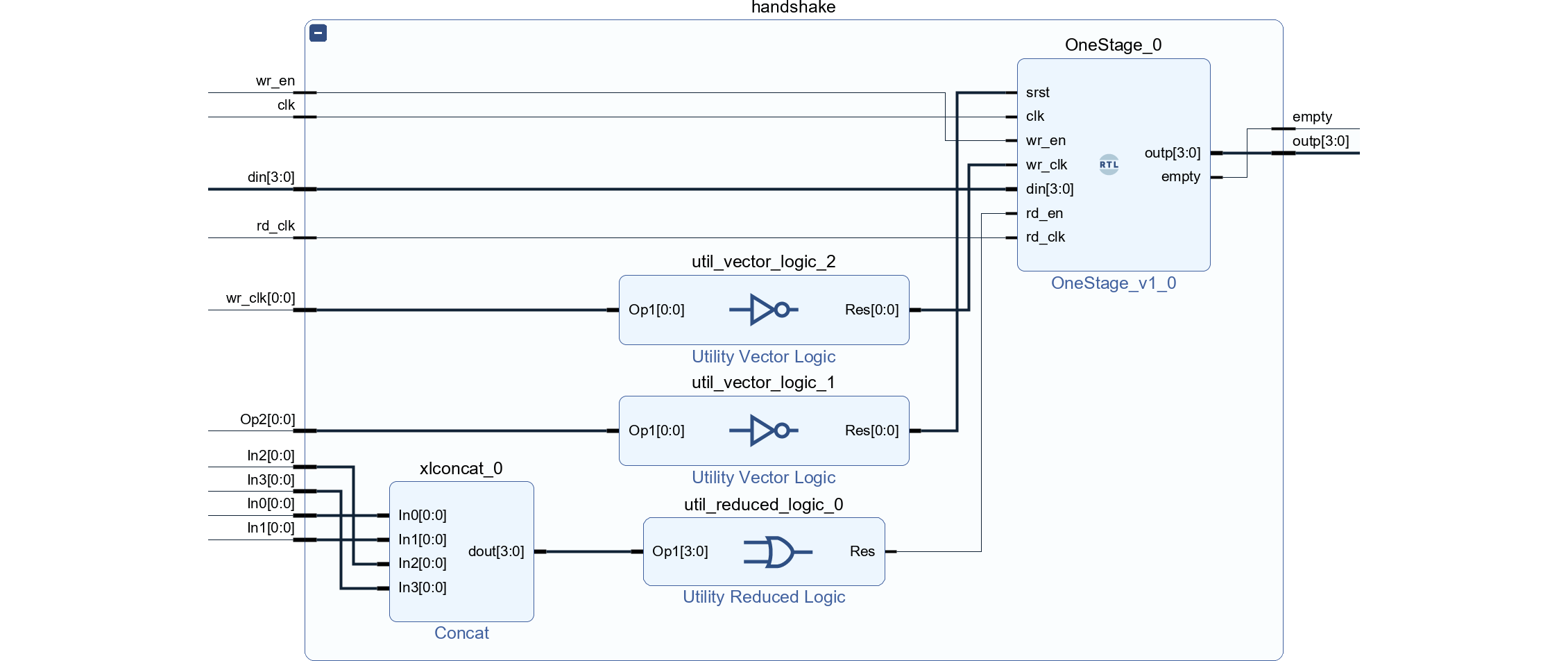

これに対し、図507.1のように新に1bitのスイッチを加え、スイッチがONのときにはゲームFSMによるアドレスの縦と横を入れ替えるように設計変更します。

具体的には通常時のアドレスa系のx座標アドレス(下位8bit)とy座標アドレス(上位8bit)を入れ替え、さらにy座標は上下反転します。上下反転は、256からアドレスを引くことで実現します。

$$ \begin{eqnarray} \left\{ \begin{array}{l} x&\Leftarrow&y \\ y&\Leftarrow&256 - x \end{array} \right. \end{eqnarray} $$