|

8 |

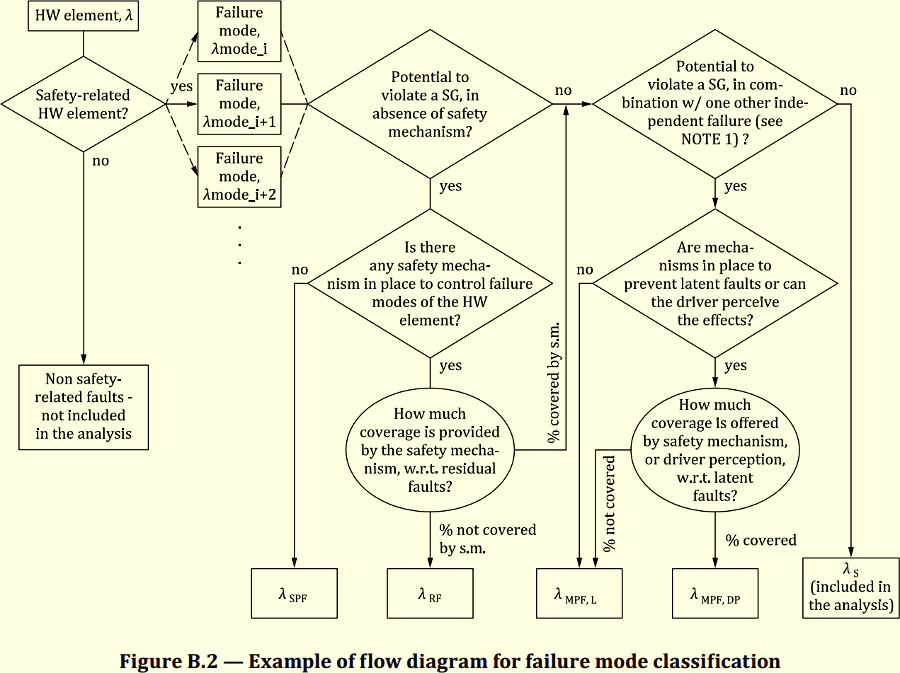

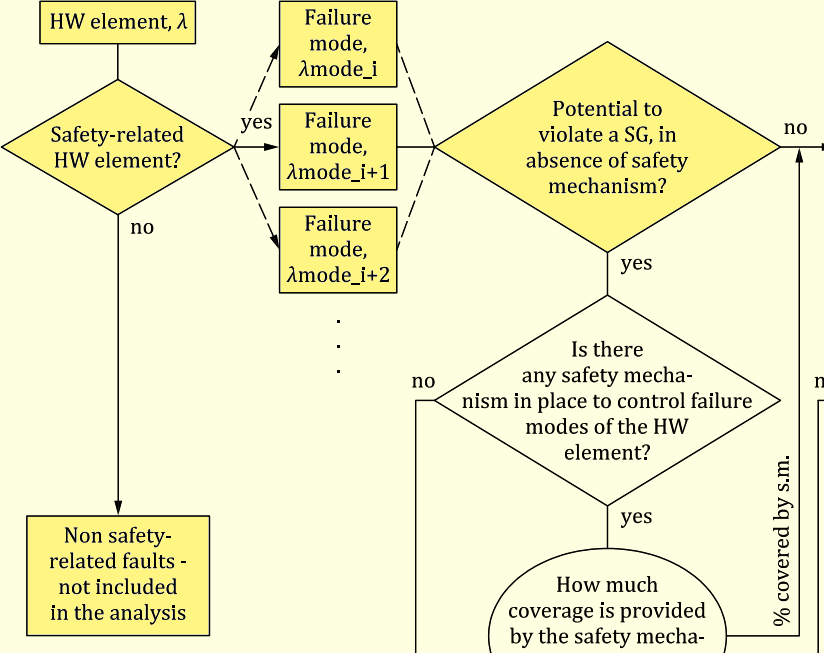

故障分類とフローチャート (2) |

まず、ECUのPCB上の部品を全てリストアップします。FMEAの考え方により、抜け漏れを防止するため、全ての部品を検討する必要があります。

- ISO 26262の入り口は、他の規格、例えばIEC TR 62380やSN29500等の故障率データベース、ないしは信頼性試験から算出された、部品の要素故障率です。この故障率を$\lambda$とし、左上の入り口から入ります。ただし、Part 5のフローチャートは定量計算ができないので、以下は定性的に考えます。

最初の菱形の判断は、この部品が安全関連であるかどうかです。Noの場合は「非安全関連」に分類され、分析から除かれます。最初に全ての部品を検討する理由は、抜け漏れの防止となるためですが、一方、無関係な部品はここでふるい落とされます。ちなみに、無関係な部品は実務上はあまり存在せず、例えばデバッグ回路等のように運転中に全く動作しない回路が相当します。他はたいていの場合安全関連です。Yesの場合は右に行き、「安全関連」と分類されます。言葉として紛らわしいのは、安全関連=危険側、非安全関連=安全側ということです。従って、安全関連と分類された部品は危険側を意味します。

次にこの部品に関して全ての故障モードを検討します。以下のフローは全ての故障モードに対して通ります。

- 次の菱形の判断は、安全機構(SM)を取り去った場合に安全目標侵害(VSG)を侵害するかどうかです。SMが無い場合はもちろん取り去るSMはありません。なぜ仮定の話を考えるかというと、ある部品の故障がVSGにつながるかどうかを考えるのがFMEAですが、一般的にSMが入っているので、ほとんどの部品はVSGとならないと判定されてしまうためです。それでは意味がないので、まずSMを除いて考えるわけです。