|

16 |

RISC-Vプロセッサの設計 (19) |

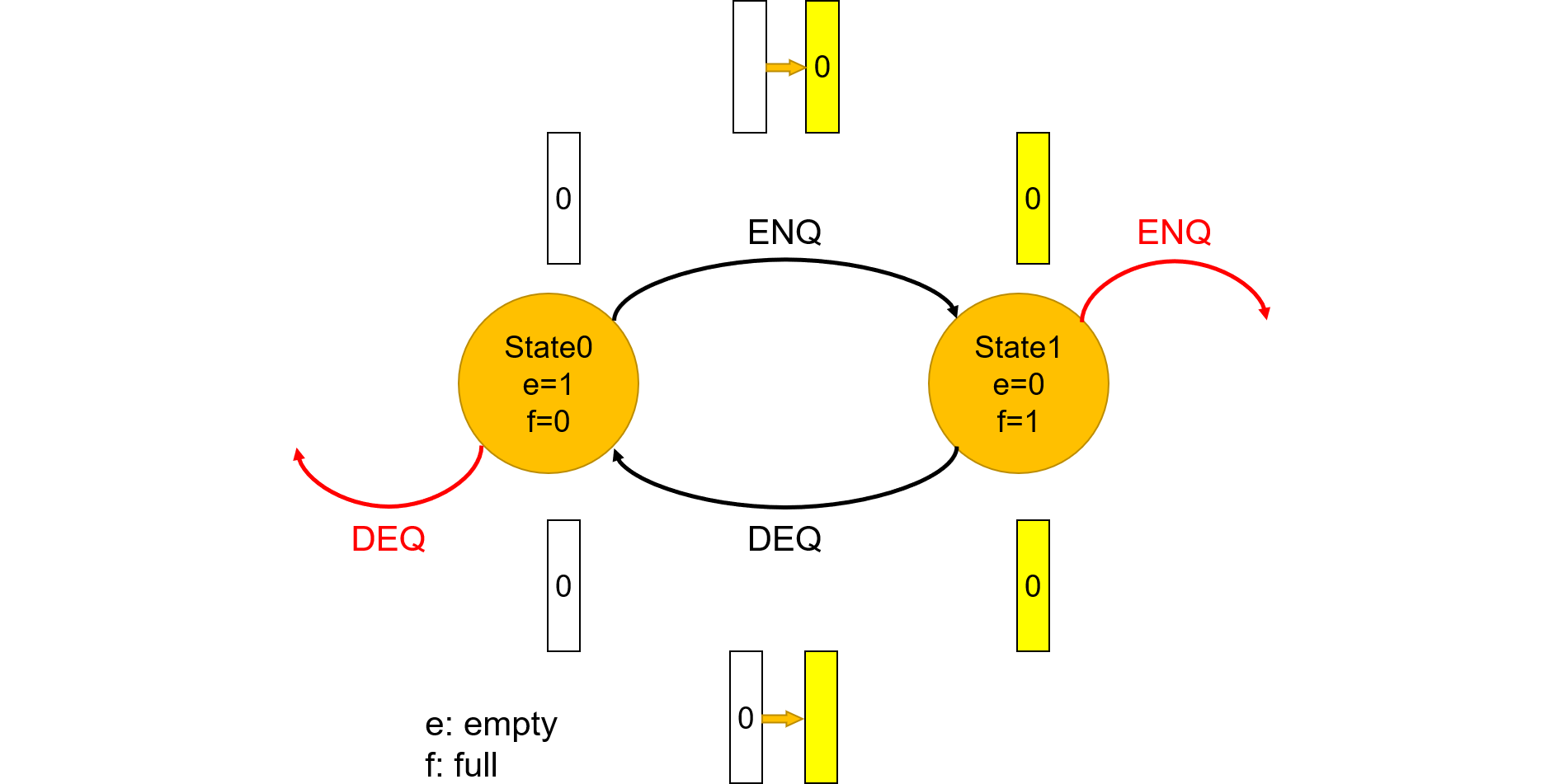

1段FIFOの検討

全く同様に1段FIFOを検討します。ここでの改善点はFullになっている場合にDEQ$ \cap $ENQを実行すると、1サイクル毎にアップデート可能な制御を行うことです。

| No. | State | DEQ/ENQ | d0入力制御 |

|---|---|---|---|

| 0 | --- | CLR | D.C. |

| 1 | State0(E:1, F:0) | !DEQ$ \cap $!ENQ | D.C. |

| 2 | !DEQ$ \cap $ENQ | d_in | |

| 3 | DEQ$ \cap !$ENQ | D.C. | |

| 4 | DEQ$ \cap $ENQ | D.C. | |

| 9 | State1(E:0, F:1) | !DEQ$ \cap $!ENQ | d0 |

| 10 | !DEQ$ \cap $ENQ | D.C. | |

| 11 | DEQ$ \cap !$ENQ | D.C. | |

| 12 | DEQ$ \cap $ENQ | d_in |

表より、ENQがアサートされたらd_inを入力する制御とします。

次にステート遷移表です。

| No. | Current State | ENQ/DEQ | Next State |

|---|---|---|---|

| 0 | --- | CLR | State0(E:1, F:0) |

| 1 | State0(E:1, F:0) | !DEQ$ \cap $!ENQ | State0(E:1, F:0) |

| 2 | !DEQ$ \cap $ENQ | State1(E:0, F:1) | |

| 3 | DEQ$ \cap $!ENQ | ERROR | |

| 4 | DEQ$ \cap $ENQ | ERROR | |

| 9 | State1(E:0, F:1) | !DEQ$ \cap $!ENQ | State1(E:0, F:1) |

| 10 | !DEQ$ \cap $ENQ | ERROR | |

| 11 | DEQ$ \cap $!ENQ | State0(E:1, F:0) | |

| 12 | DEQ$ \cap $ENQ | State1(E:0, F:1) |

これをこのまま実装するとState1の時にENQをアサートしようとしても、既にfullであるため、キューに入らない事態になります。これをfull=0として見せてやれば同時にDEQする時に限りキューに入れることができます。

Leave a Comment