|

22 |

Parameterについて |

Parameterについて

Verilogにおいてparameterという機能があります。これは動的に定数を変更することができ便利な機能ですが、ソースを修正することからあまり使用していませんでした。

ところがIPインテグレータを使用すれば、ソースを修正することがなく再合成だけで仕様を変更することができます。今回テスト回路を作成し、BSVからFPGAまでの繋がりを確認します。

BSVにおいてのparameter

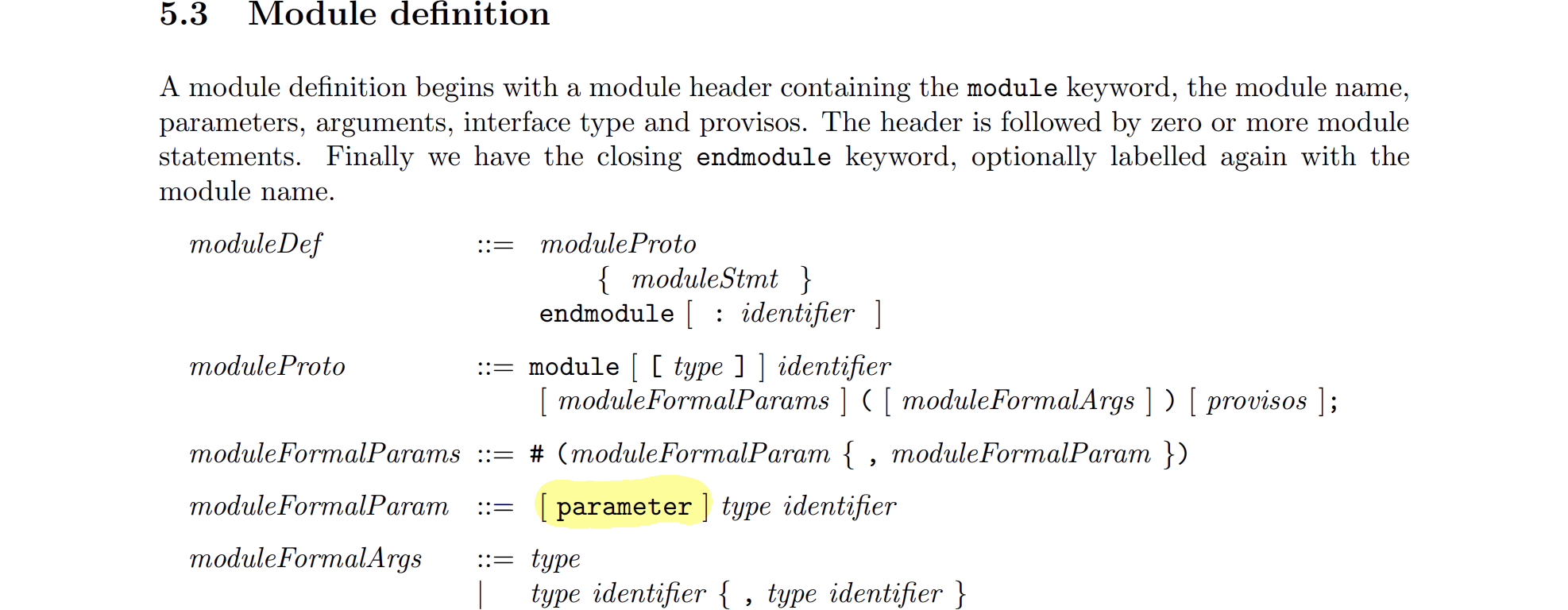

BSVリファレンスガイド5.3モジュールにパラメータの文法が書かれています。これを用いたテスト回路を作成します。

文法を見るとわかるようにデフォルト値を設定する機能はありません。'='記号の使用等でそれが可能であればよかったのですが。

以下に具体的なBSVコードを示します。ボタンを押すとパラメータで指定された数だけパルスを出力するFSMです。ポートリストというかメソッドリストの直前にカッコ書きで記述するようです。

import StmtFSM::*;

interface FSM_ifc;

method Action button(Bool flag);

method Bool lrclk();

endinterface

(* synthesize,always_ready,always_enabled *)

module mkTestParam #(

parameter Int#(32) count

) (FSM_ifc);

Reg#(Bool) outPulse <- mkReg(False),

buttonf <- mkReg(True);

// Mainloop

Stmt main = seq

while(True) seq

outPulse <= False;

await(!buttonf);

await(buttonf);

repeat (unpack(pack(count))) seq

outPulse <= True;

outPulse <= False;

endseq

endseq

endseq;

mkAutoFSM(main);

method Bool lrclk();

return outPulse;

endmethod

method Action button(Bool flag);

buttonf <= flag;

endmethod

endmodule: mkTestParam

パルスの出力回数を表すcountをパラメータ化しました。

Leave a Comment