|

23 |

Parameterについて (2) |

verilogにおけるparameter

次にbscを用いてverilogにコンパイルします。

$ bsc -verilog TestParam.bsv

Verilog file created: mkTestParam.v

コンパイルするとmkTestParam.vというverilogファイルが生成されます。パラメータ部分を見ると、

:

module mkTestParam(CLK,

RST_N,

button_flag,

lrclk);

parameter [31 : 0] count = 32'b0;

:

のように、モジュール定義のすぐ後にparameterとしてcountが定義されています。そのほかにもverilogコード内でcountは複数使用されていますが、レジスタではないので書き込みのコードは存在せず、定数として参照されています。例えば、

assign n__h31509 = count - 32'd1 ;

;

assign MUX_jj_repeat_count$write_1__VAL_1 =

(n__h31509[15:0] == jj_repeat_count) ? 16'd0 : x__h31537 ;

のようにcount-1とjj_repeat_countが一致するかのテストを行っている回路が生成されます。repeat_countは文字通りrepeat回数の実行時の変数と思われ、終了条件としてそれがcount-1(定数)と一致するかのテストを行っているようです。

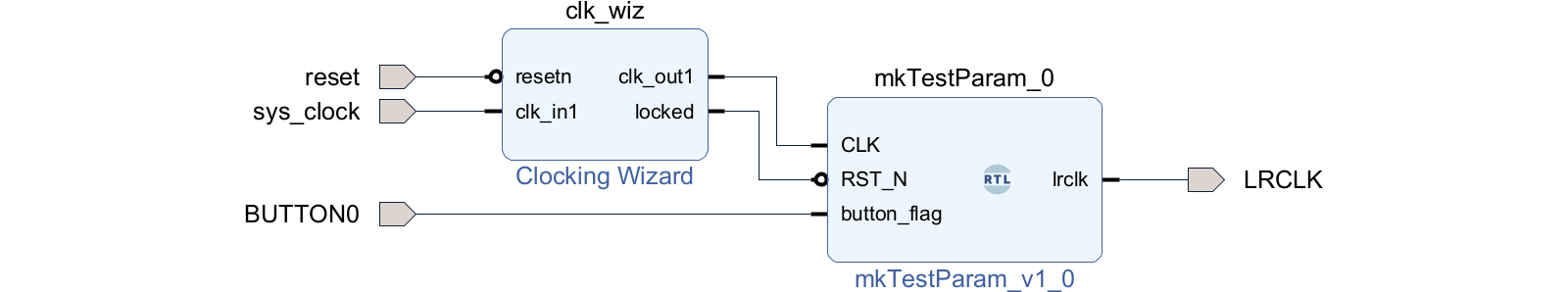

IPインテグレータによる変更

これだけであれば、結局bsvなりverilogのパラメータ部分を修正するので、ソース修正となることからdefineでもあまり変わりません。

完全に動的にはいかずとも、ソースファイルを編集することなくVivaoのIPインテグレータのブロックデザイン画面上で変更する方法があります。

まずVivadoでmkTestParam.vをソースとして読み込み、回路をインスタンシエートします。

Leave a Comment