|

20 |

Ultra96toPMODボードの設計変更 (2) |

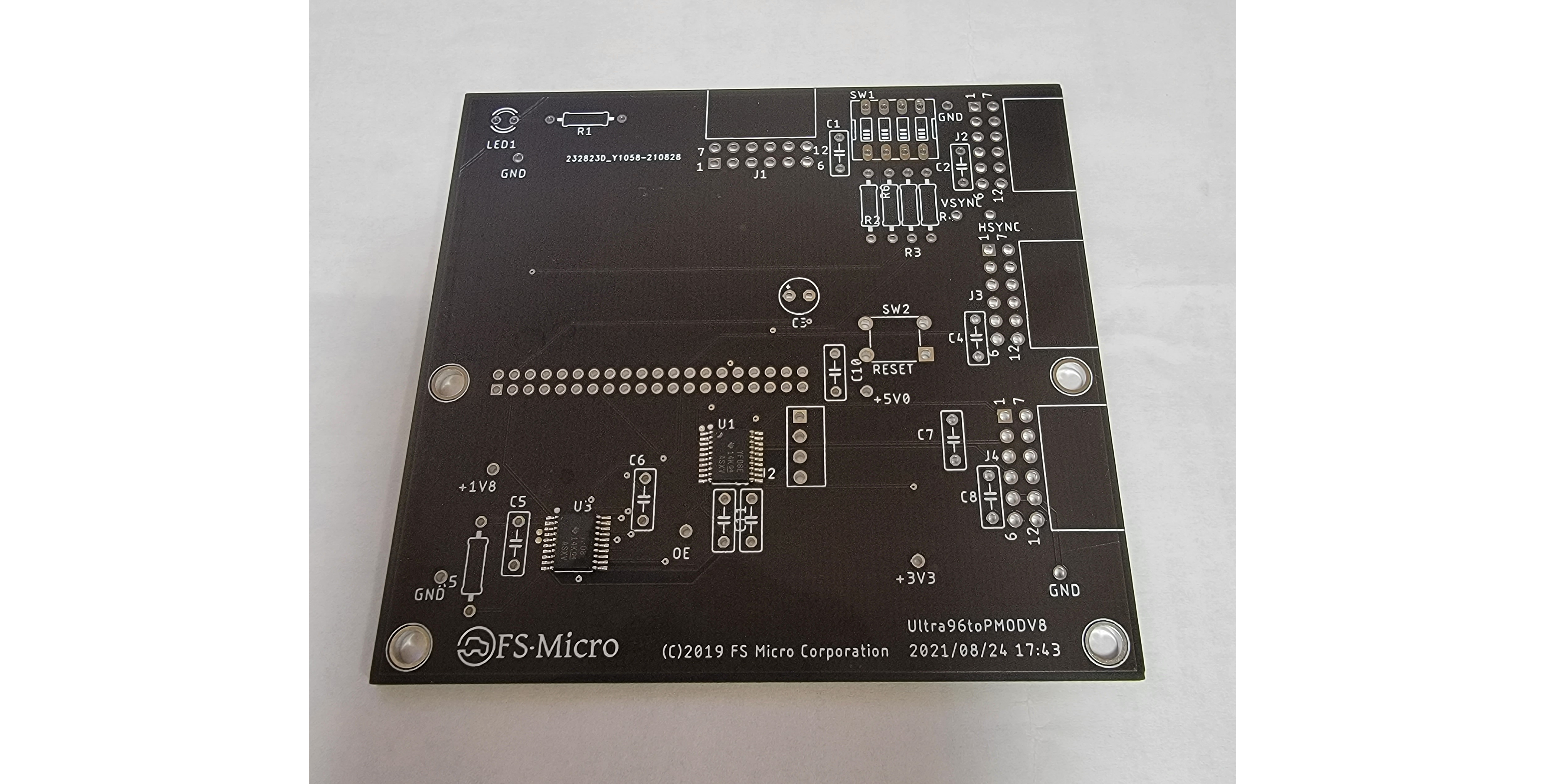

V8基板が到着しました。今回も実装が安いBokTechに依頼しました。

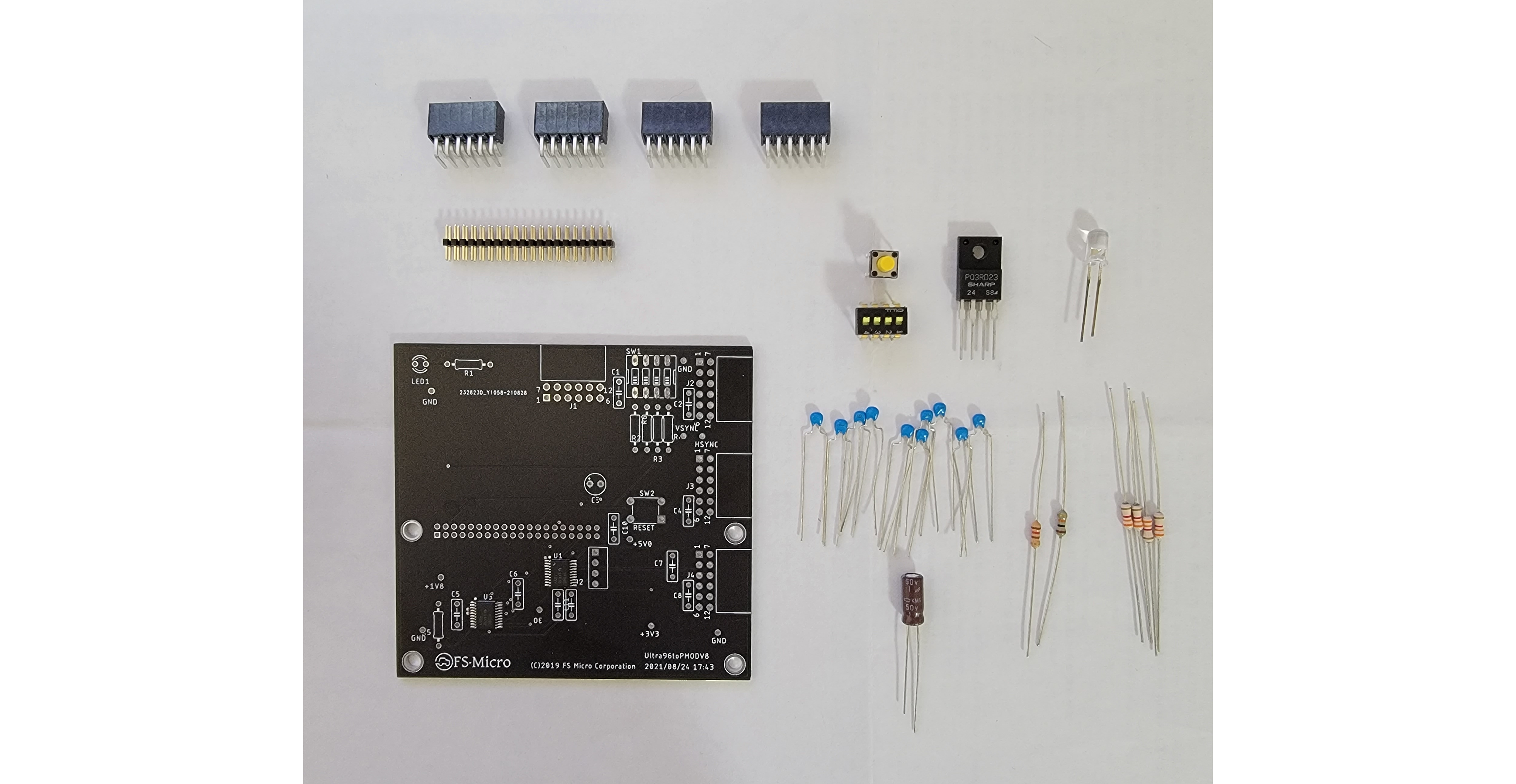

部品を並べたものが図436.2です。

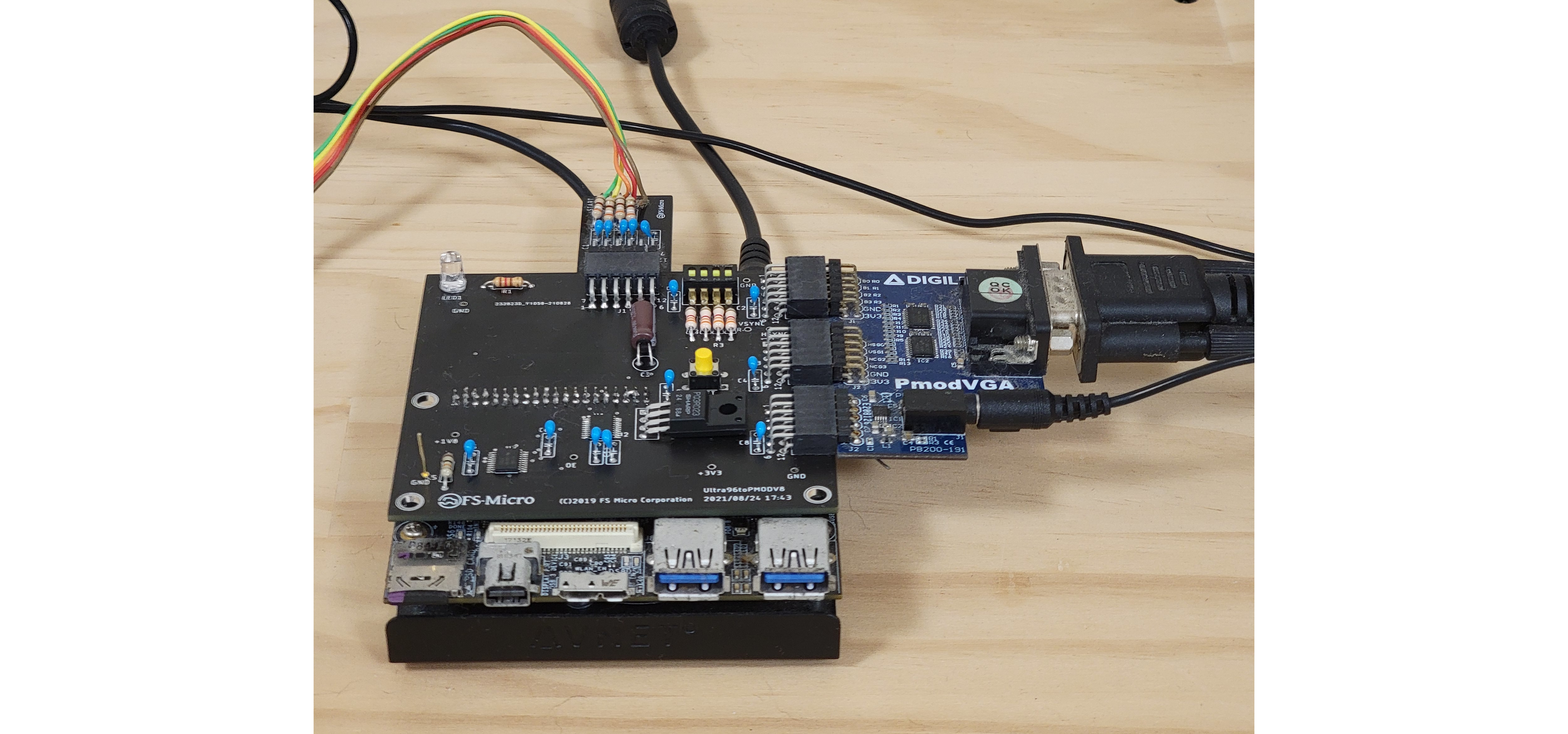

組み立てたものが図436.3です。

正常に動作したものの、デバッグ途中で修正箇所を発見したため、V9として改版中です。具体的には、

- Dip SWの入力がレベル変換ICにより1.8Vに変換されて入力されていた(Dip SWはスタティック信号のため、レベル変換ICの必要無し)⇒Dip SWの電源を1.8Vに変更し、ダイレクト入力に変更

- Joy SWの入力が3.3Vダイレクト入力だった⇒1.8Vにレベル変換して入力(ラッチアップの可能性有るため)

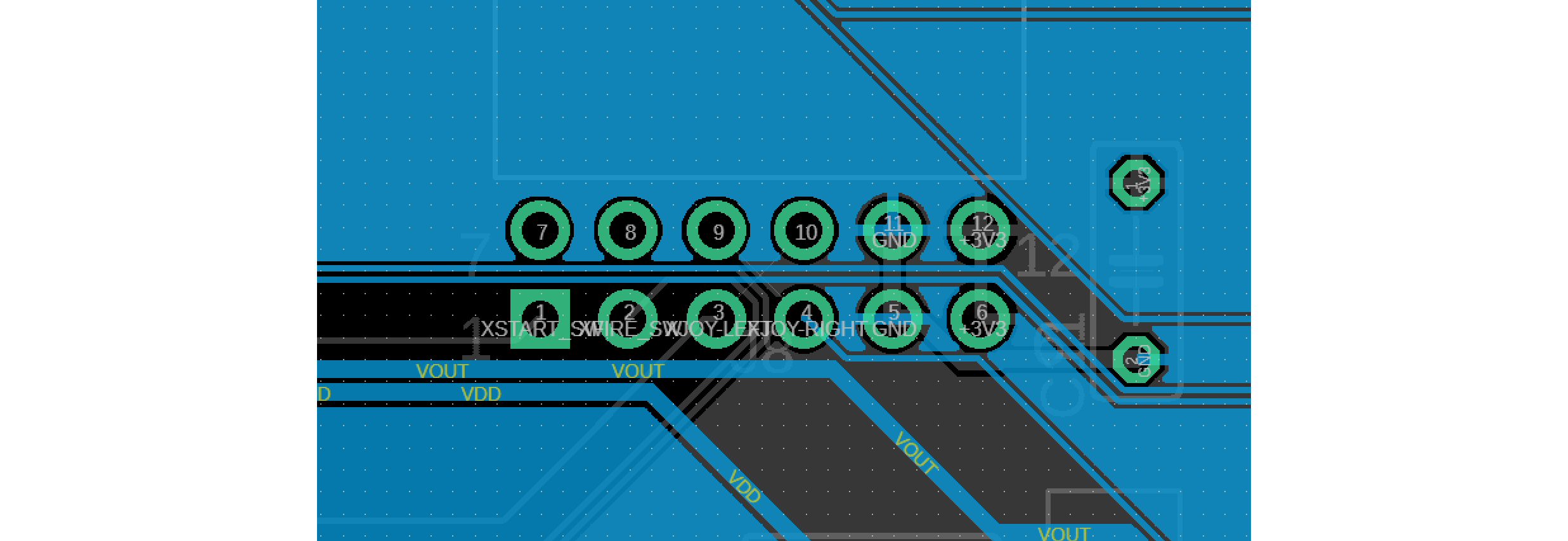

Joy SWはV3において、1.8Vへのレベル変換ICを通すように変更したのですが、その際にSW信号が水平・垂直同期信号に悪影響を与えたため、V4以降で元に戻したものです。ただし動作しているとはいえ、1.8V入力に3.3Vを加えています。今回は再度V3と同様に修正します。ちなみにV3での悪影響の理由は、レベル変換ICで混信したのではなく、図436.4のように、レイアウト上同期信号がSW信号の間を通っていたためのようです。

【追記】レベル変換ICの端子間もしくはIC内部での混信のようでした。

V9ではV3と同様、再度JoySW信号を1.8Vへのレベル変換ICに入れるように修正しました。合わせて、レイアウト上SWの間を水平・垂直同期信号が通らないように注意して配線しています。