|

24 |

Ultra96と拡張インタフェース |

Ultra96

Avnetから画期的なZynq UltraScale+ FPGA評価ボードが発売されたので入手しました。何が画期的かというと、搭載されているチップが20nm先端プロセス、ARM A53×4コア、R5×2コアを搭載したFPGA評価ボードが、従来20万円以上したいわばプロ用の評価ボードが約3万円という、アマチュアにも手が届く価格になったことです。同じチップを搭載しているボードの過去記事はhttp://fs-micro.com/post/show/id/39.htmlです。また、インベーダゲームを実装した記事はhttp://fs-micro.com/post/show/id/52.htmlであり、同じチップであることから、簡単に実装可能と思われます。

開発ツールも無償のWebpackという論理合成、シミュレーション、配置配線全部入りのツールが使えるので、ひと昔前の設計現場では考えられない素晴らしい環境となりました。LSIのEDA、特に配置配線等では数千万円するものもあったのです。

メーカサイト:

http://zedboard.org/product/ultra96

拡張インタフェース

以前に設計したグラフィックディスプレイコントローラとサウンドコントローラを、本Ultra96ボードのFPGAに実装します。

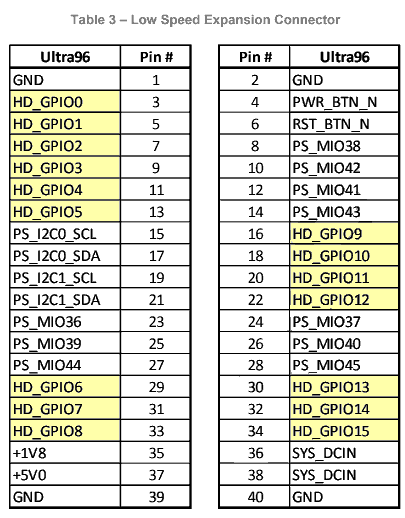

問題点としては、図80.2に黄色で示すように汎用GPIOが16本しかなく、グラフィック系だけでも各色4bit×3原色=12bitあり、他にサウンド系4bit、スイッチ系で4bitと少々オーバーします。幸いグラフィクスは各色4bitも使用していないので、各色1bit×3原色=3bitとして本数を減らすことにします。

目的

掲載予定のアプリケーションを示します。