|

20 |

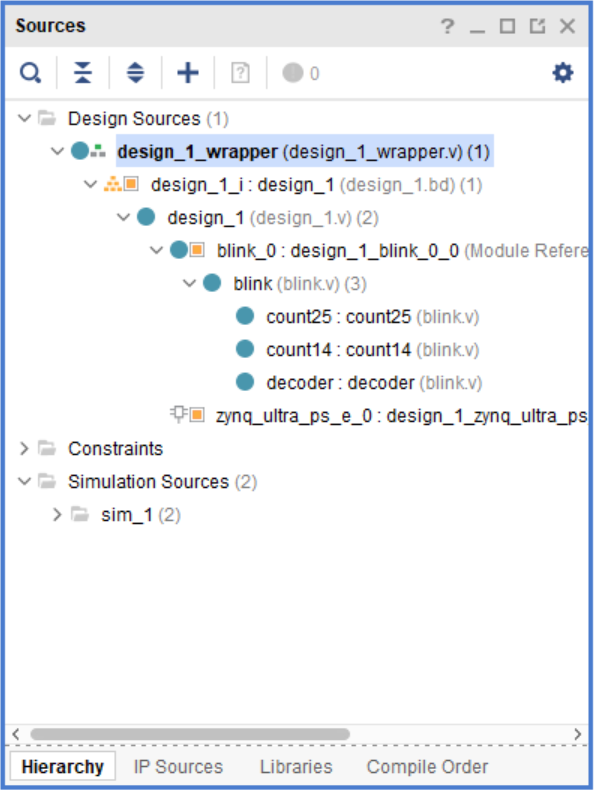

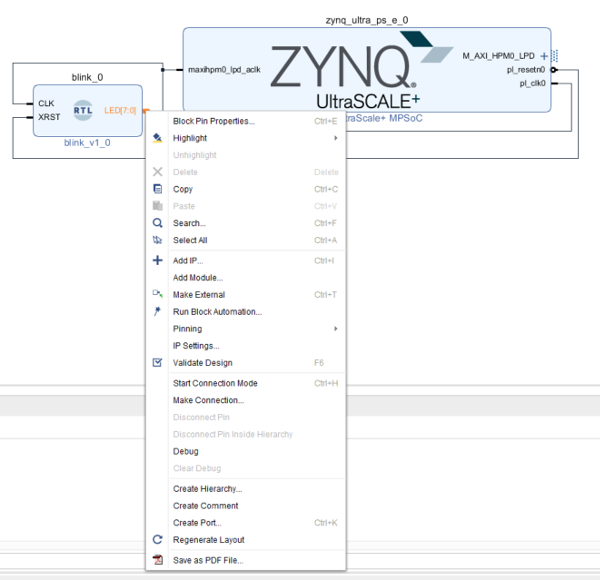

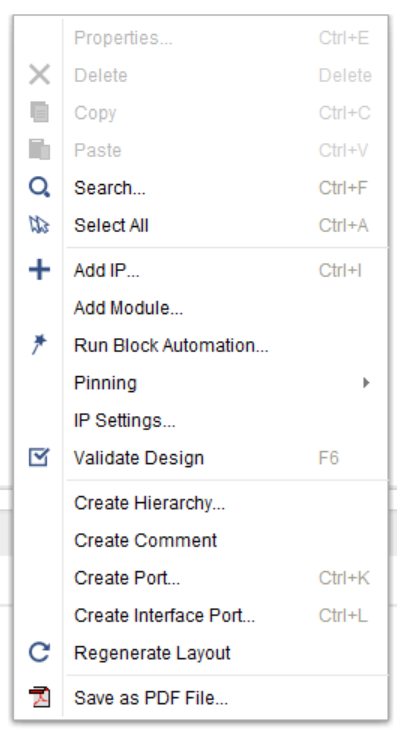

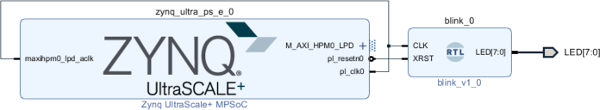

Lチカの実装 (7) |

|

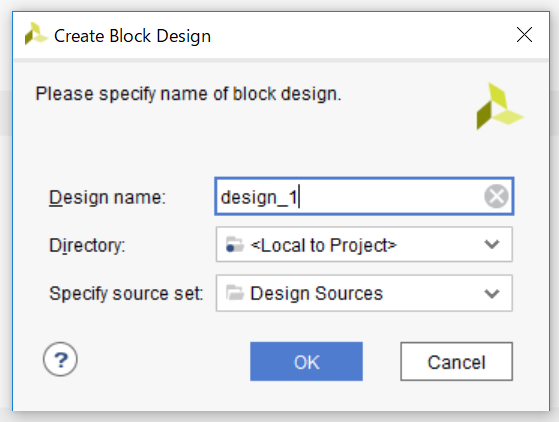

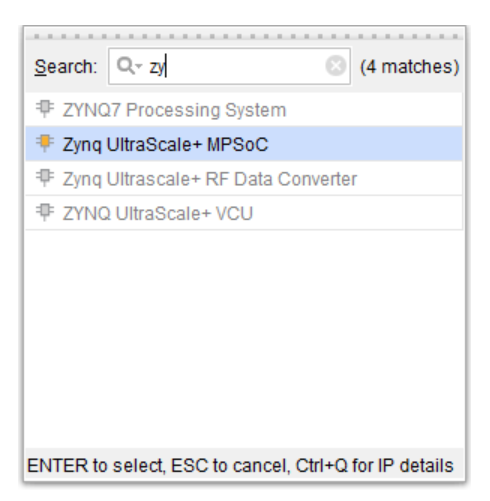

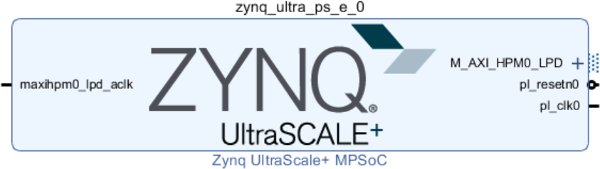

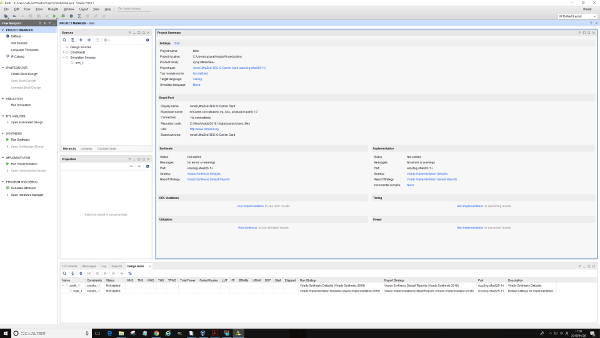

Vivadoの操作

- シミュレーション

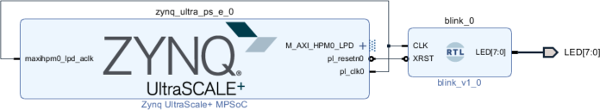

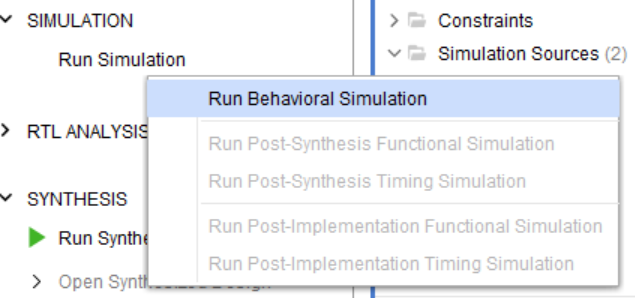

シミュレーションにより、動作が正しく行われるかを確認します。左のFlow NavigatorからSIMULATIONの下のRun Simulationをクリックし、Run Behavioral Simulationを実行します。

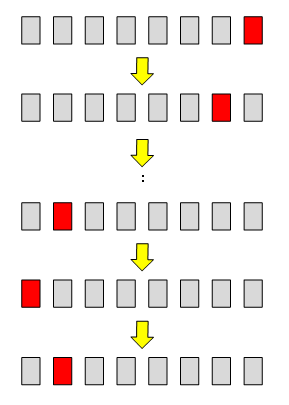

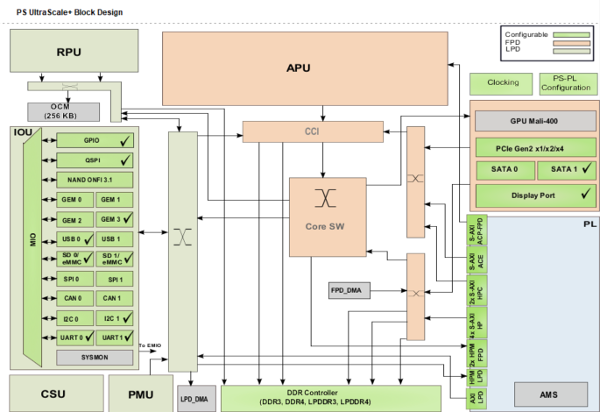

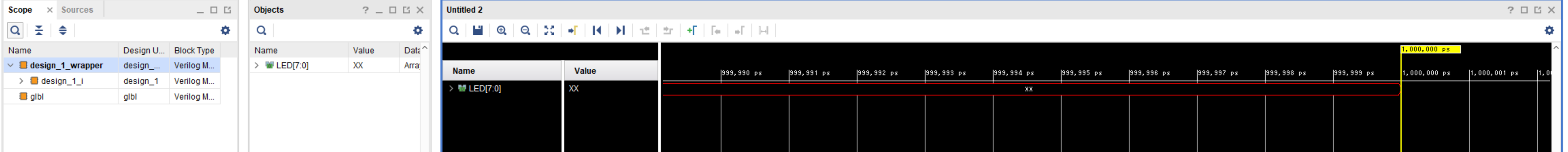

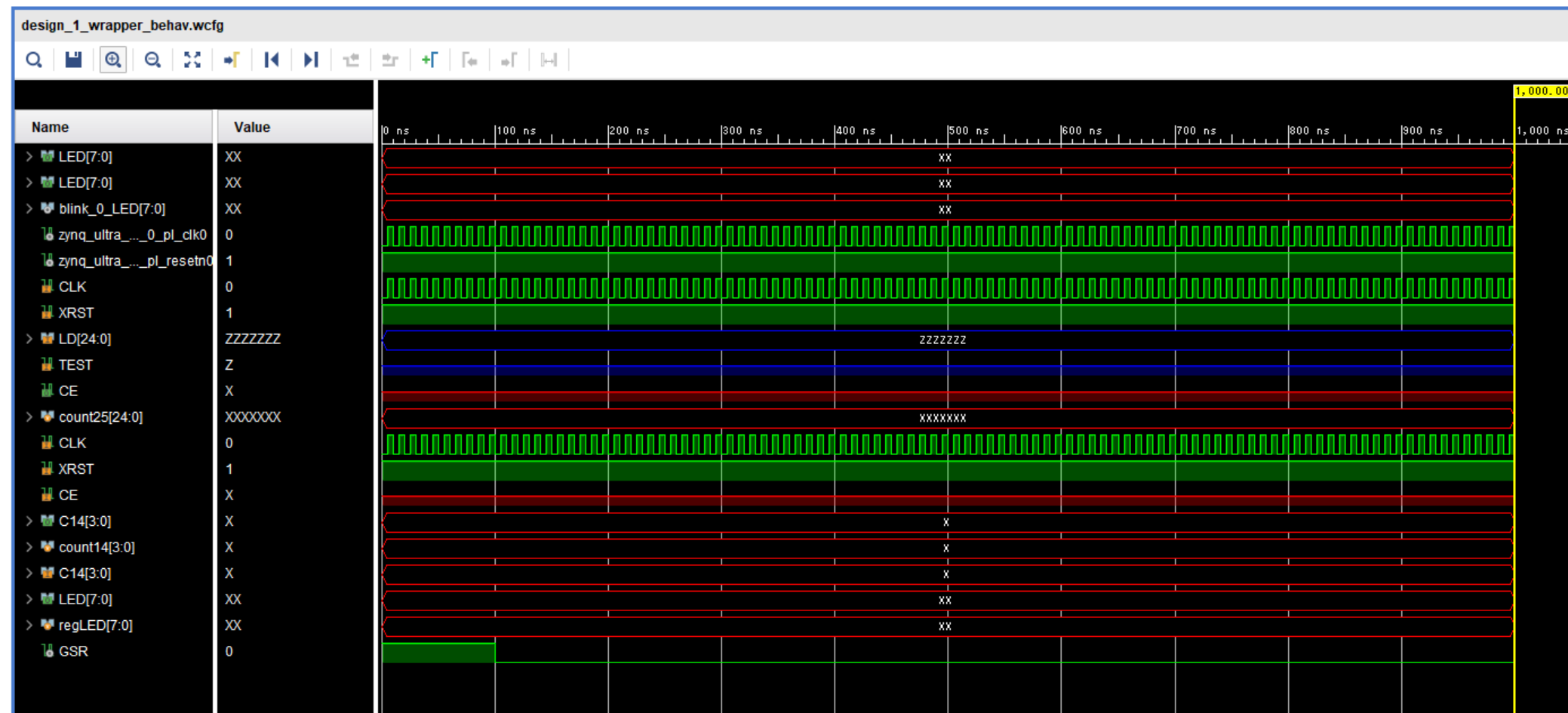

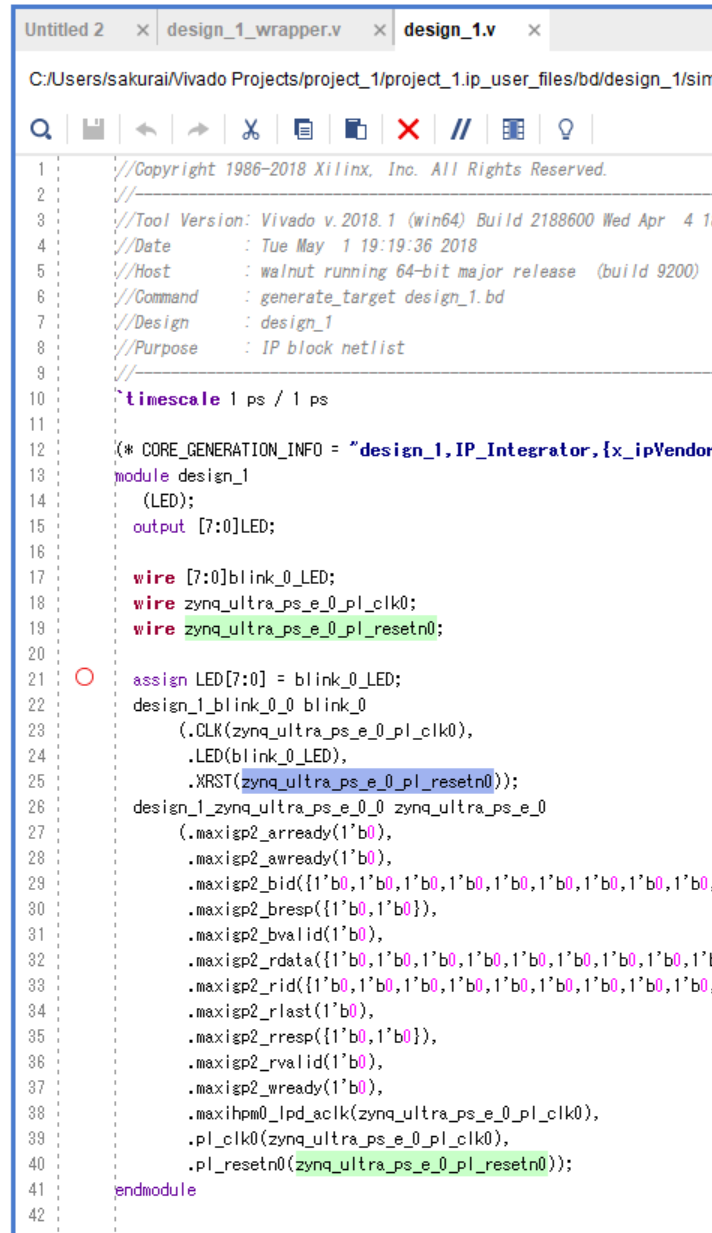

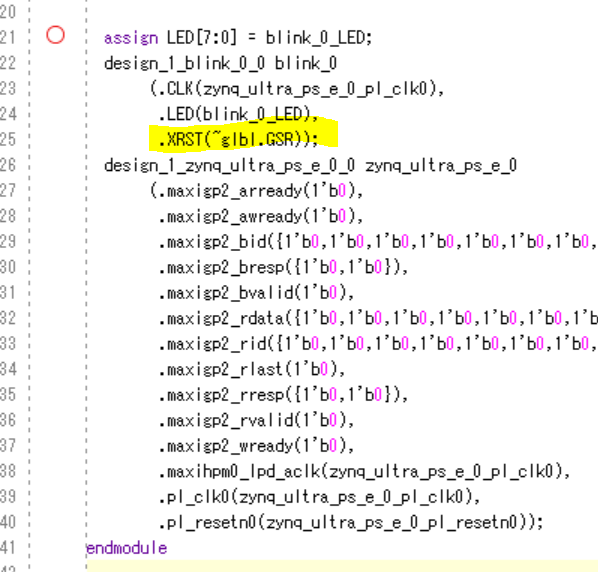

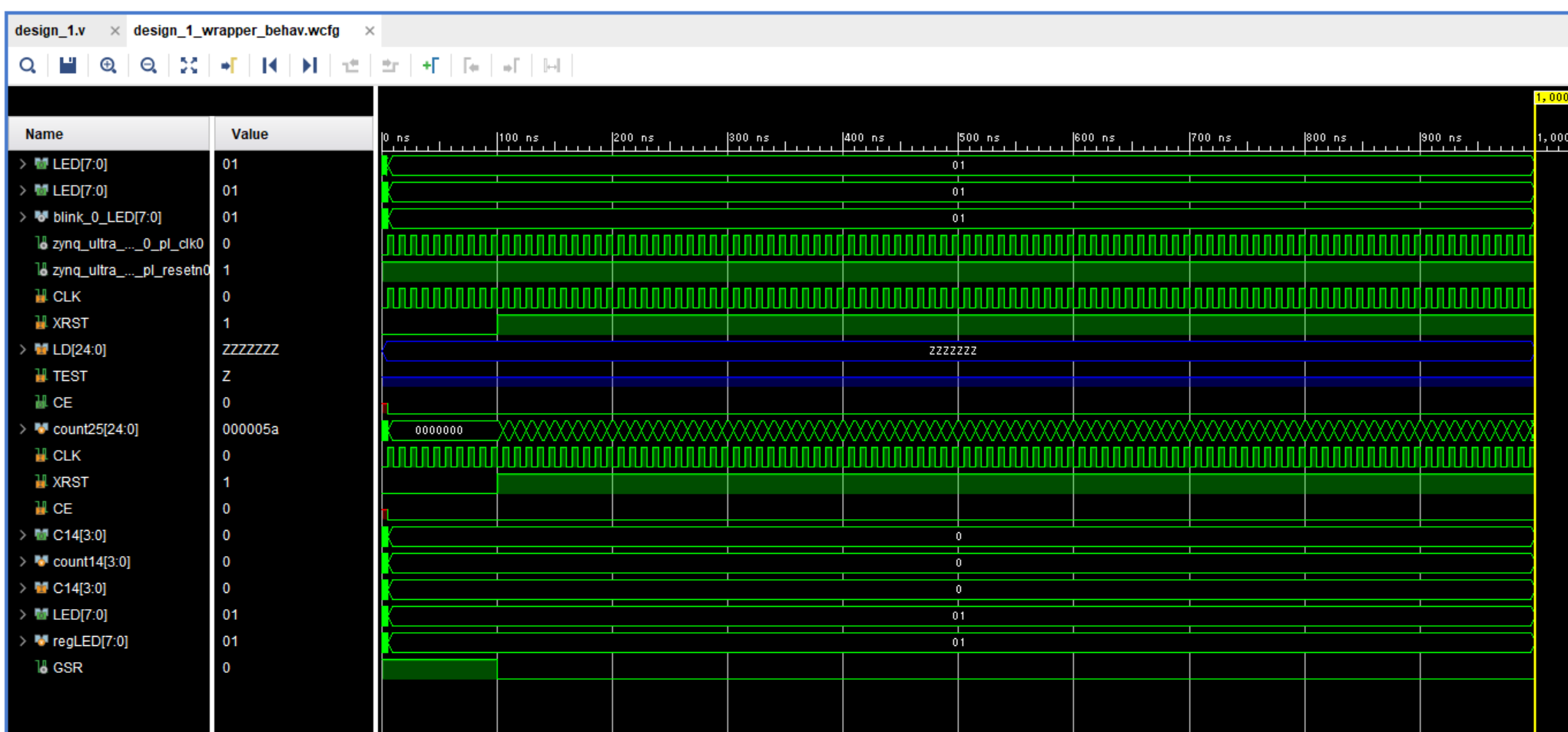

しばらく待つと以下のようにシミュレーションが動作するが、リセットがうまく入っていないため、カウンタ値が不定となっています。PSからのリセットはソフトで指示しないとかからないのかもしれません。従って、シミュレーションで動作するようにワークアラウンドを行います。

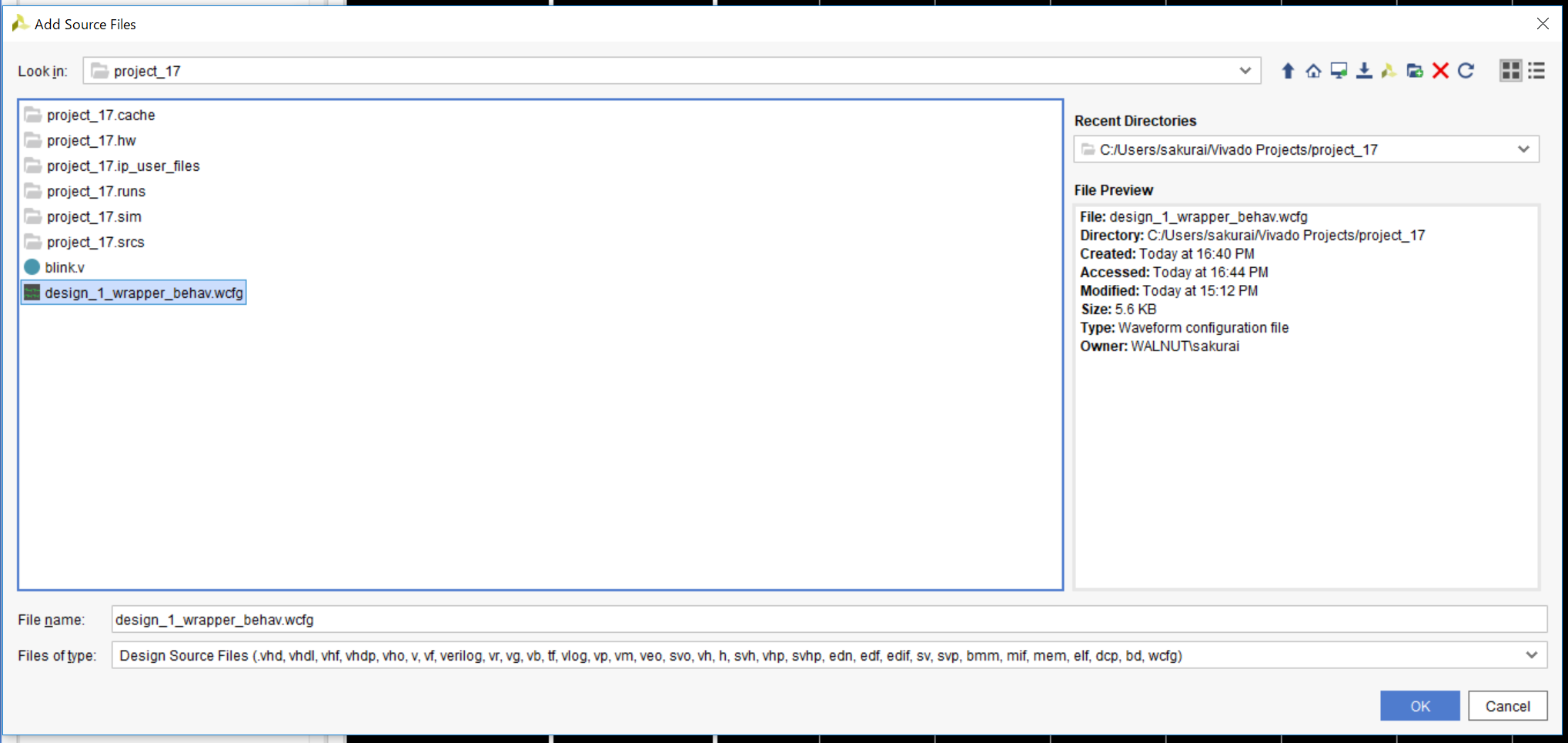

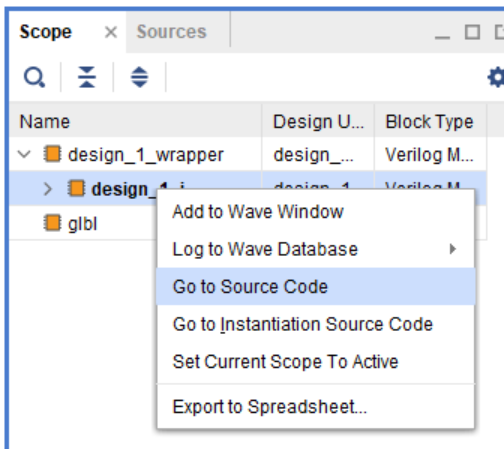

tclウインドウから入力するコマンドを示します。

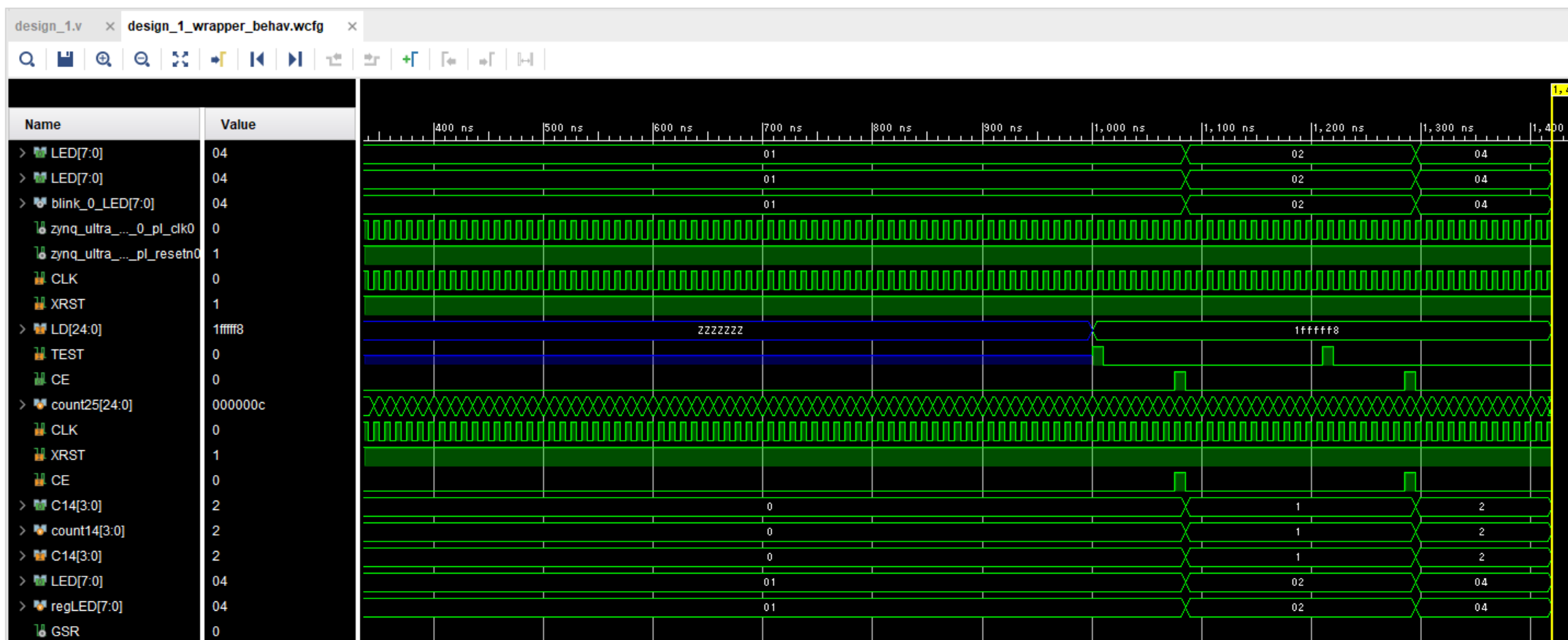

add_force {/design_1_wrapper/design_1_i/blink_0/inst/count25/LD} -radix hex {1fffff8 0ns}

add_force {/design_1_wrapper/design_1_i/blink_0/inst/count25/TEST} -radix hex {1 0ns}

run 10 ns

add_force {/design_1_wrapper/design_1_i/blink_0/inst/count25/TEST} -radix hex {0 0ns}

run 200ns

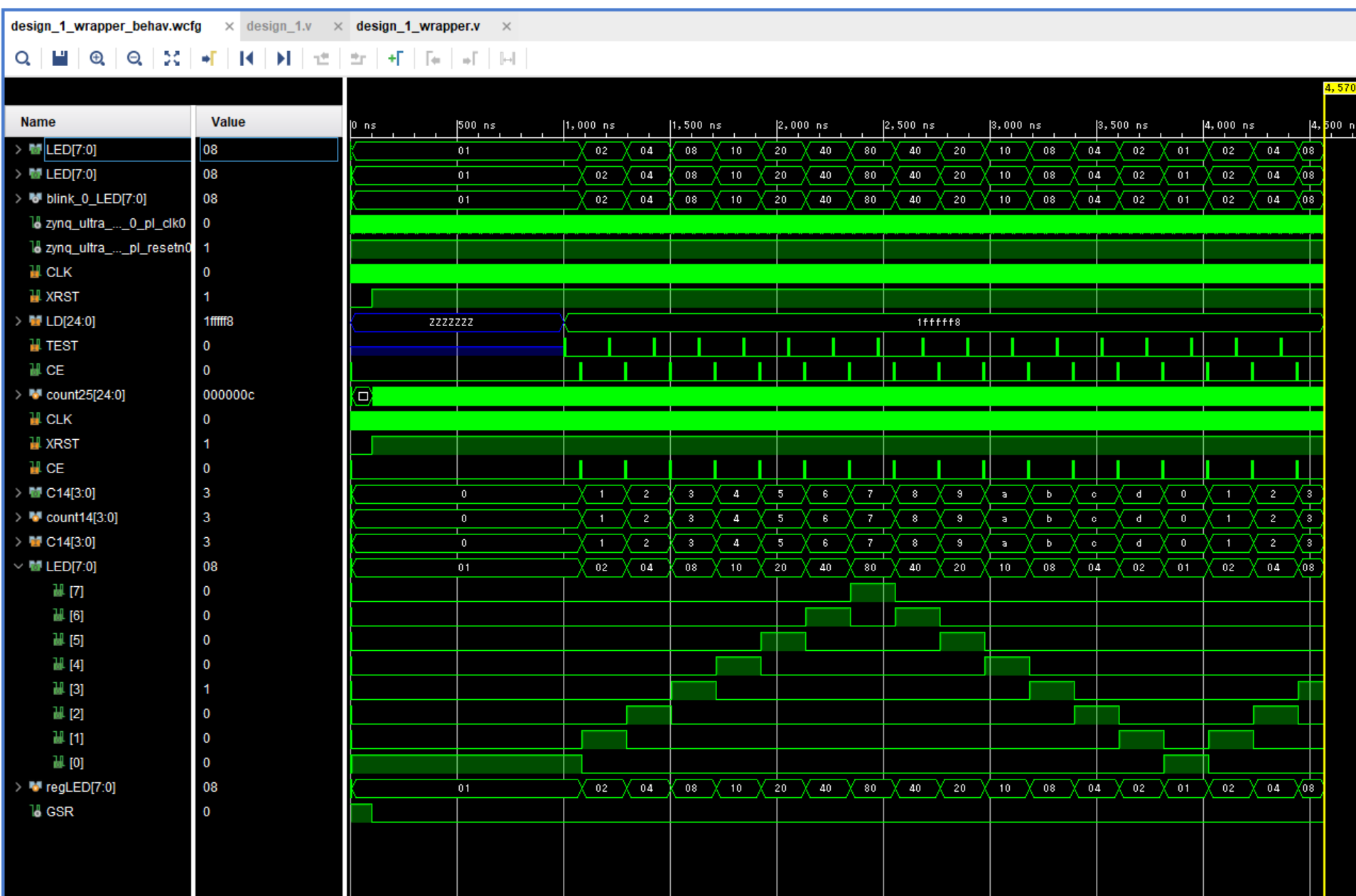

テスト回路自体は本来のパス(機能安全用語では主要機能)ではありませんが、このような長いカウンタのテスト容易化設計として常識の回路です。