|

28 |

Zynq UltraScale+ MPSoC |

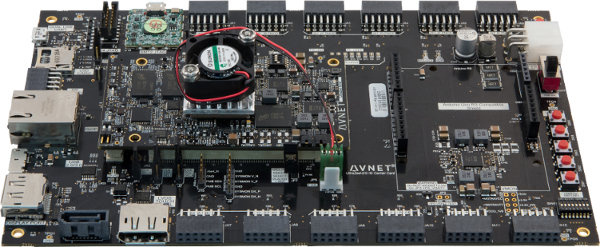

FPGAボード

プロセッサを含んだFPGAボードを入手しましたので、お約束のLED点滅を実験してみたいと思います。 まず、FPGAは、XilinxのZynq UltraScale+ MPSoCという部品で、ARM Cortex A53のクアッドコアとARM Cortex R5のデュアルコアを内蔵しています。

ボードの詳細は以下にあります。 http://microzed.org/product/ultrazed-eg-starter-kit

ベースボードとメザニンボードから構成されており、ベースボードの資料は、 http://picozed.org/product/ultrazed-eg-io-carrier-cardに、 メザニンボードの資料は http://microzed.org/product/ultrazed-EGにあります。

メザニンボード上にFPGA、SDRAM、Flash等が搭載されており、ベースボード上には各種高速インタフェースが搭載されています。

開発環境

最近のFPGAの開発環境の進歩はいちぢるしく、従来は高価なEDAツールが無償で使えるようになりました。XilinXが無償で提供しているVivado HLx WebPackが、上記FPGAの開発ツールです。このツールには論理合成ツール、配置配線ツール、論理シミュレータ等が含まれます。特に、最近は高位合成ツールまで無償で使用できるので、隔世の感があります。高位合成までいかなくても強力なIPインテグレータが搭載されており、従来はRTL設計するしかなかった各種AXIインタフェースに関して、単にブロックをドロップし、auto connectをクリックするだけで自動結線する、強力な機能を持ちます。

Vivadoの入手はXilinxにアカウントを作成する必要がありますが、無償ですので以下からwebpackを入手してください。 https://japan.xilinx.com/products/design-tools/vivado/vivado-webpack.html

IP Integrator

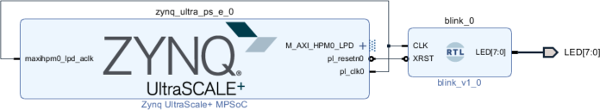

IPインテグレータでブロック設計をした結果を以下の図に示します。FPGA全体はPS(Processor System)部とPL(Plogrammable Logic)部から構成されていますが、ZynqはFPGA全体ではなく、PS部のみです。blinkはRTLで設計するブロックで、PL内に配置します。

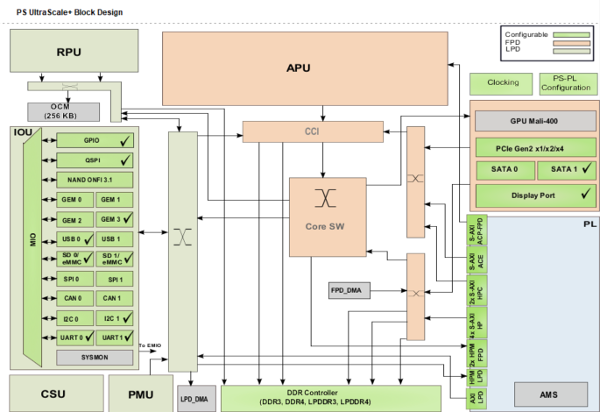

Zynqをダブルクリックすると以下の図のようにブロック図が現れます。APUはApplication Processing Unit、RPUはRealtime Processing Unitの略で、それぞれCA53、CR5及びそのキャッシュシステムを意味します。今回はハードのみで動作する回路を設計するため、プロセッサは全く使用しません。

Leave a Comment