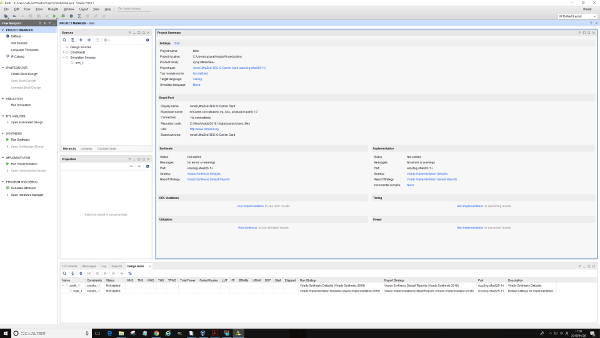

Vivadoの操作

- シミュレーション

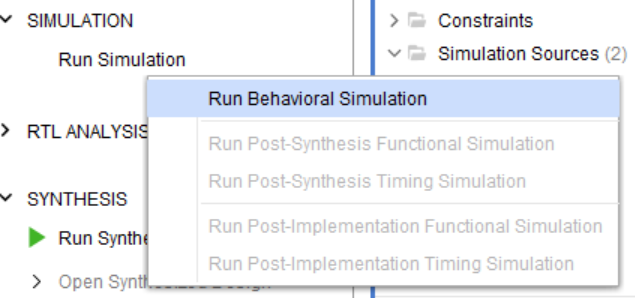

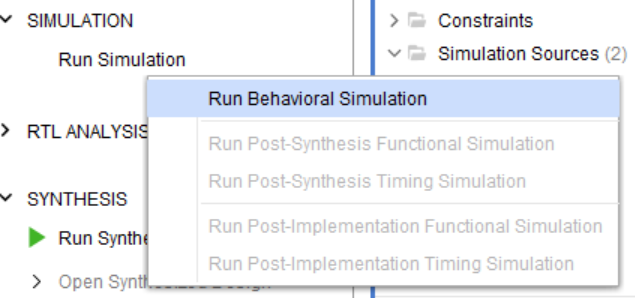

シミュレーションにより、動作が正しく行われるかを確認します。左のFlow NavigatorからSIMULATIONの下のRun Simulationをクリックし、Run Behavioral Simulationを実行します。

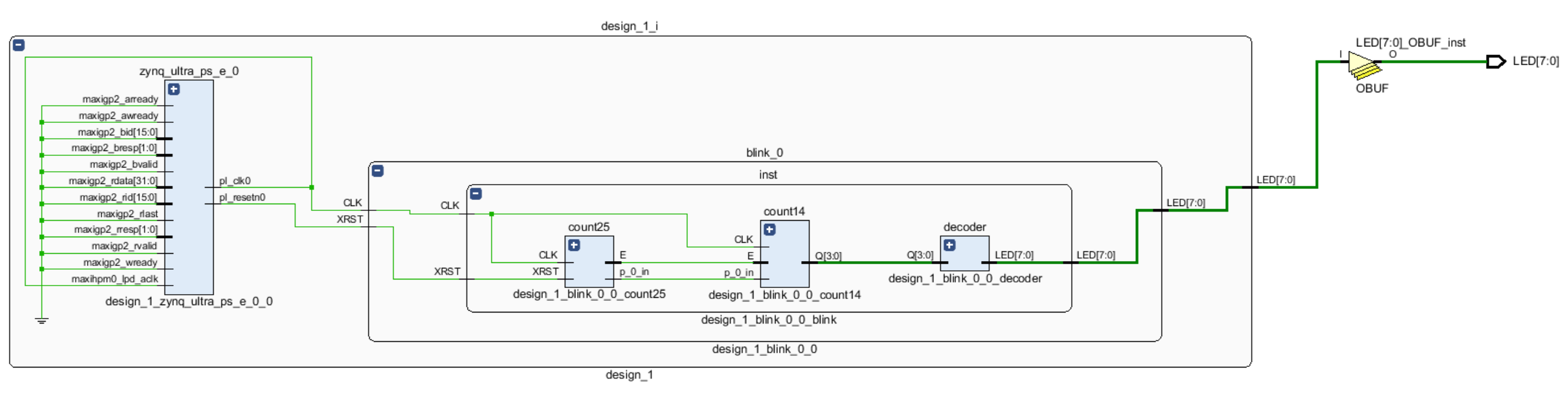

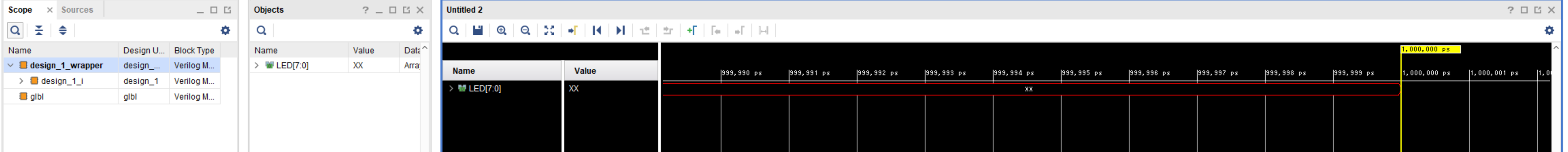

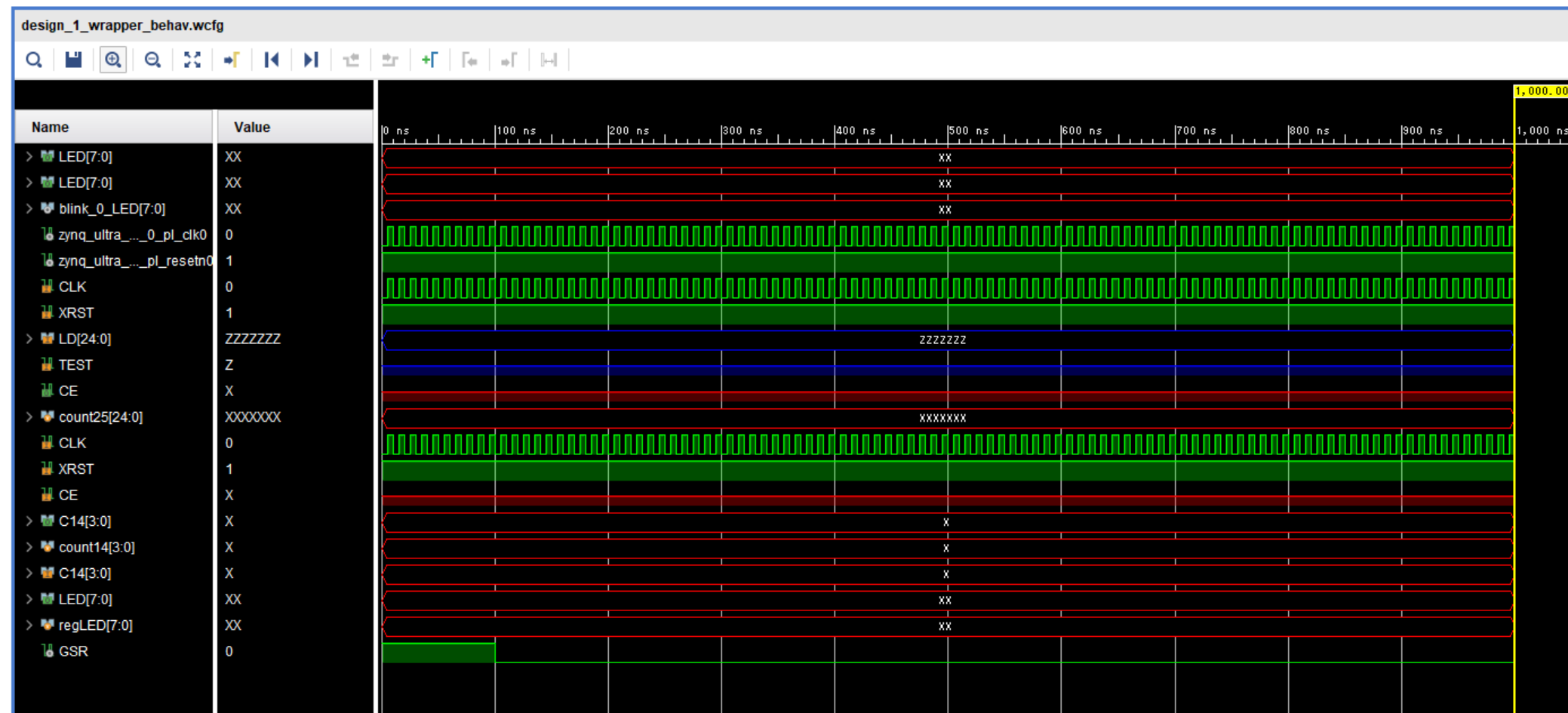

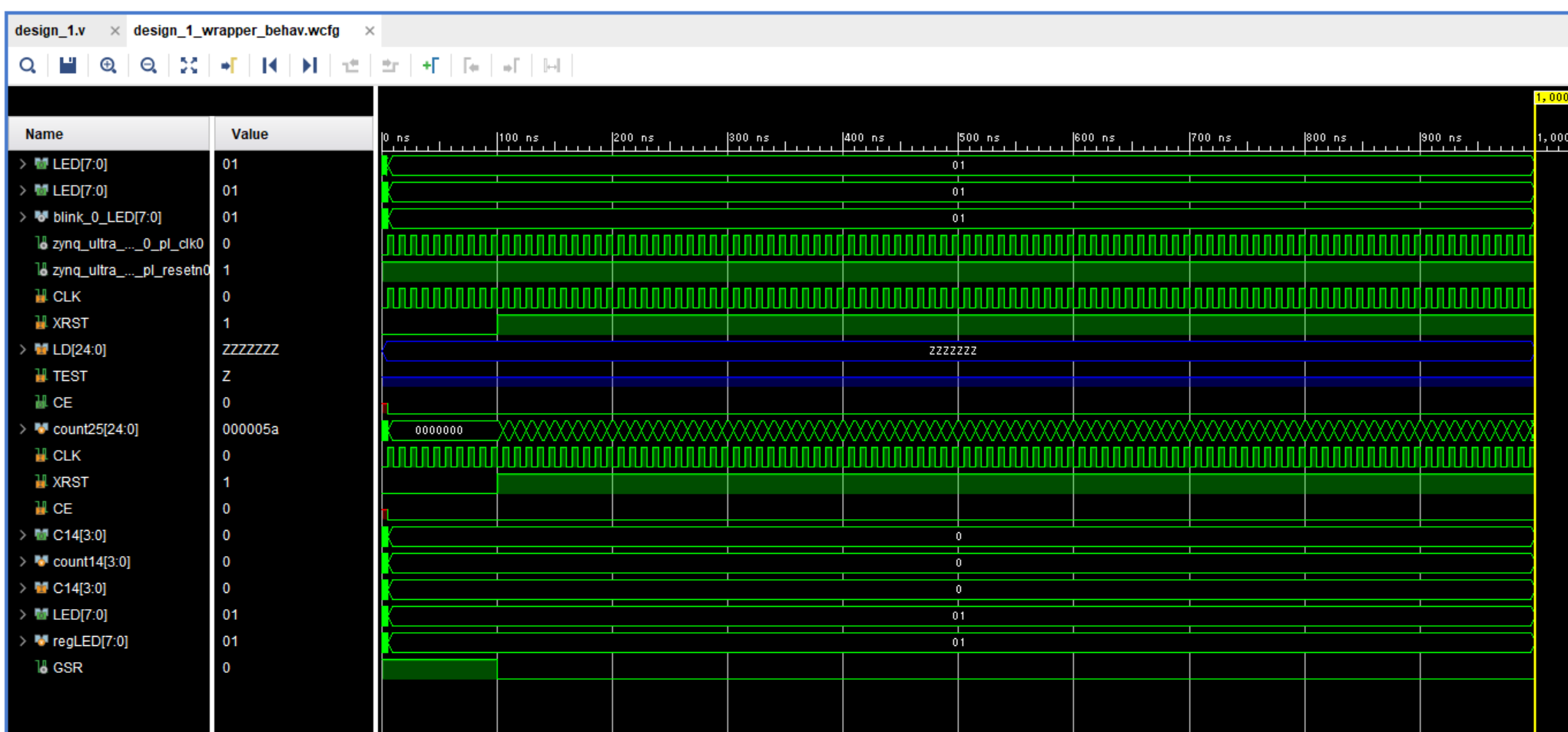

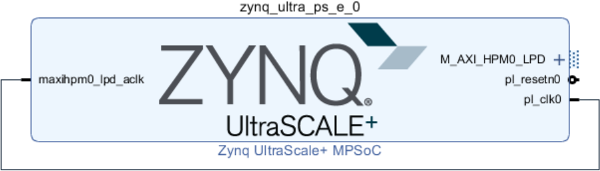

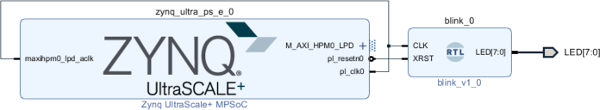

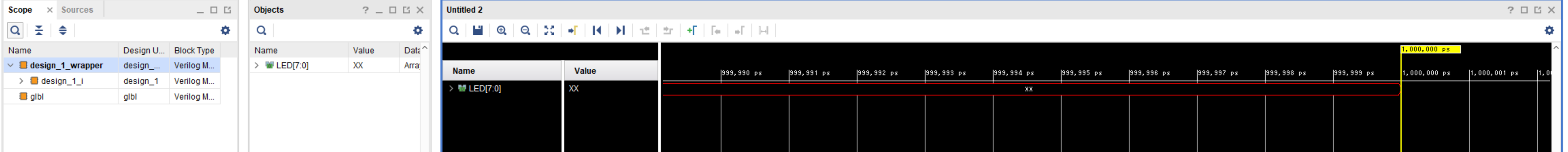

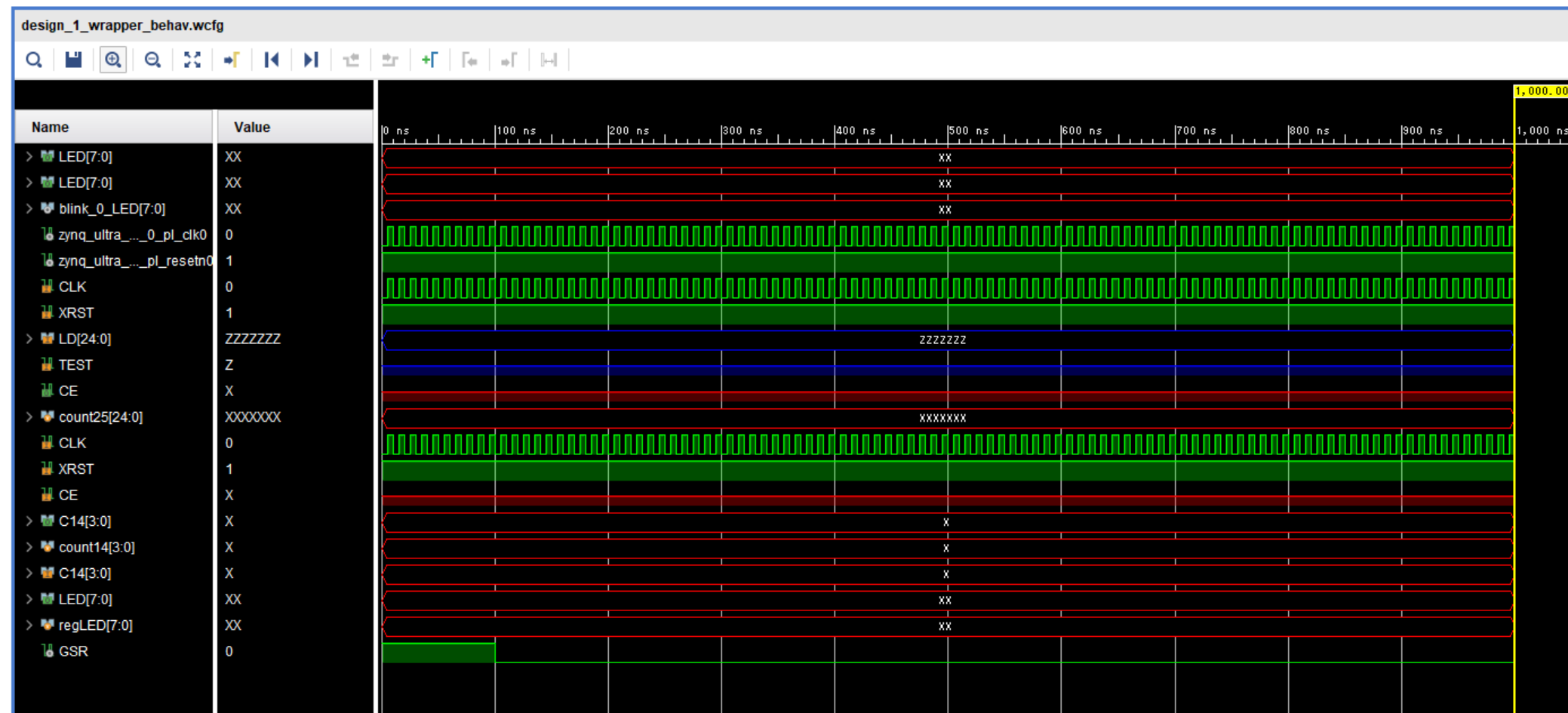

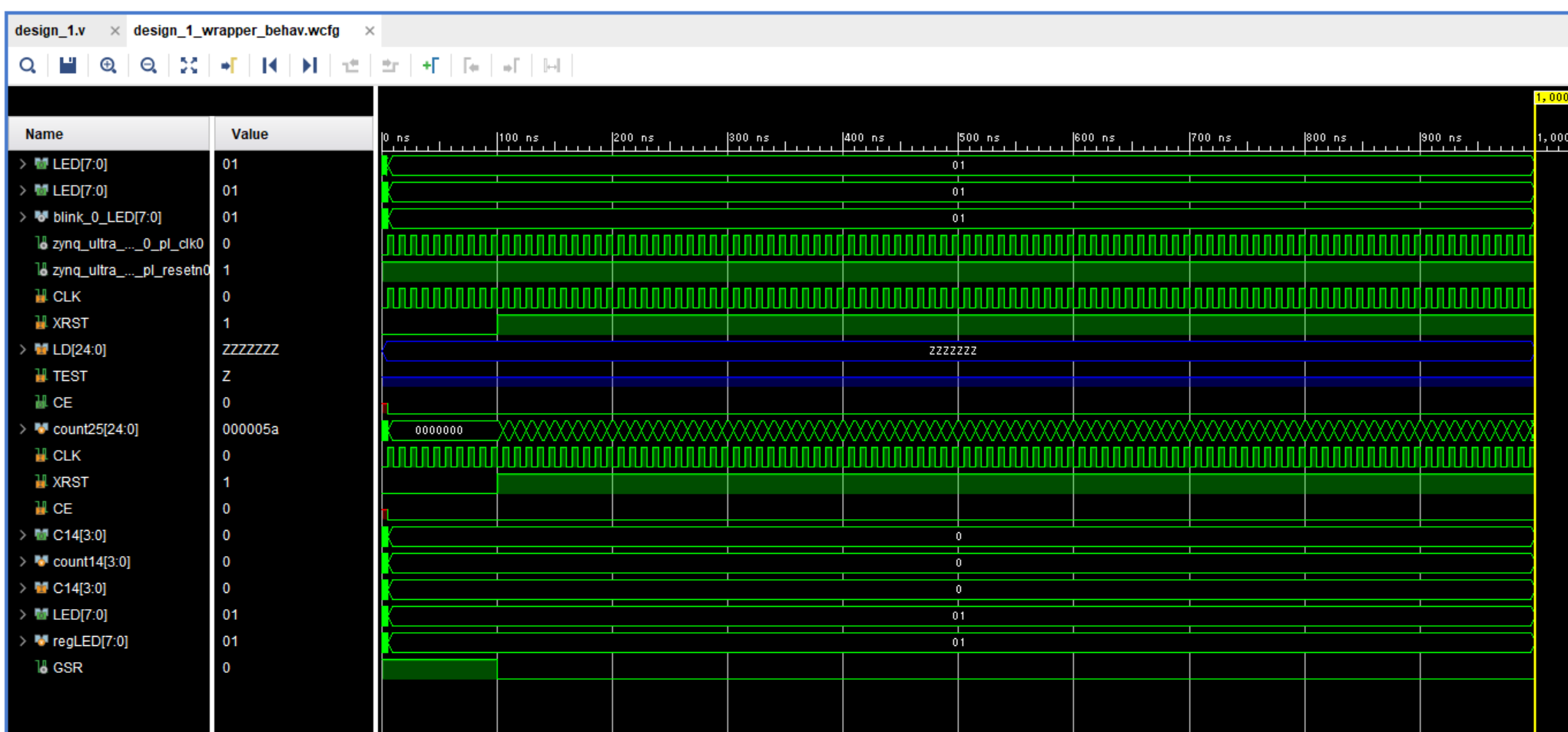

しばらく待つと以下のようにシミュレーションが動作するが、リセットがうまく入っていないため、カウンタ値が不定となっています。PSからのリセットはソフトで指示しないとかからないのかもしれません。従って、シミュレーションで動作するようにワークアラウンドを行います。

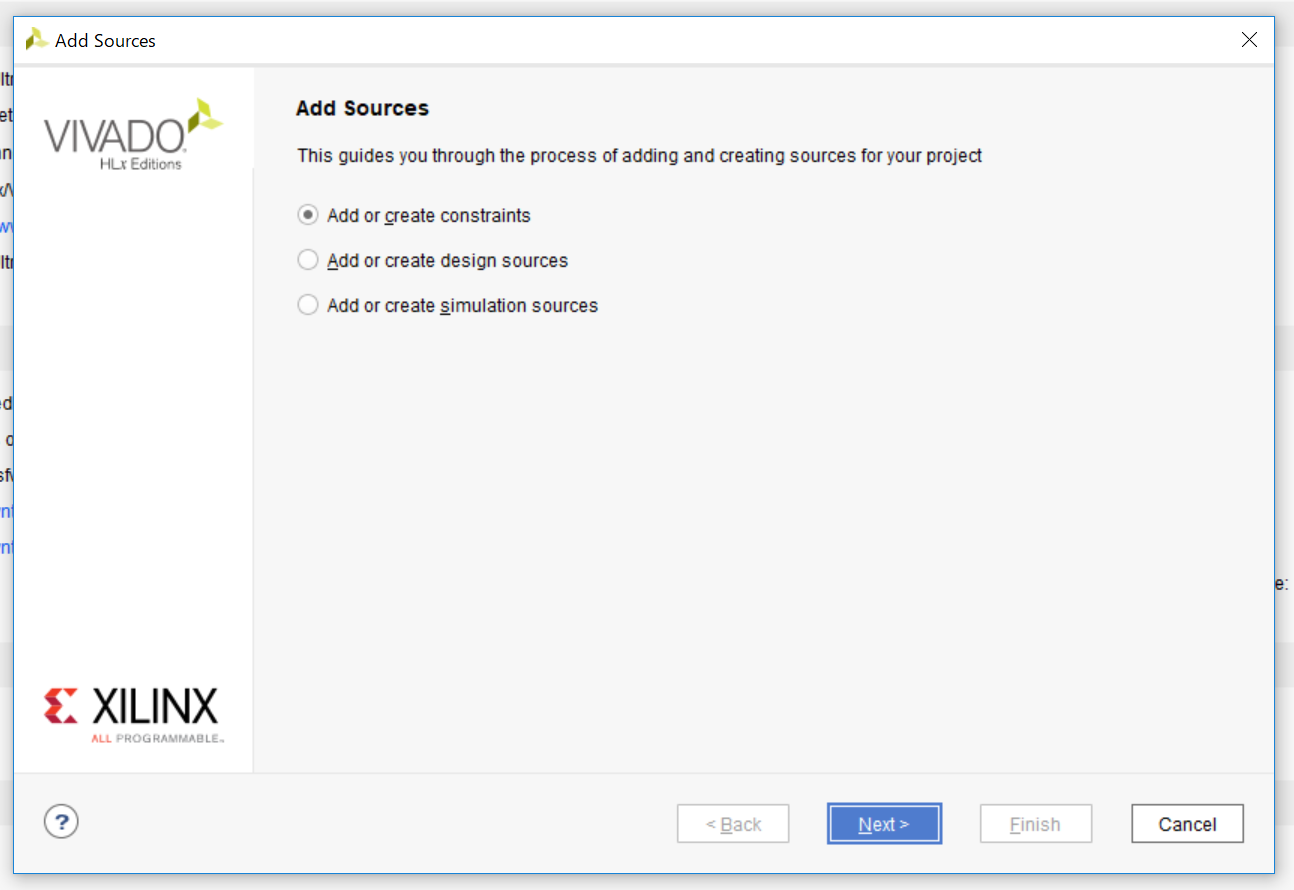

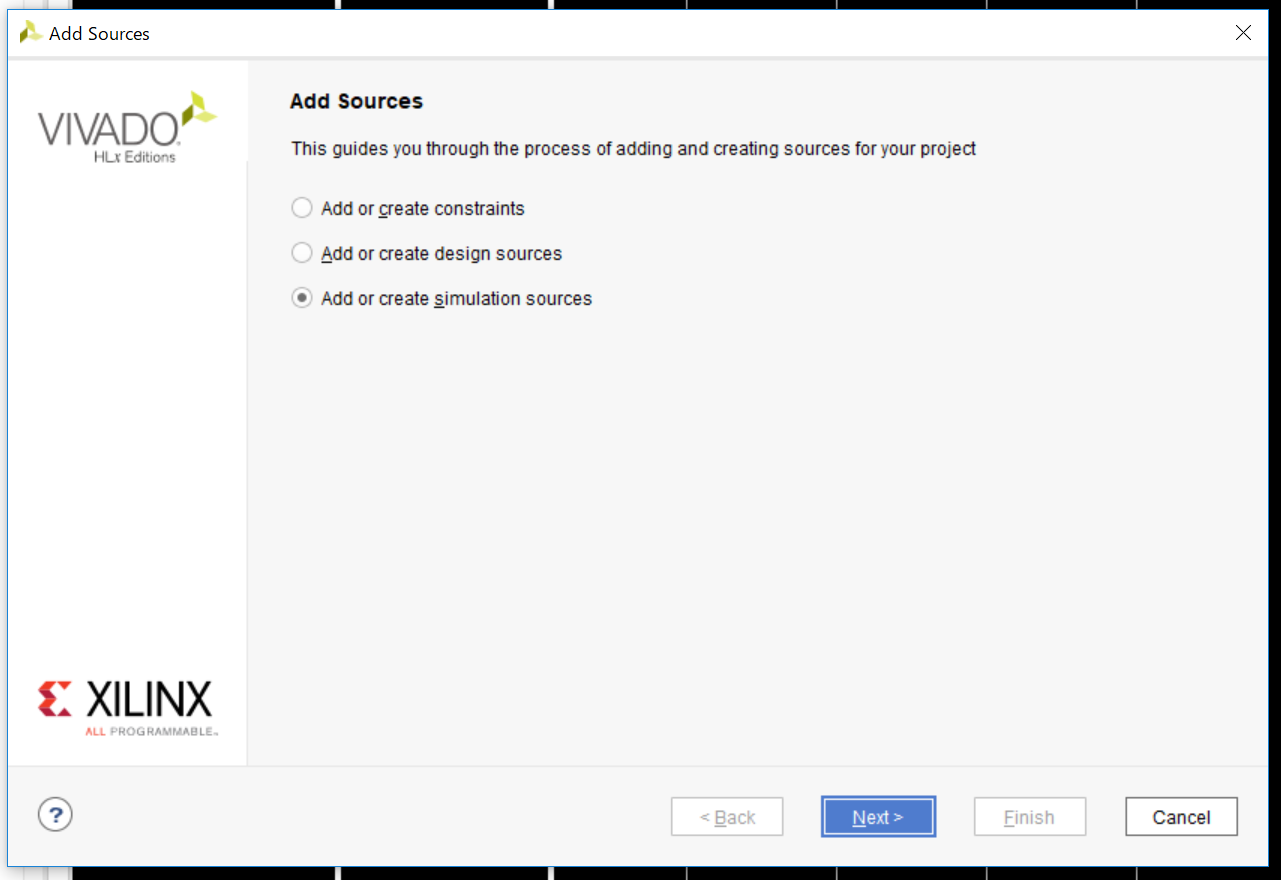

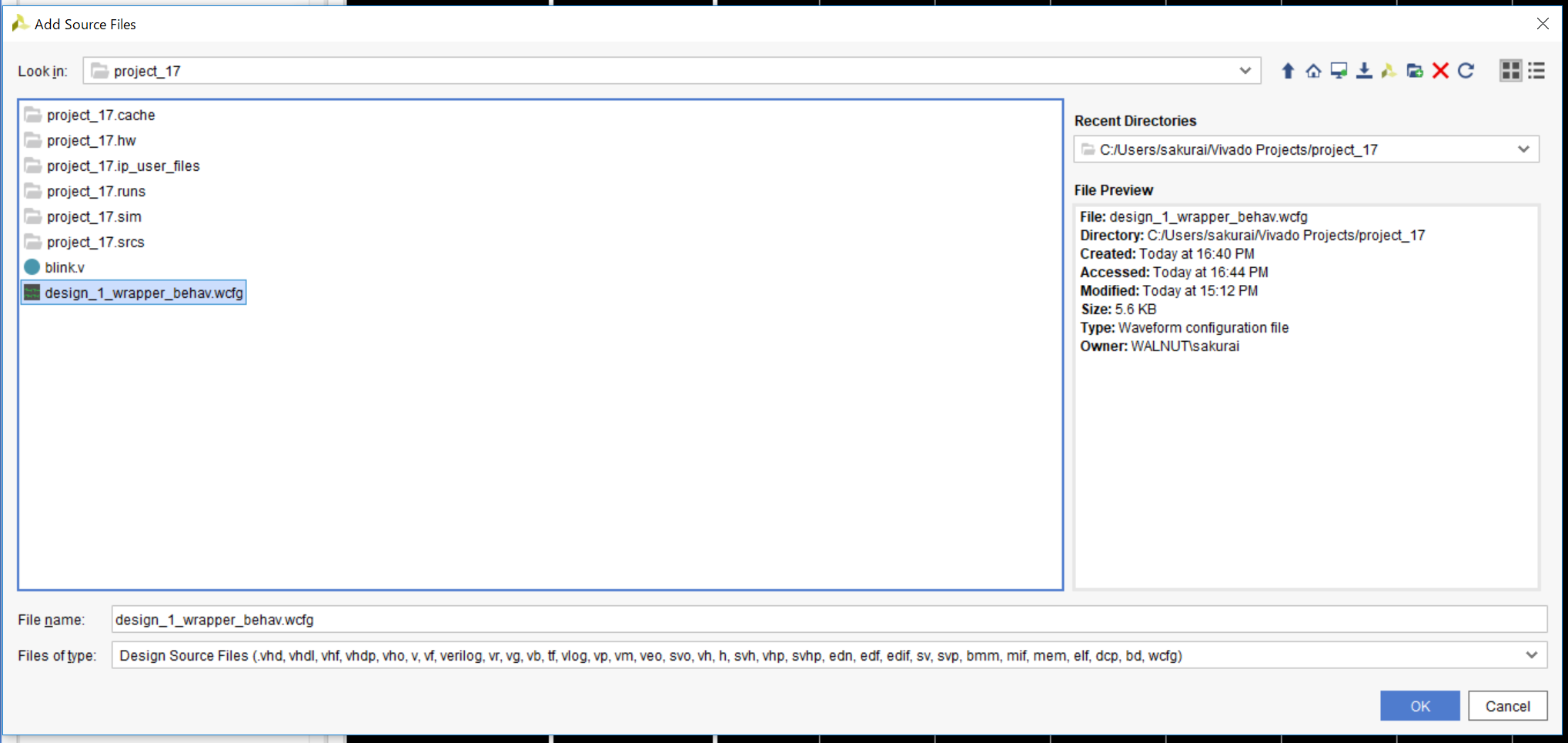

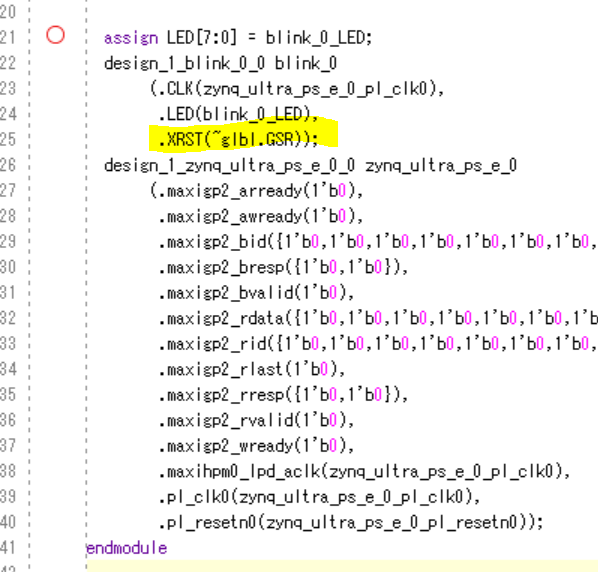

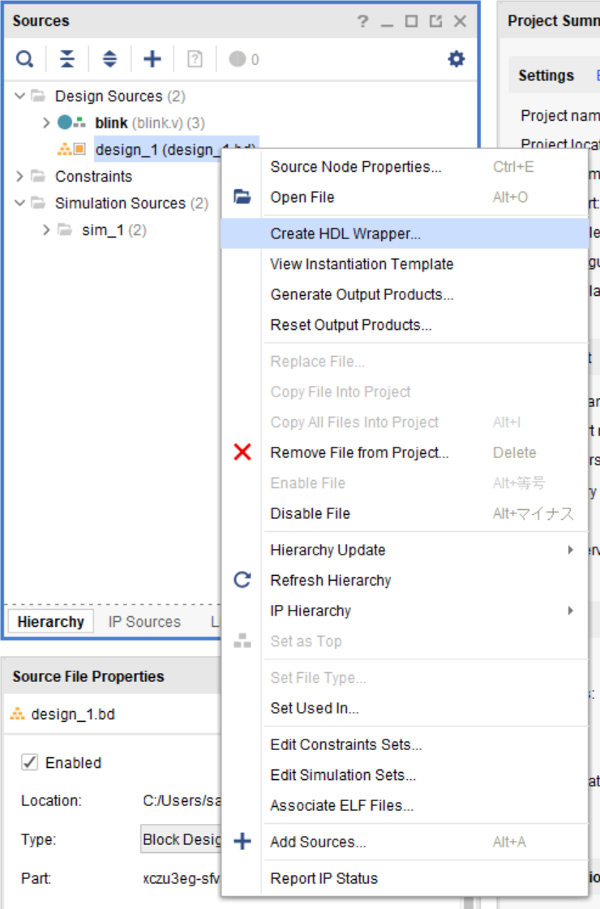

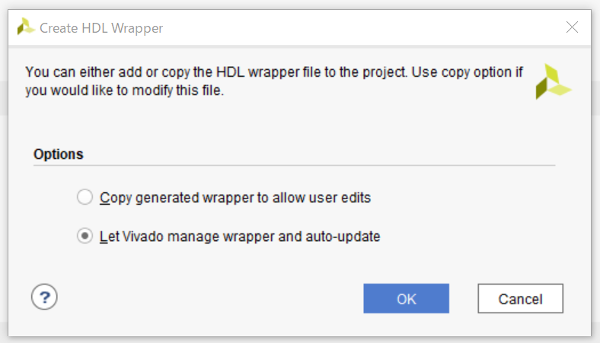

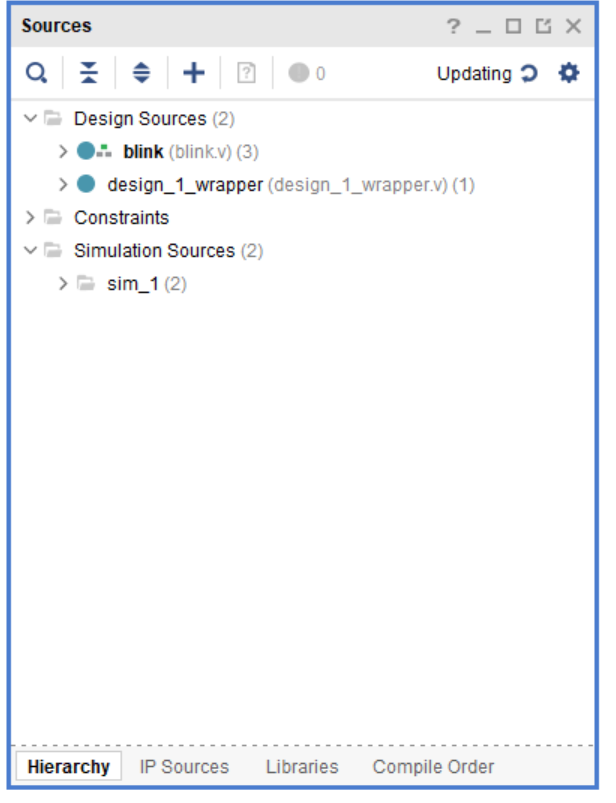

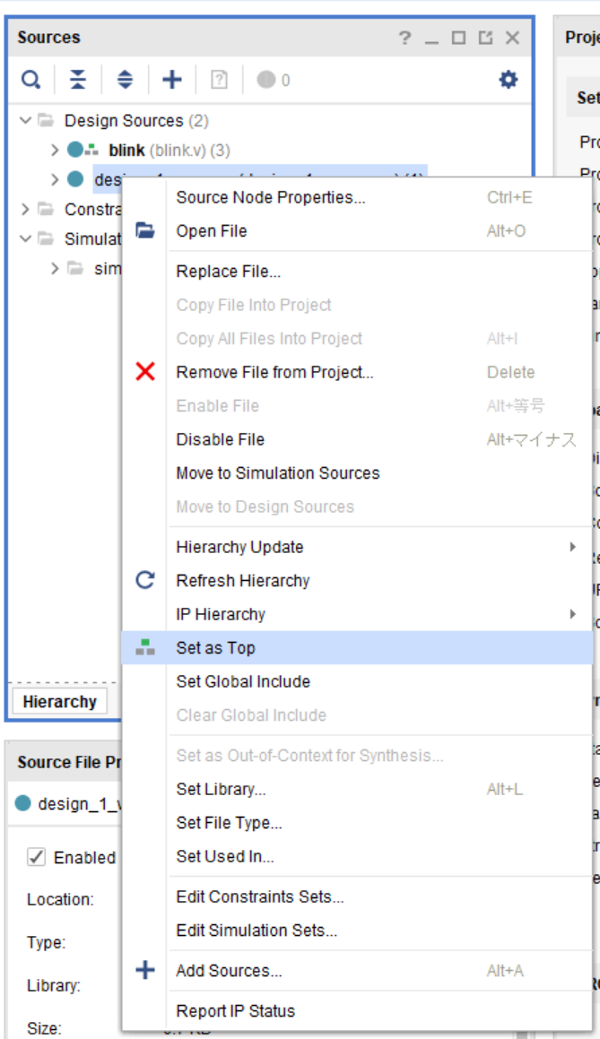

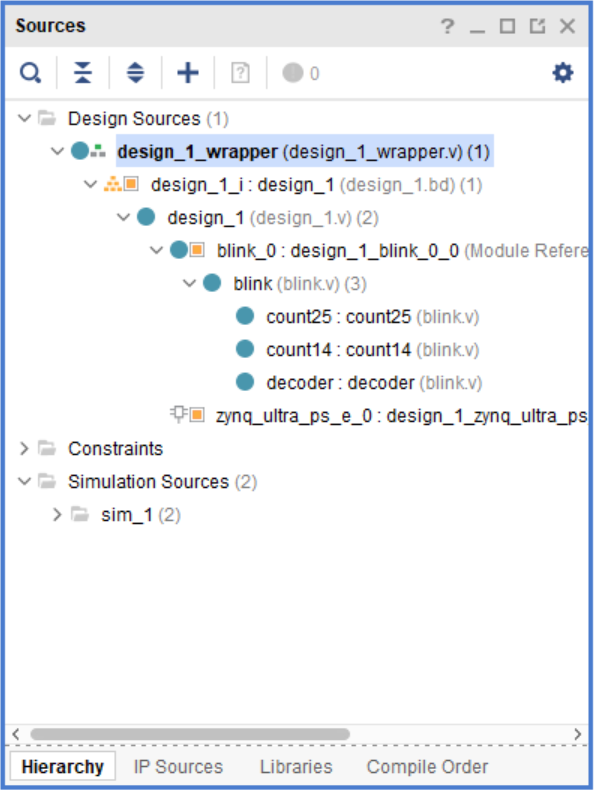

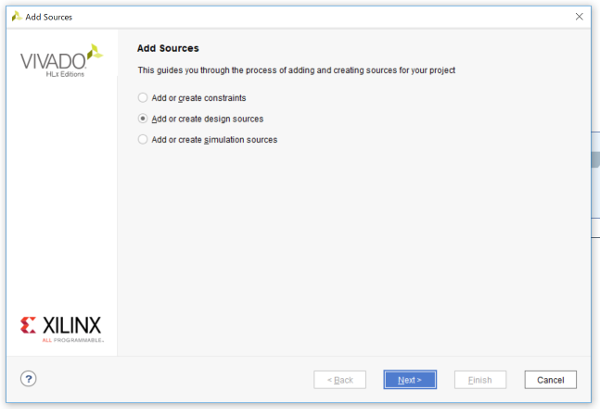

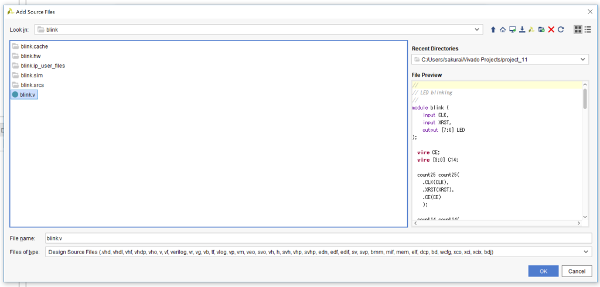

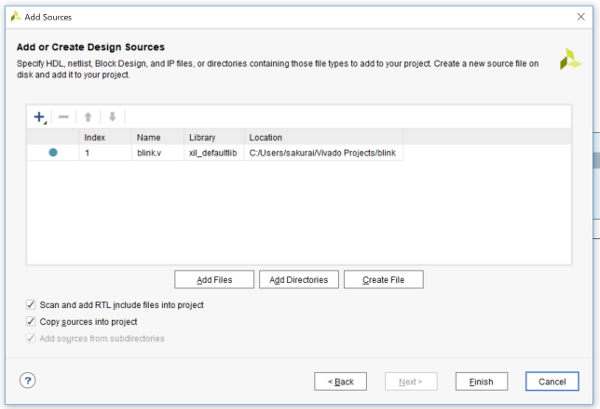

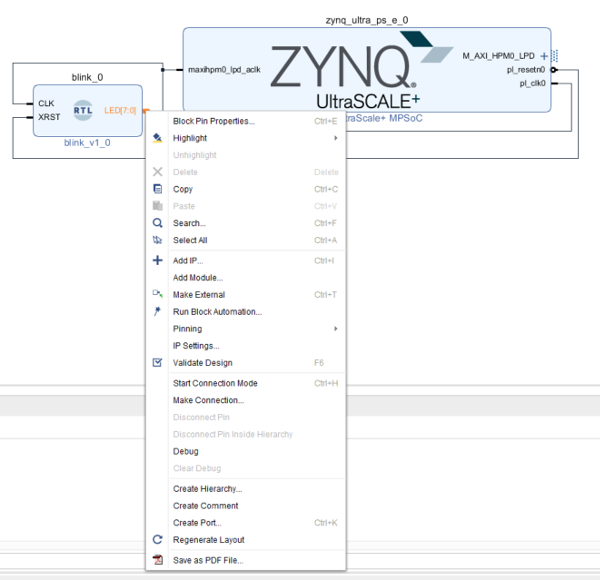

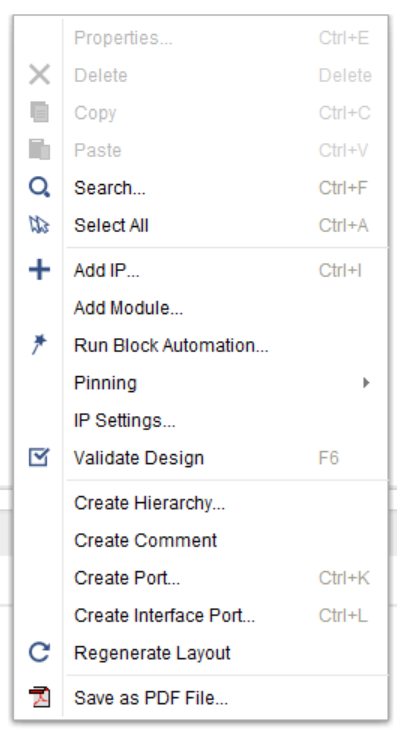

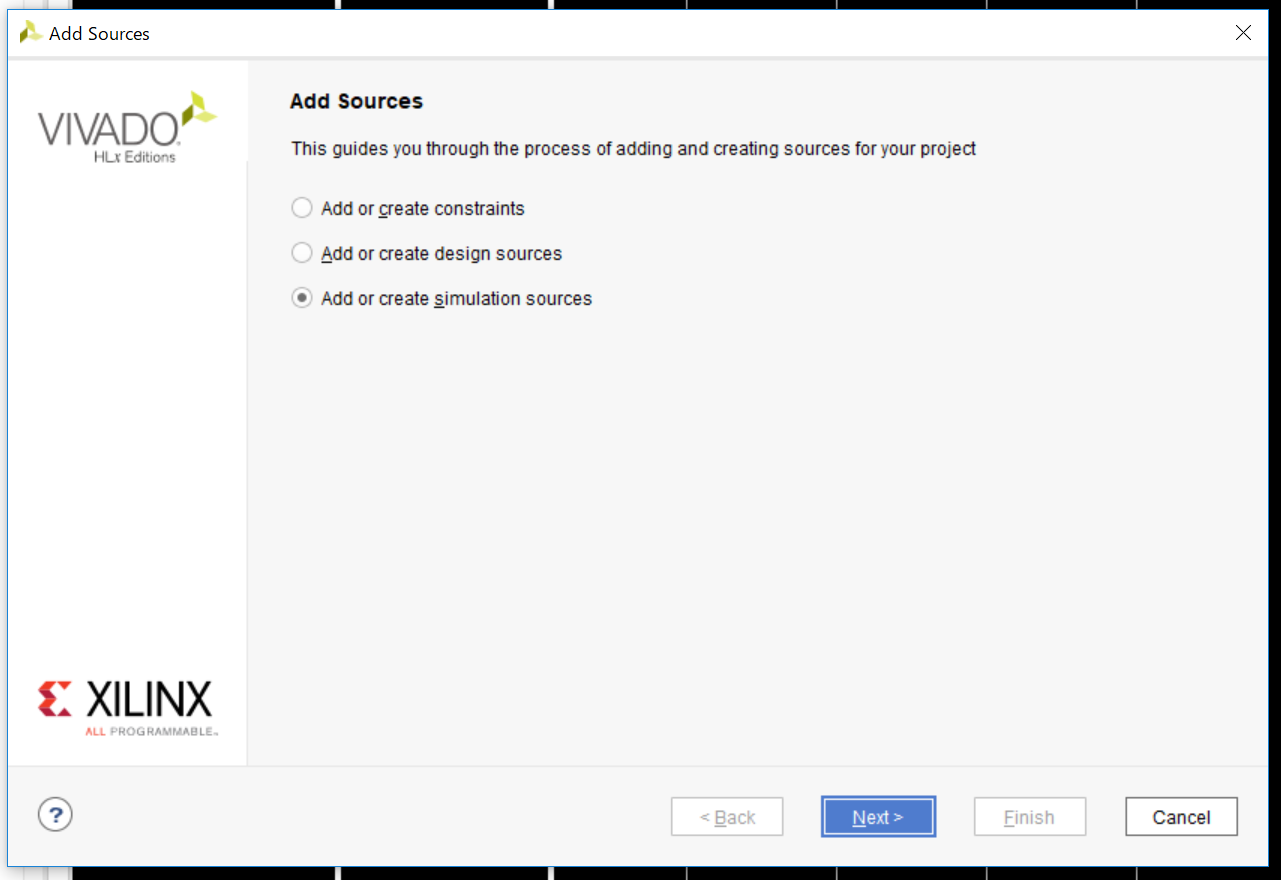

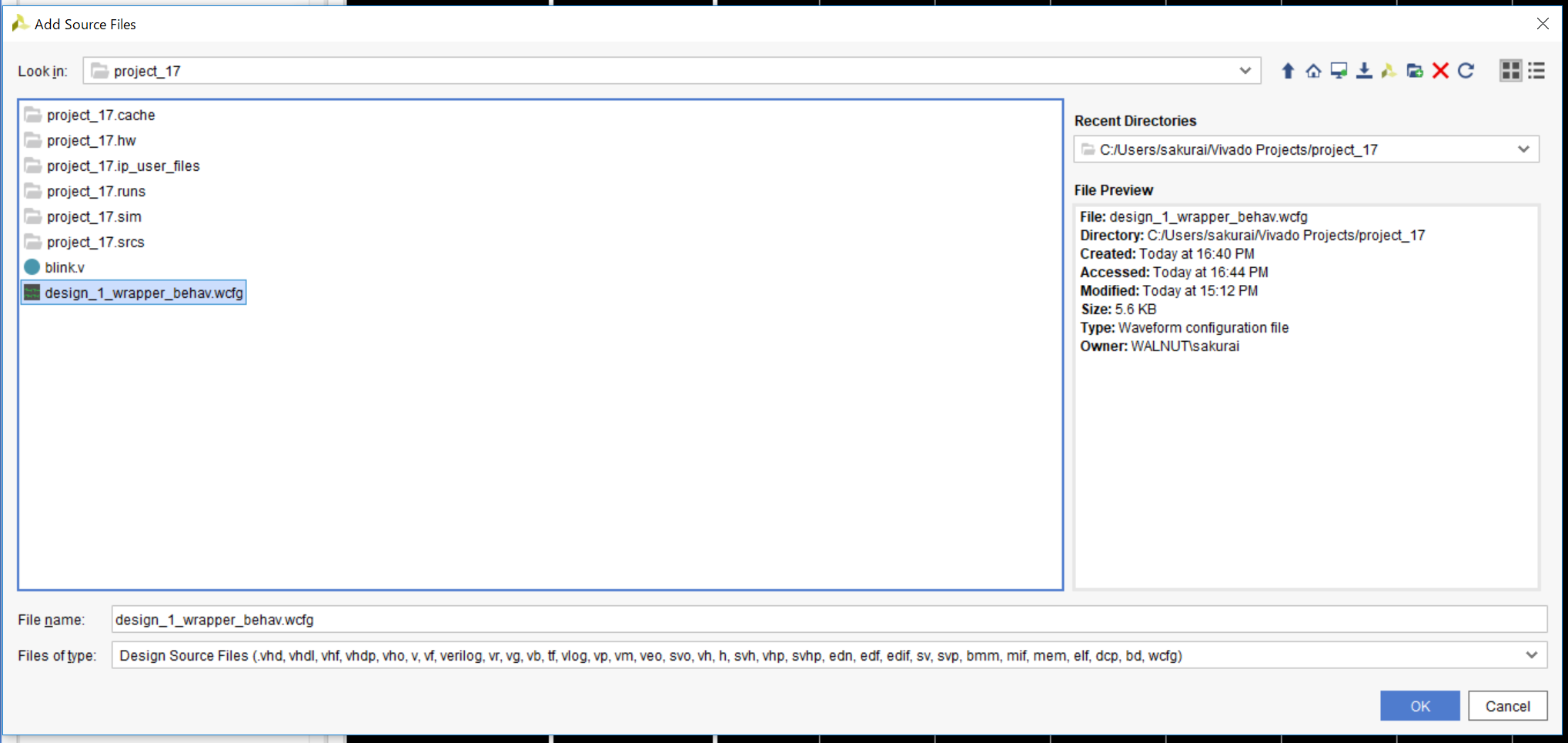

まず、ソースを以下のように開きます。

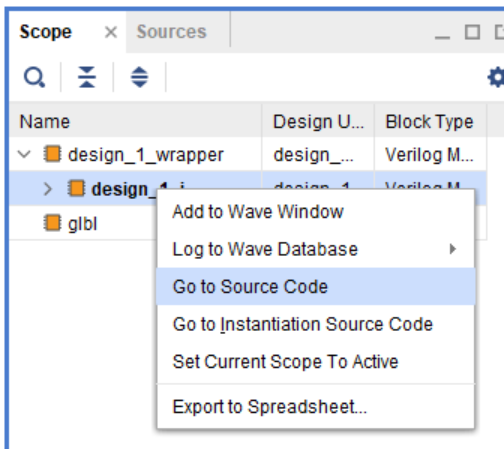

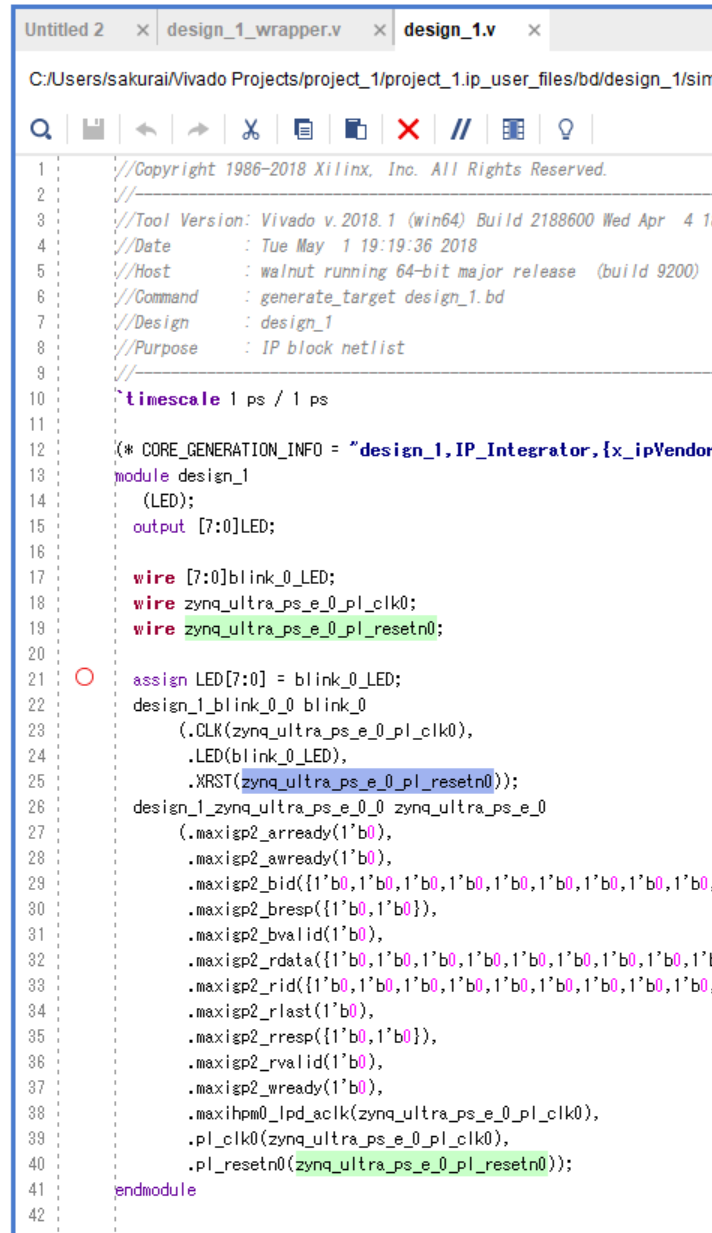

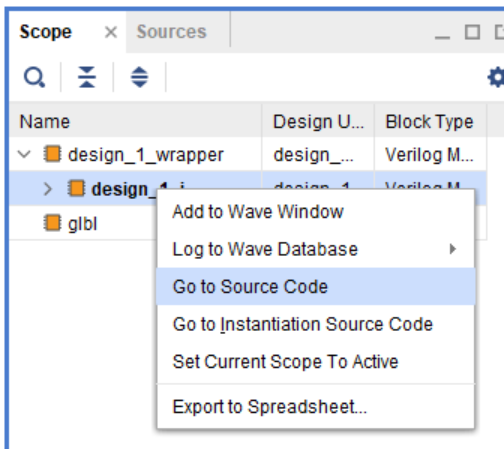

design_1の階層でGoto Sourceをクリック。

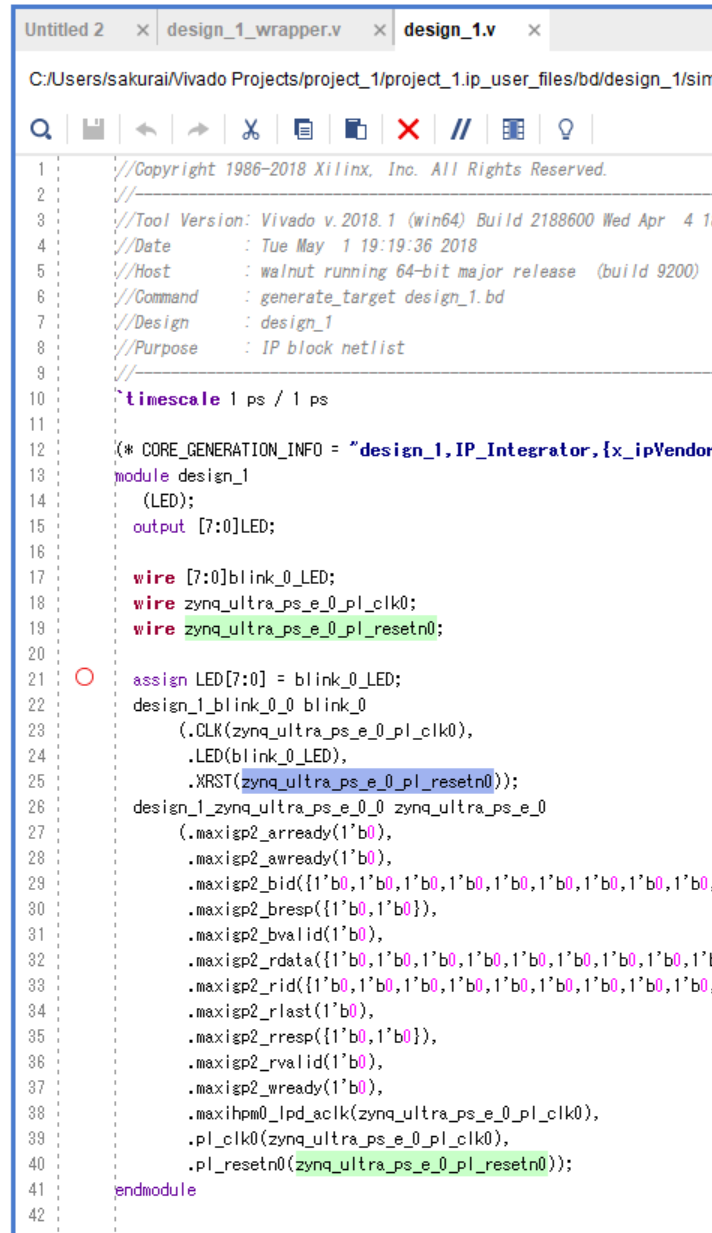

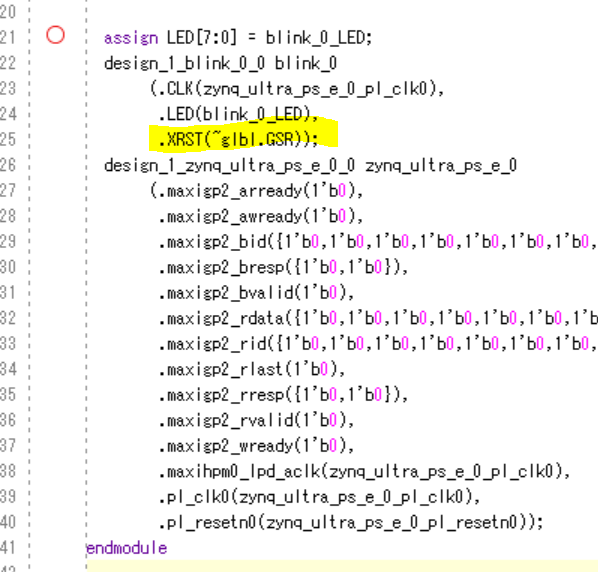

25行目の、blinkモジュールのXRST端子をPSからのリセットを削除し、~glbl.GSRをつなぎます。glblモジュールのGSRは100nsのみtrueとなる信号であるため、反転してXRST端子に入力します。

以下の図のようにリセットが正常に入り、回路が動作しました。

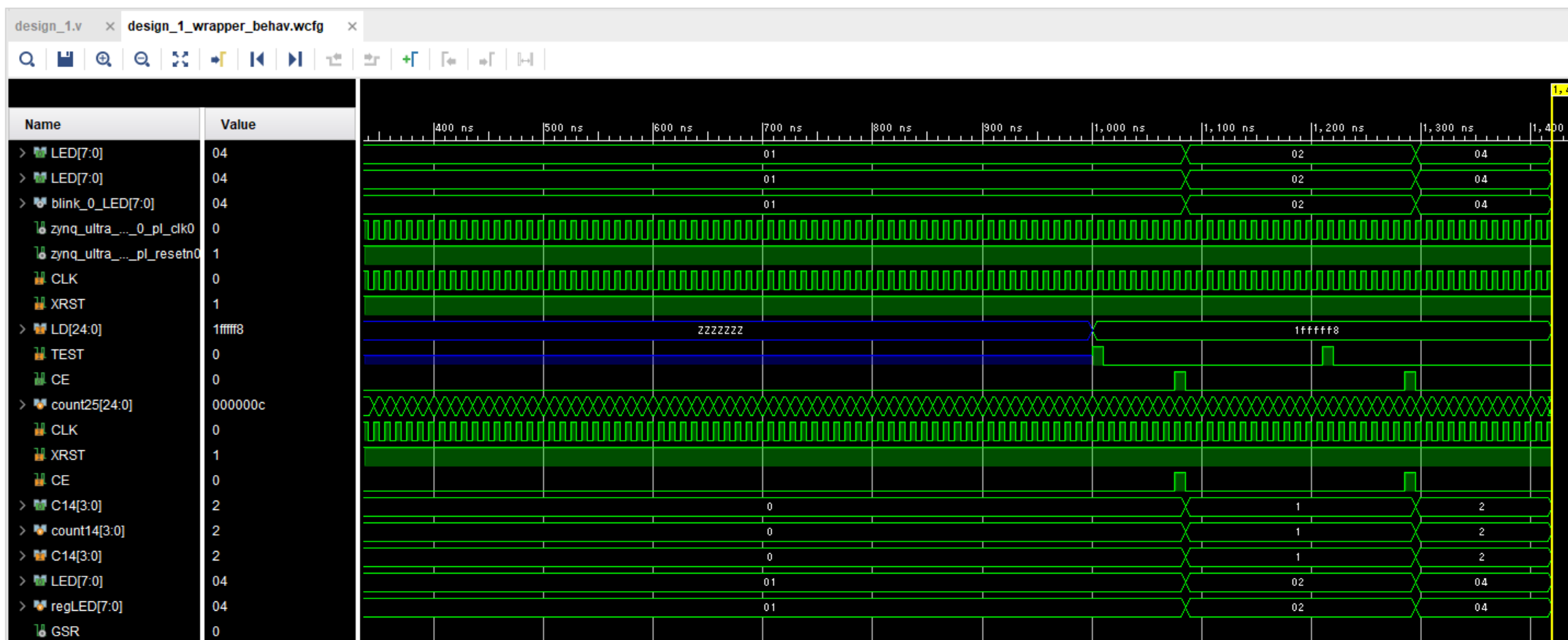

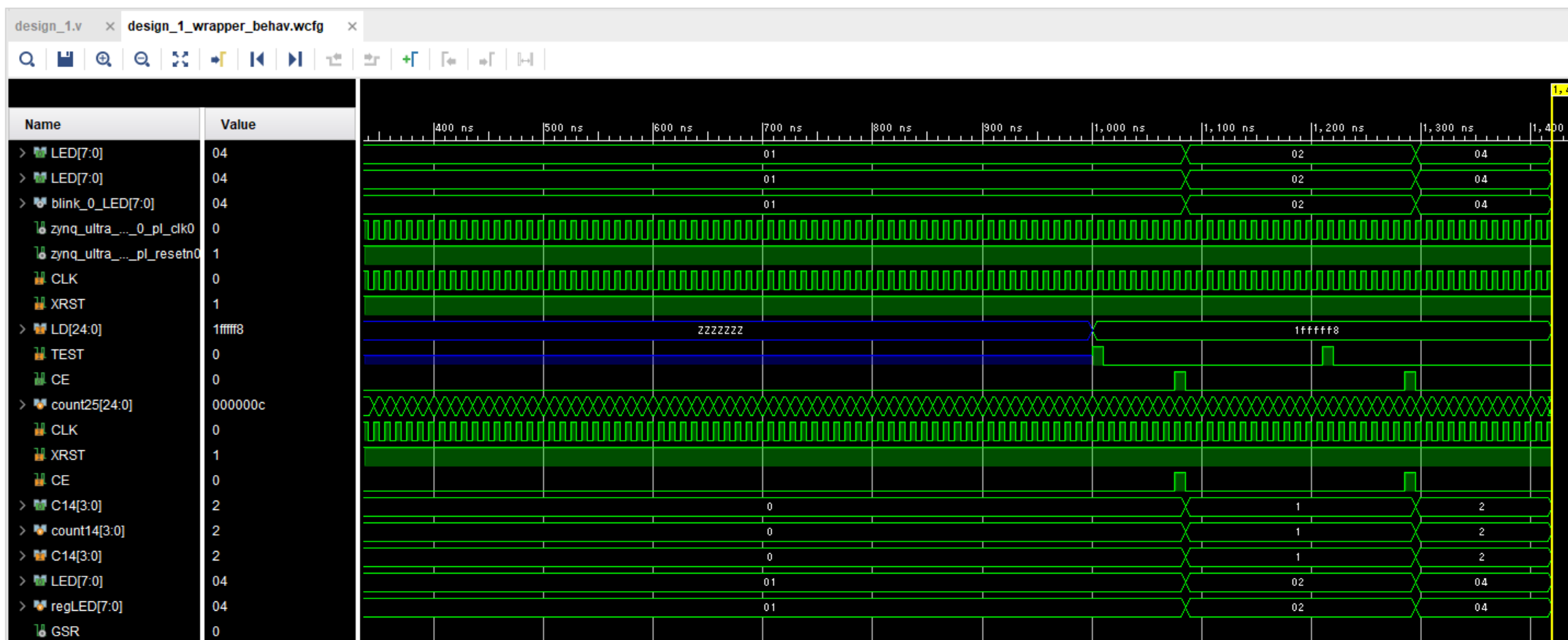

このままクロックを入れ続けても動作しますが、シミュレーション時間が非常にかかるため、短縮を行います。25bitカウンタを単純にカウントするのではなく、MAX値に近い値をロードした後にカウントを進めます。具体的にはTEST信号をtrueにし25bitカウンタにMAX値に近い値(例えば0x1ffff8)をロードします。

この前提としてRTLの25bitカウンタを、TEST信号のtrueにより任意の値をロードできるように修正する必要があります。テスト回路を用いない方法としては、カウント値に強引に上記値をforceするやり方もあります。テスト回路は本番では不要であるため、こちらのほうが良いかもしれません。

tclウインドウから入力するコマンドを示します。

add_force {/design_1_wrapper/design_1_i/blink_0/inst/count25/LD} -radix hex {1fffff8 0ns}

add_force {/design_1_wrapper/design_1_i/blink_0/inst/count25/TEST} -radix hex {1 0ns}

run 10 ns

add_force {/design_1_wrapper/design_1_i/blink_0/inst/count25/TEST} -radix hex {0 0ns}

run 200ns

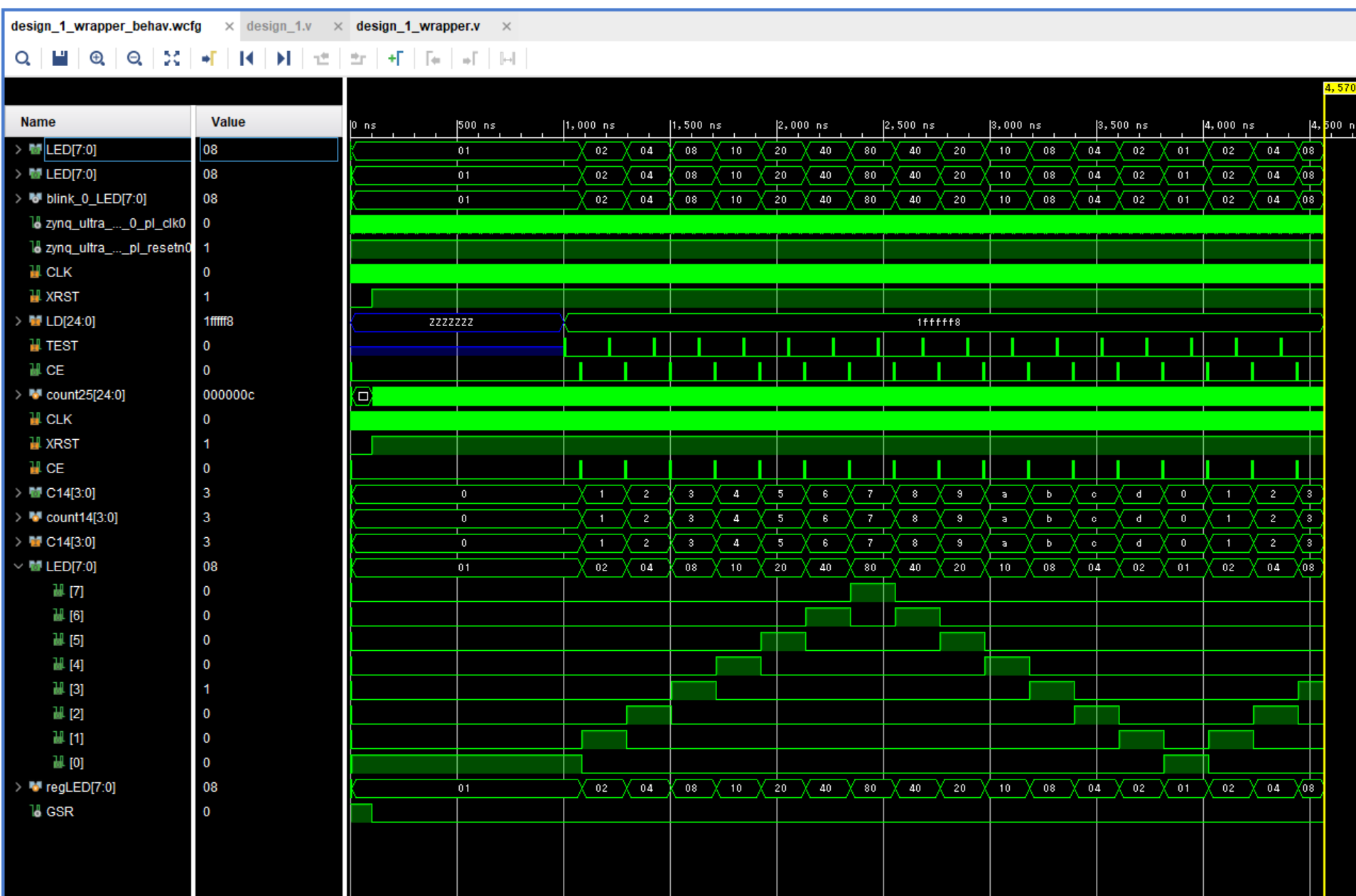

このように動作したので、14進カウンタがすべてカウントするまでこのコマンドを入力します。

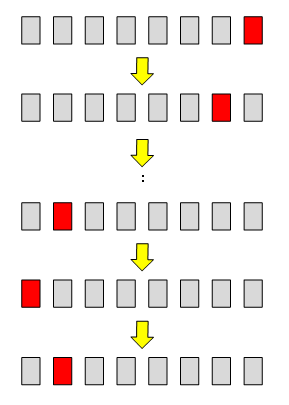

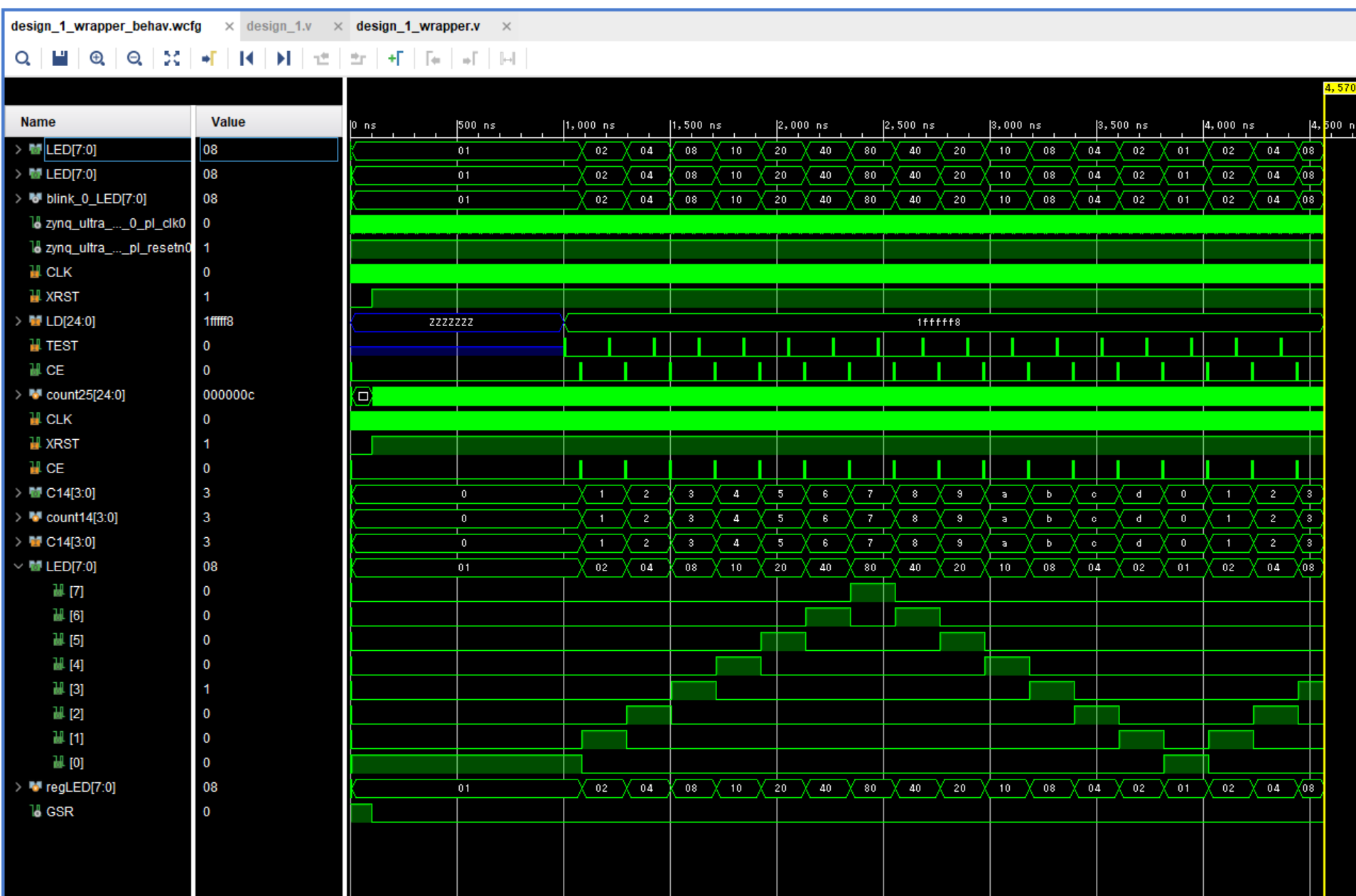

正しく14進カウンタが動作し、かつLEDパターンが要件に従ったふるまいのとおりデコードされているのがわかります。

テスト回路自体は本来のパス(機能安全用語では主要機能)ではありませんが、このような長いカウンタのテスト容易化設計として常識の回路です。

前のブログ

次のブログ

前のブログ

次のブログ