|

25 |

Lチカの実装 (8) |

Vivadoの操作

- 制約ファイル設定

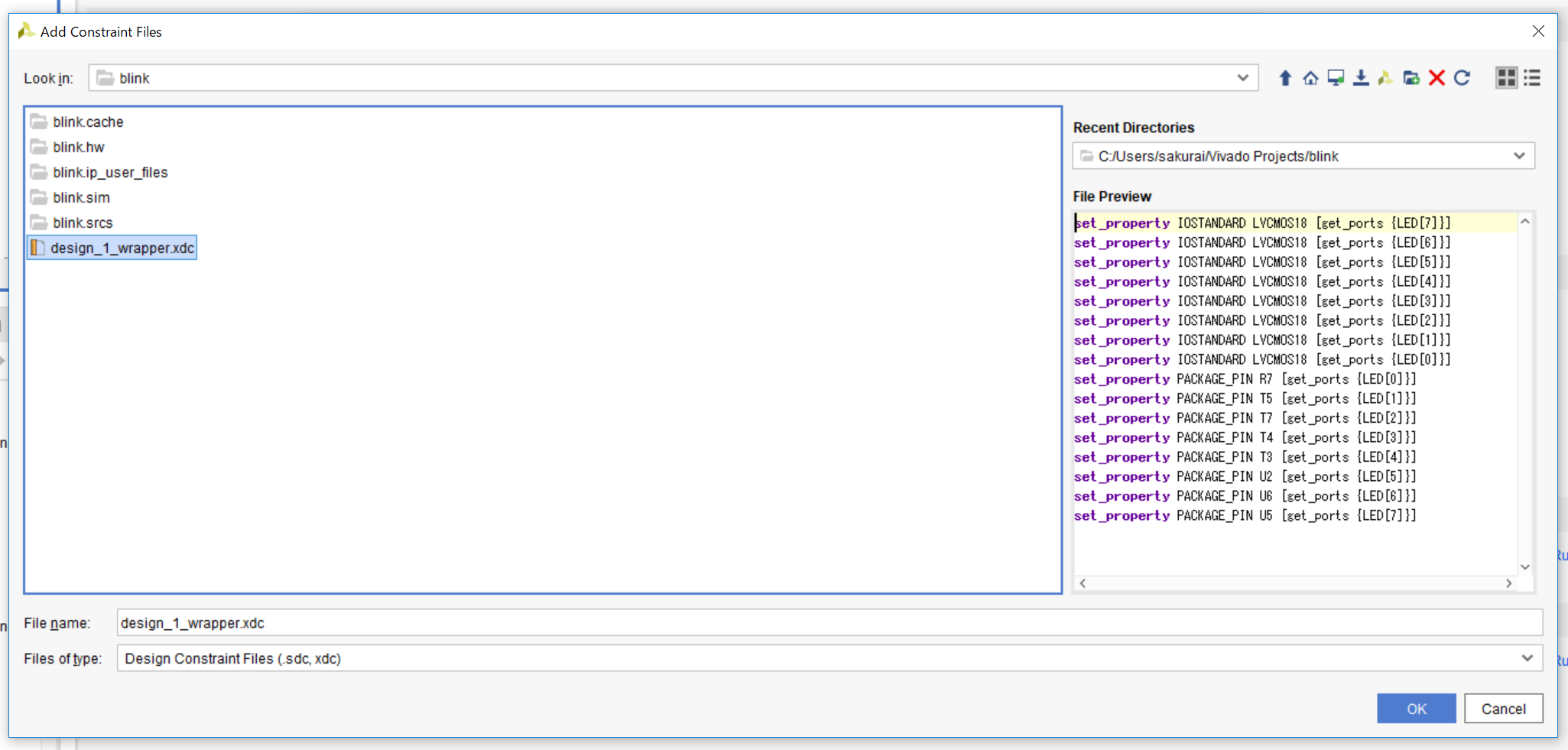

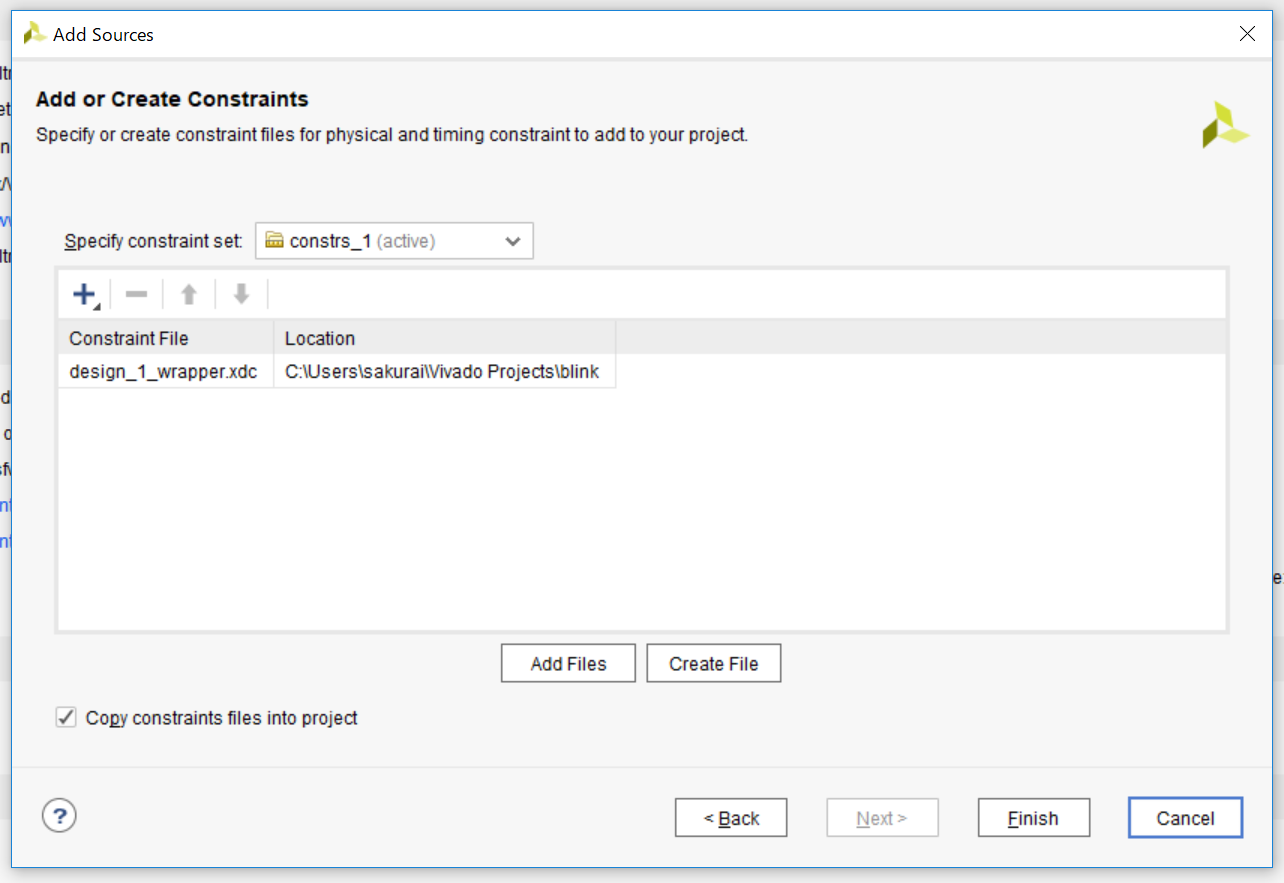

デザインの準備ができたので合成制約をかけます。制約の内容はLED端子に対するパッケージ端子の位置の決定と、LED端子のドライブ強度です。以下に制約ファイルの内容を示します。

set_property IOSTANDARD LVCMOS18 [get_ports [list {LED[*]}]]

set_property PACKAGE_PIN R7 [get_ports [list {LED[0]}]]

set_property PACKAGE_PIN T5 [get_ports [list {LED[1]}]]

set_property PACKAGE_PIN T7 [get_ports [list {LED[2]}]]

set_property PACKAGE_PIN T4 [get_ports [list {LED[3]}]]

set_property PACKAGE_PIN T3 [get_ports [list {LED[4]}]]

set_property PACKAGE_PIN U2 [get_ports [list {LED[5]}]]

set_property PACKAGE_PIN U6 [get_ports [list {LED[6]}]]

set_property PACKAGE_PIN U5 [get_ports [list {LED[7]}]]

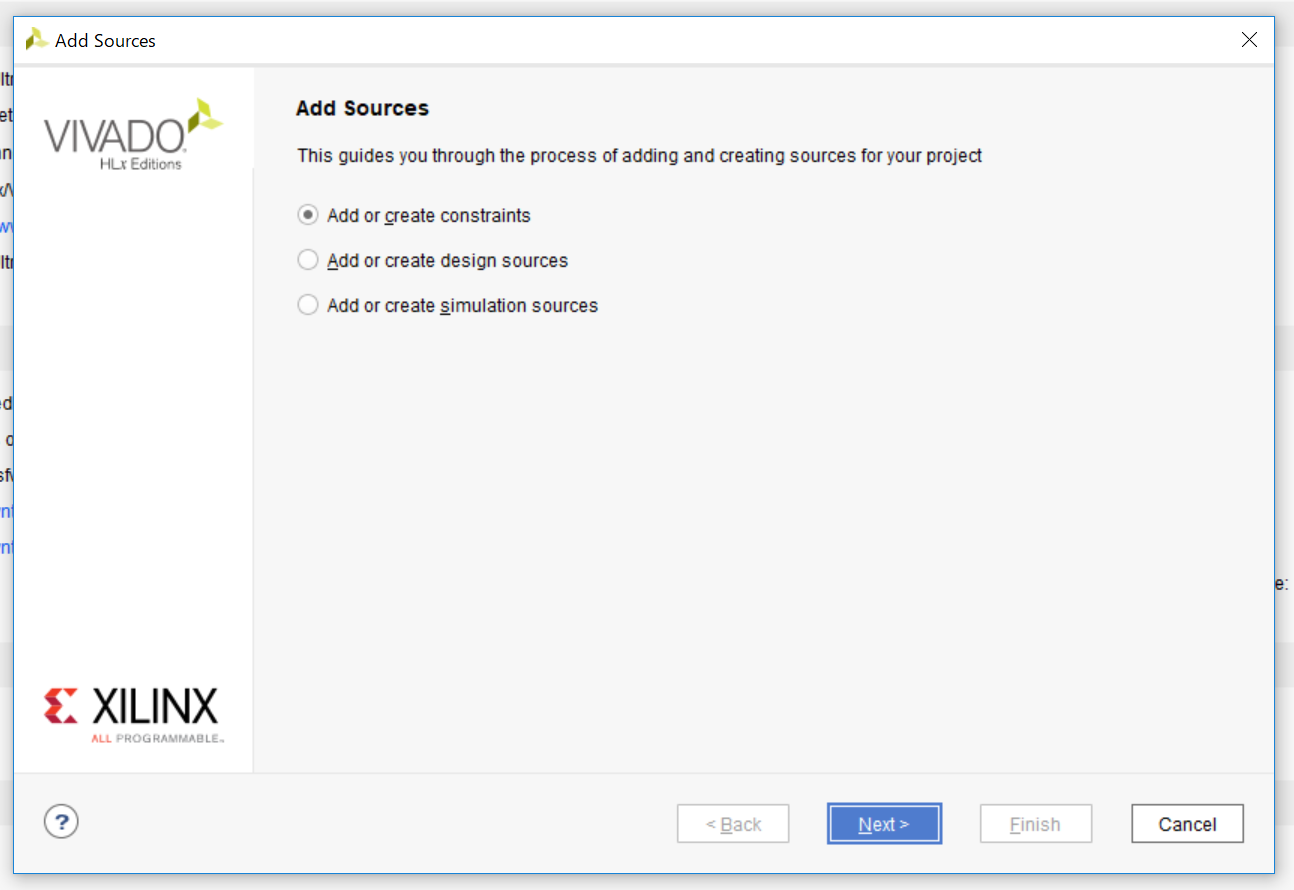

Add Sourcesをクリックして下図のメニューを表示させ、Add or create contraintsのラジオボタンを選択。

- RTLアナリシス

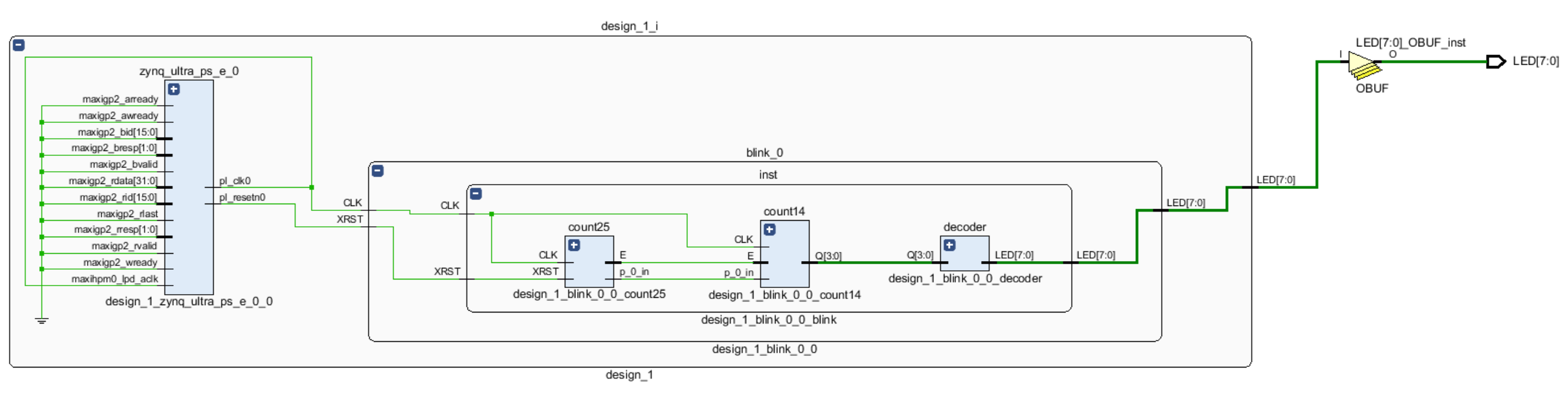

合成、配置配線をかける前に、RTLが正しく読めているかどうかを回路図的に確認します。Flow NavigatorからRTL ANALYSISを選択し、Schematicをクリック。階層化されているブロックを適宜展開し、解析を行うと以下の図のようになります。

- RTL合成

Run Synthesisをクリックし、論理合成を実施します。 - 実装

Run Implementationをクリックし、配置配線を実施します。 - ビットストリームの作成

Generate Bitstreamをクリックし、コンフィグファイルの作成を実施します。 - FPGAのコンフィギュレーション

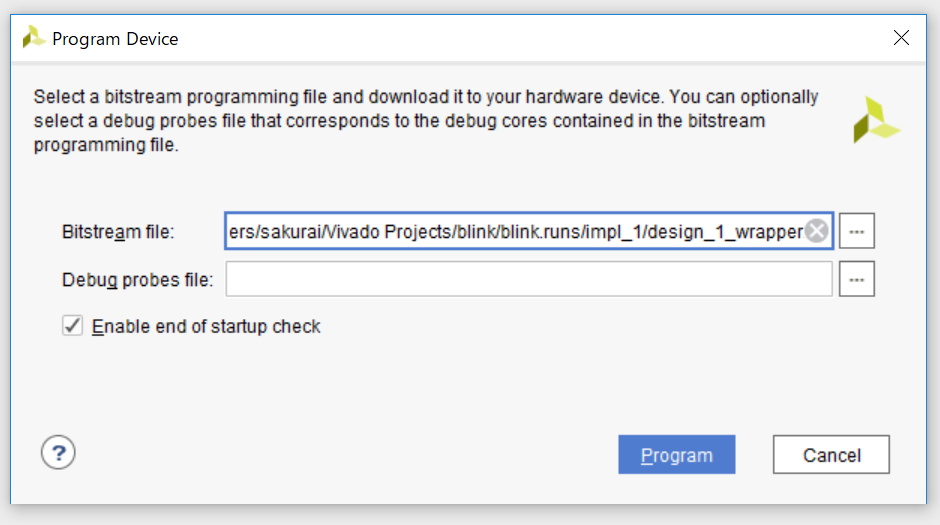

Open Targetをクリックし、Auto Connectを行います。以下の図のメニューが出てビットストリームファイルの選択となるため、そのままProgramを行います。

Leave a Comment