BluespecのFluteプロセッサ

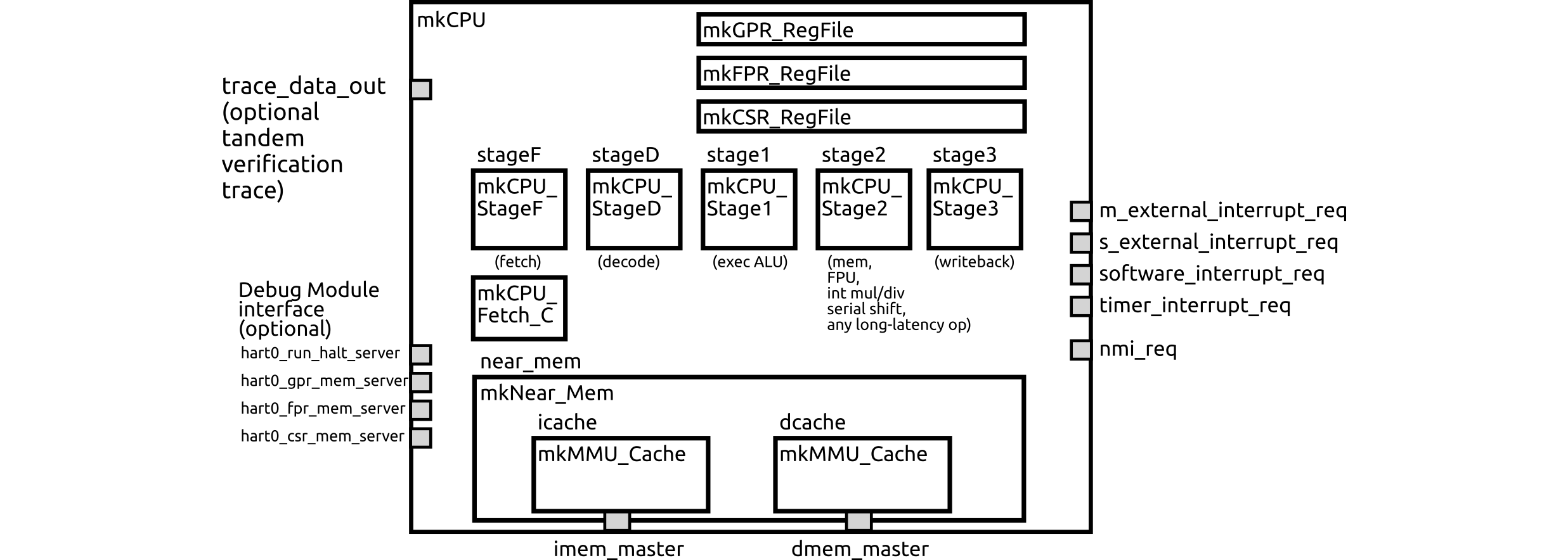

BluespecのBSVが読めるようになったところで、引き続いてFluteプロセッサの調査を行います。FluteはBluespecの開発したRISC-Vアーキテクチャの5段パイプラインRISC CPUです。それだけでなく、仮想記憶をサポートしているため、Linuxが動作します。(ページ)テーブルウォークはMMU内のハードウェアが実行します。ソースではステートベース設計のFSMで実装されていました。

Githubからダウンロード

$ git clone https://github.com/bluespec/Flute.git

としてGithubからダウンロードします。

RV32ACIMUアーキテクチャのBsimモデルの作成

アーキテクチャには各種ありますが、比較的軽いもの、例えば32bit、Floating無しのマイクロアーキテクチャを選択します。

$ cd builds/RV32ACIMU_Flute_bluesim

として、ターゲットディレクトリに移行します。

$ make all

と実行すると、

:

Simulation shared library created: exe_HW_sim.so

Simulation executable created: ./exe_HW_sim

INFO: linked bsc-compiled objects into Bluesim executable

$

このように、bsvで書かれたソースファイルがbscによりコンパイルされ、シミュレーションモデルであるexe_HW_simが生成されます。

RV32ACIMUアーキテクチャのBsimモデルの試験

$ make test

により、出来上がったシミュレーションモデルが、RISC-Vのテストスイートによりテストされます。

$ make test

make -C ../../Tests/elf_to_hex

make[1]: Entering directory '/home/sakurai/src/bsv/riscv/Flute/Tests/elf_to_hex'

make[1]: 'elf_to_hex' is up to date.

make[1]: Leaving directory '/home/sakurai/src/bsv/riscv/Flute/Tests/elf_to_hex'

../../Tests/elf_to_hex/elf_to_hex ../../Tests/isa/rv32ui-p-add Mem.hex

c_mem_load_elf: ../../Tests/isa/rv32ui-p-add is a 32-bit ELF file

Section .text.init : addr 80000000 to addr 80000604; size 0x 604 (= 1540) bytes

Section .tohost : addr 80001000 to addr 80001048; size 0x 48 (= 72) bytes

Section .riscv.attributes: Ignored

Section .symtab : Searching for addresses of '_start', 'exit' and 'tohost' symbols

Writing symbols to: symbol_table.txt

No 'exit' label found

Section .strtab : Ignored

Section .shstrtab : Ignored

Min addr: 80000000 (hex)

Max addr: 80001047 (hex)

:

================================================================

Bluespec RISC-V standalone system simulation v1.2

Copyright (c) 2017-2019 Bluespec, Inc. All Rights Reserved.

================================================================

INFO: watch_tohost = 1, tohost_addr = 0x80001000

1: top.soc_top.mem0_controller_axi4_deburster::AXI4_Deburster.rl_reset

2:top.soc_top.rl_reset_start_initial ...

3: Core.rl_cpu_hart0_reset_from_soc_start

================================================================

CPU: Bluespec RISC-V Flute v3.0 (RV32)

Copyright (c) 2016-2020 Bluespec, Inc. All Rights Reserved.

================================================================

6: D_MMU_Cache: cache size 8 KB, associativity 2, line size 32 bytes (= 8 XLEN words)

6: I_MMU_Cache: cache size 8 KB, associativity 2, line size 32 bytes (= 8 XLEN words)

512: top.soc_top.core.cpu.rl_reset_complete: restart at PC = 0x1000

514: Near_Mem_IO_AXI4.set_addr_map: addr_base 0x2000000 addr_lim 0x200c000

514: Core.rl_cpu_hart0_reset_complete

515: Mem_Controller.set_addr_map: addr_base 0x80000000 addr_lim 0x90000000

515:top.soc_top.rl_reset_complete_initial

instret:0 PC:0x1000 instr:0x297 priv:3

instret:1 PC:0x1004 instr:0x2028593 priv:3

instret:2 PC:0x1008 instr:0xf1402573 priv:3

:

instret:471 PC:0x80000044 instr:0xfc3f2023 priv:3

instret:472 PC:0x80000048 instr:0xff9ff06f priv:3

instret:473 PC:0x80000040 instr:0x1f17 priv:3

2396: Mem_Controller.rl_process_wr_req: addr 0x80001000 (<tohost>) data 0x1

PASS

2397: top:.rl_terminate: soc_top status is 0x1 (= 0d1)

Simulation speed: 2396 cycles, 60915008 nsecs = 39333 cycles/sec

テストスイートのelfを、elf_to_hexにより、asciiのメモリイメージファイルに変換しています。

これはadd命令単体のテストですが、全てのテストを行うには、以下のように実行します。

$ make isa_tests

と実行すると、

:

Worker 1: Test: rv32um-p-mul PASS [So far: total 67, executed 34, PASS 34, FAIL 0]

Worker 0 executed 33 tests, of which 33 passed

Worker 1 executed 34 tests, of which 34 passed

Total tests: 67 tests

Executed: 67 tests

PASS: 67 tests

FAIL: 0 tests

Finished running regressions; saved logs in Logs/

のように出力され、67個全てのテストが実行され、全てパスしたことが表示されます。

前のブログ

次のブログ

前のブログ

次のブログ