2段FIFOの検討(4)

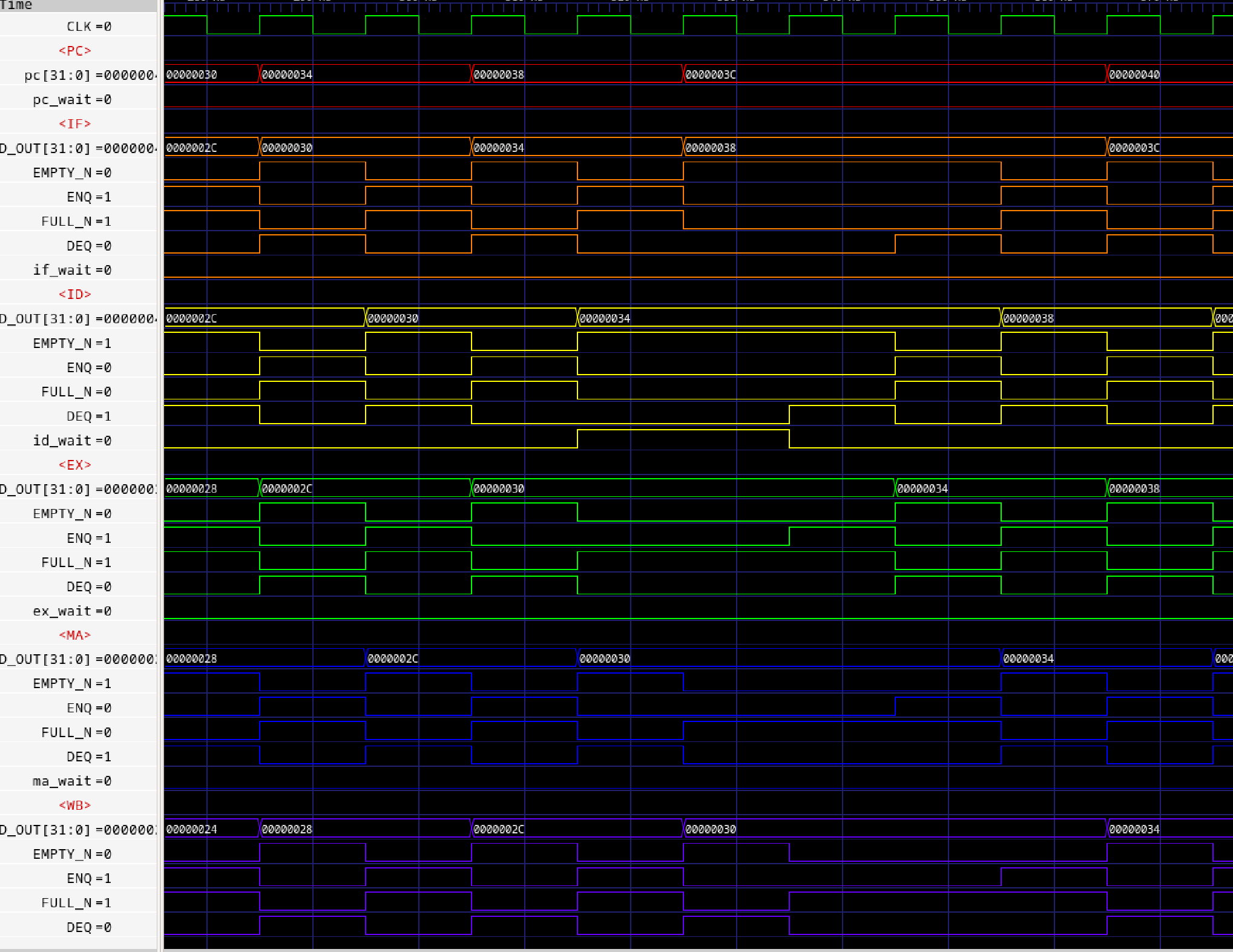

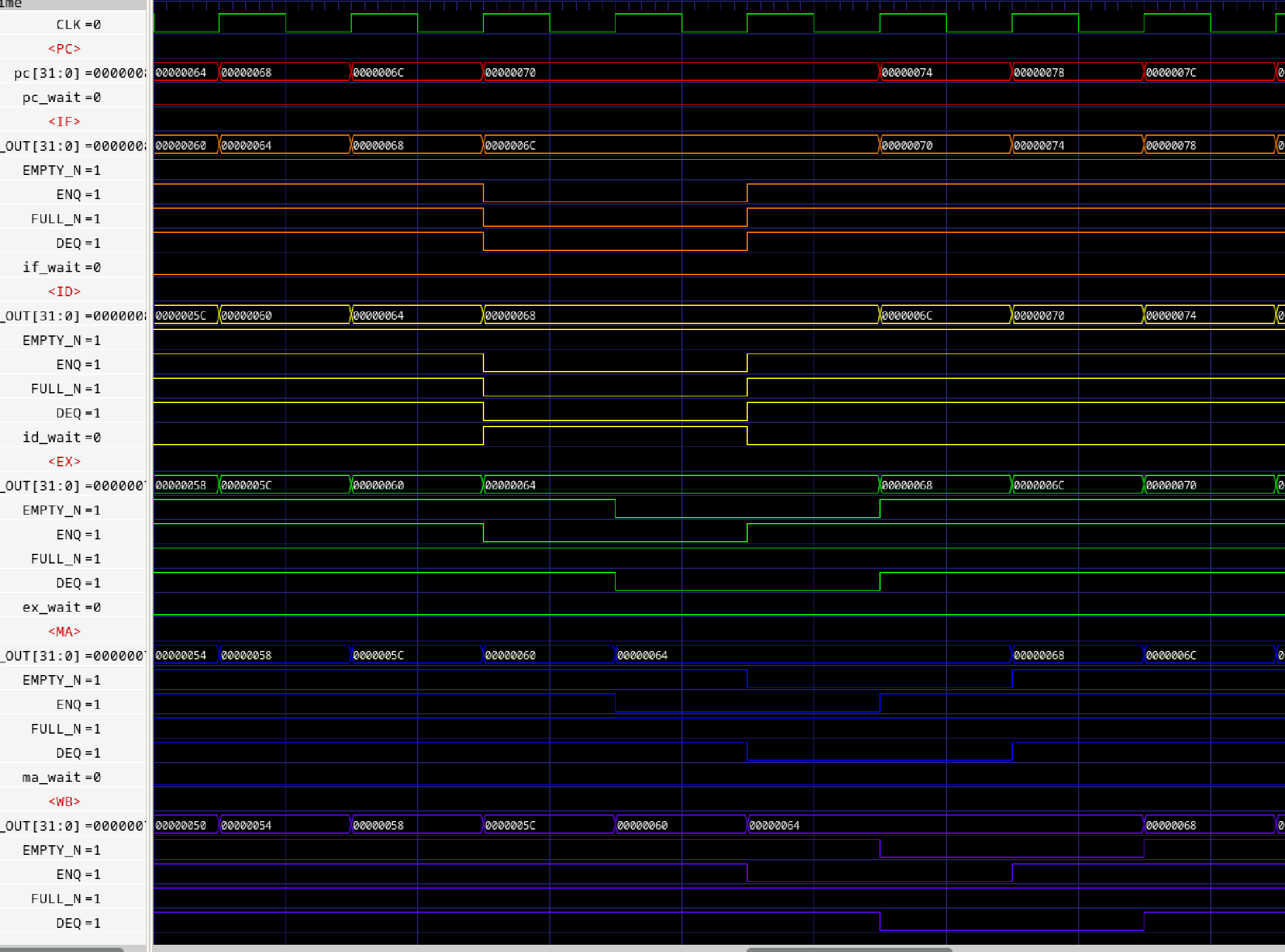

ここまでで自作FIFO2.vの論理が確定しました。そこでBluespec作成のライブラリであるverilogの論理FIFO2.vと一致するかを確認します。

d0diの論理の手圧縮の結果はd0di = (ENQ && empty == 1) || (DEQ && full == 0)です。一方、Bluespec製verilogソースは、

$BLUESPECDIR/Verilog/FIFO2.v

wire d0di = (ENQ && ! empty_reg ) || ( ENQ && DEQ && full_reg ) ;

です。empty_regは不論理のemptyなのでBluespecと1項目は一致しています。

一方2項目目は不一致です。Bluespecには若干無駄があるようです。これをケース分解すれば、2項目は4, 8ですがさらにD.C.である3と7を加えることができます。ちなみにBluespecではempty_reg及びfull_regはなぜか負論理なので、!empty_regはemptyを、full_regは!fullを意味します。

次にd0d1の論理は、d0d1 = DEQ && full == 1ですがBluespec製verilogソースは、

wire d0d1 = DEQ && ! full_reg ;

であり、完全一致しました。

次に、d0hの論理は、d0h = !DEQ && empty == 0ですがBluespec製verilogソースは、

wire d0h = ((! DEQ) && (! ENQ )) || (!DEQ && empty_reg ) || ( ! ENQ &&full_reg) ;

であり、かなり無駄があるようです。

Bluespec製verilogソースをケース分解すれば、1項目は1,5,9、2項目は5,6,9,10、3項目は1,3,5,7です。必要なのは5,6,9だけなので2項目のみで全てを満たしているのですが、BluespecはState0でもホールドするとして1項目を加えたようです。State0ではデータは無効なのでホールドの必要はありませんがState0で何も起きない場合のホールドである1と、State1からDEQされた場合の7が追加されています。

3項目はState0, 1でENQとならない場合という意味ですが、そもそもState0では無効データのためホールドの必要は無いし、State1でもDEQの場合(7)はホールド不要です。

【追記】無効データではあるものの、DEQされた場合やENQもDEQも無い場合は、前の値を保持するというのがBluespecの仕様のようです。

最後にd1diの論理は、d1di = ENQ && empty == 0ですがBluespec製verilogソースは、

wire d1di = ENQ & empty_reg ;

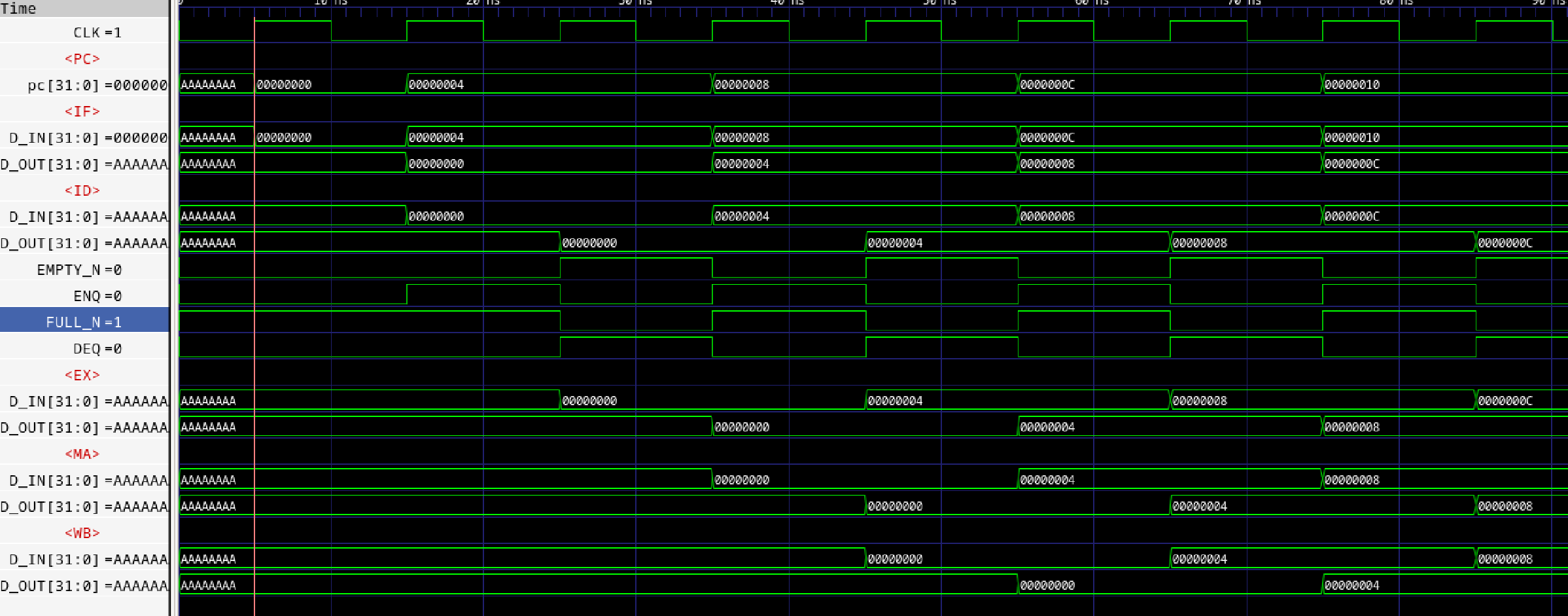

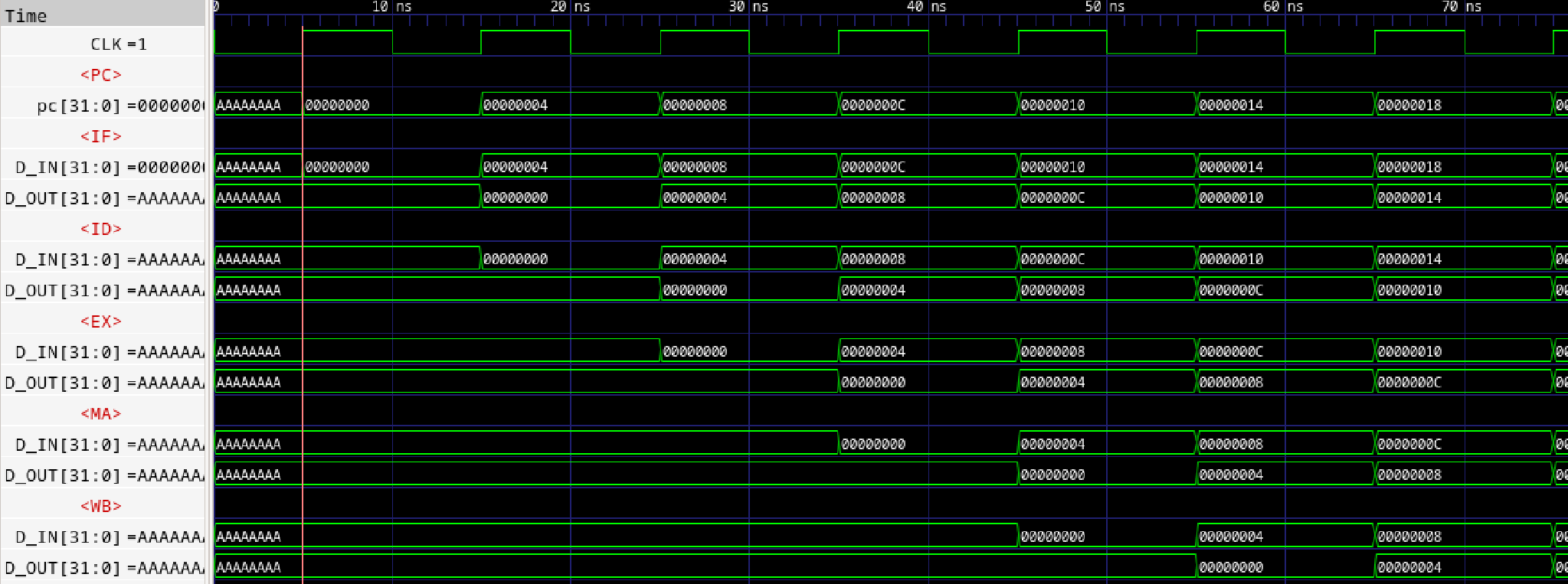

であり、完全一致しました。弊社の論理に変更したFIFOライブラリを用いてシミュレーションを実行しましたが、正常に動作しました。

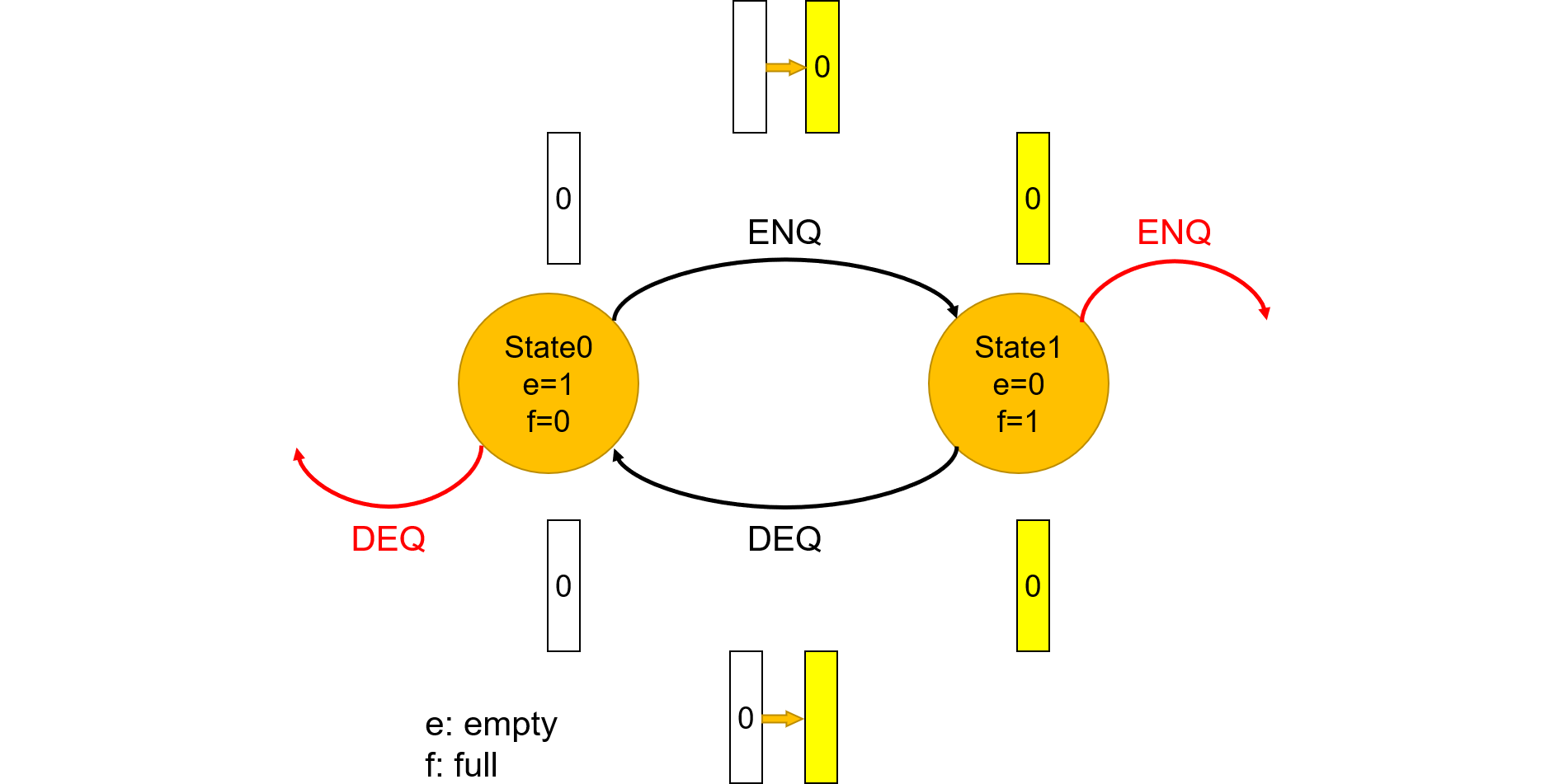

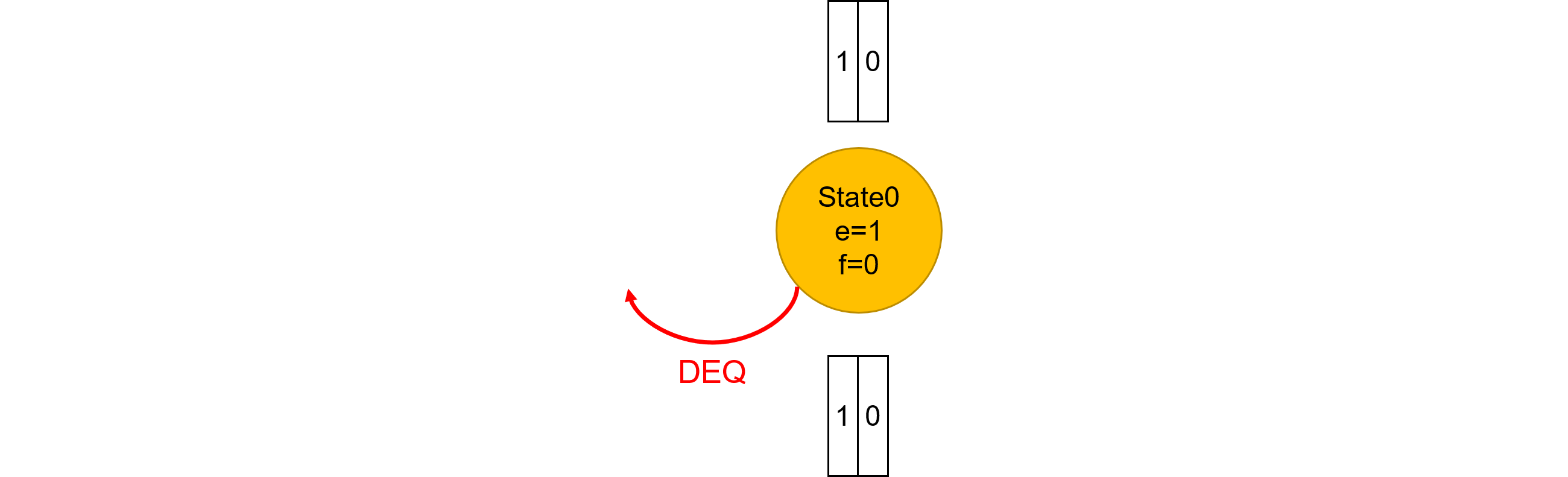

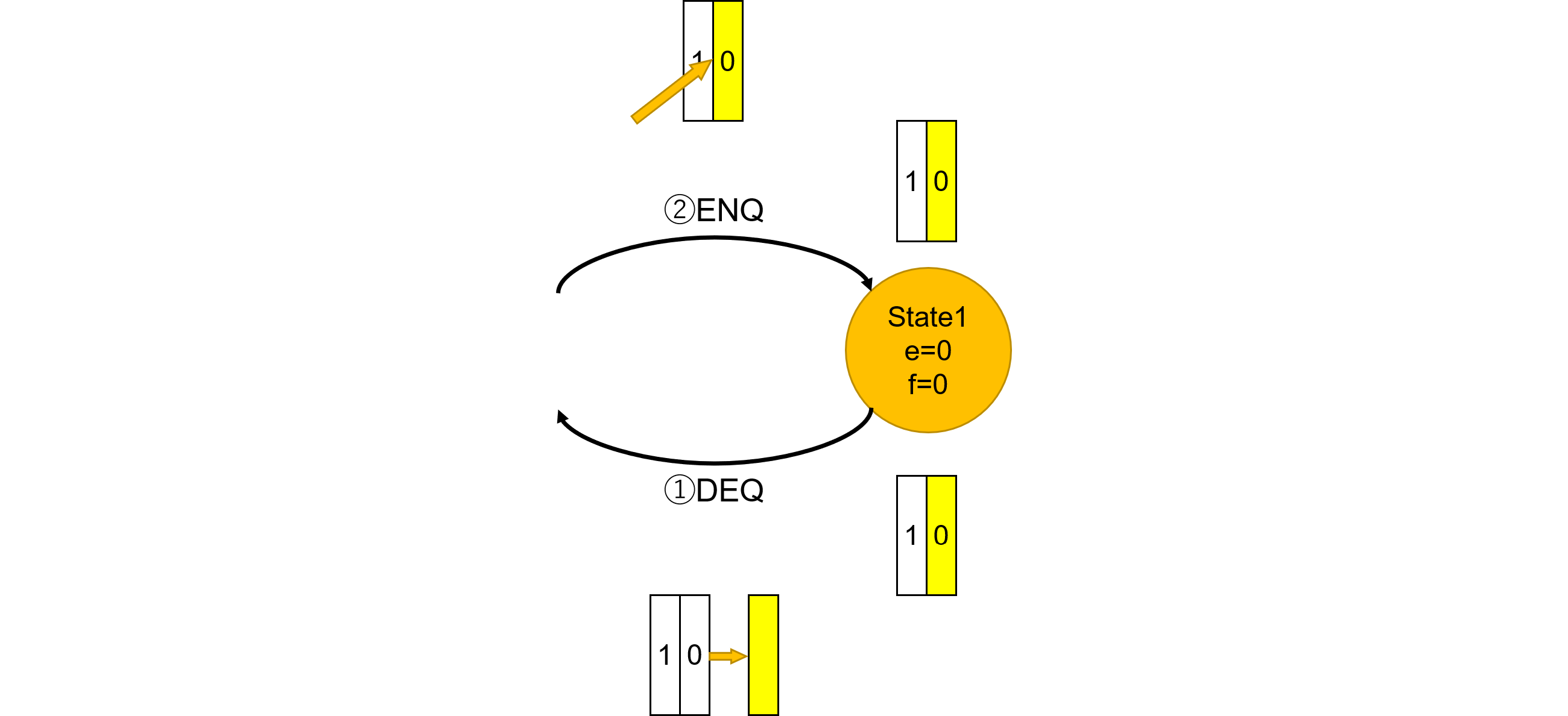

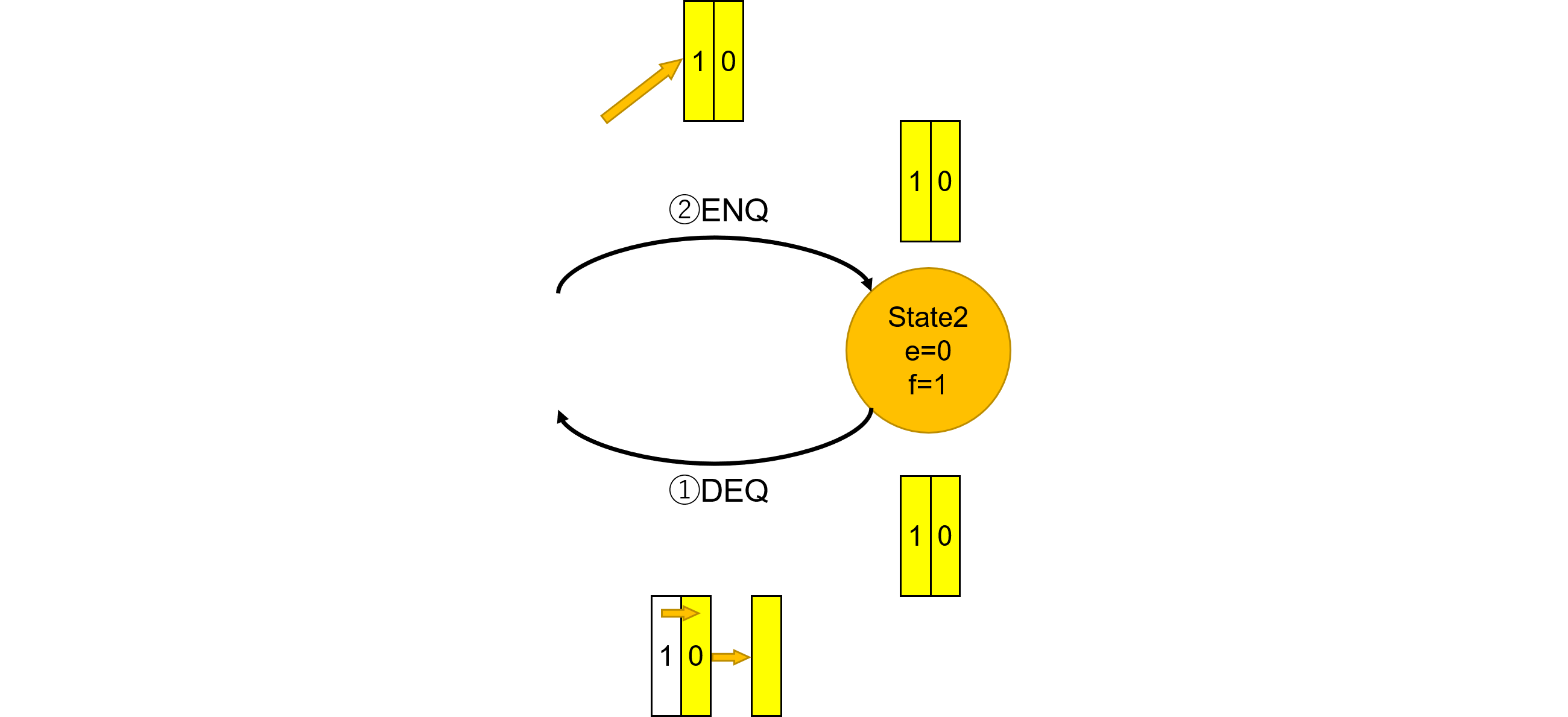

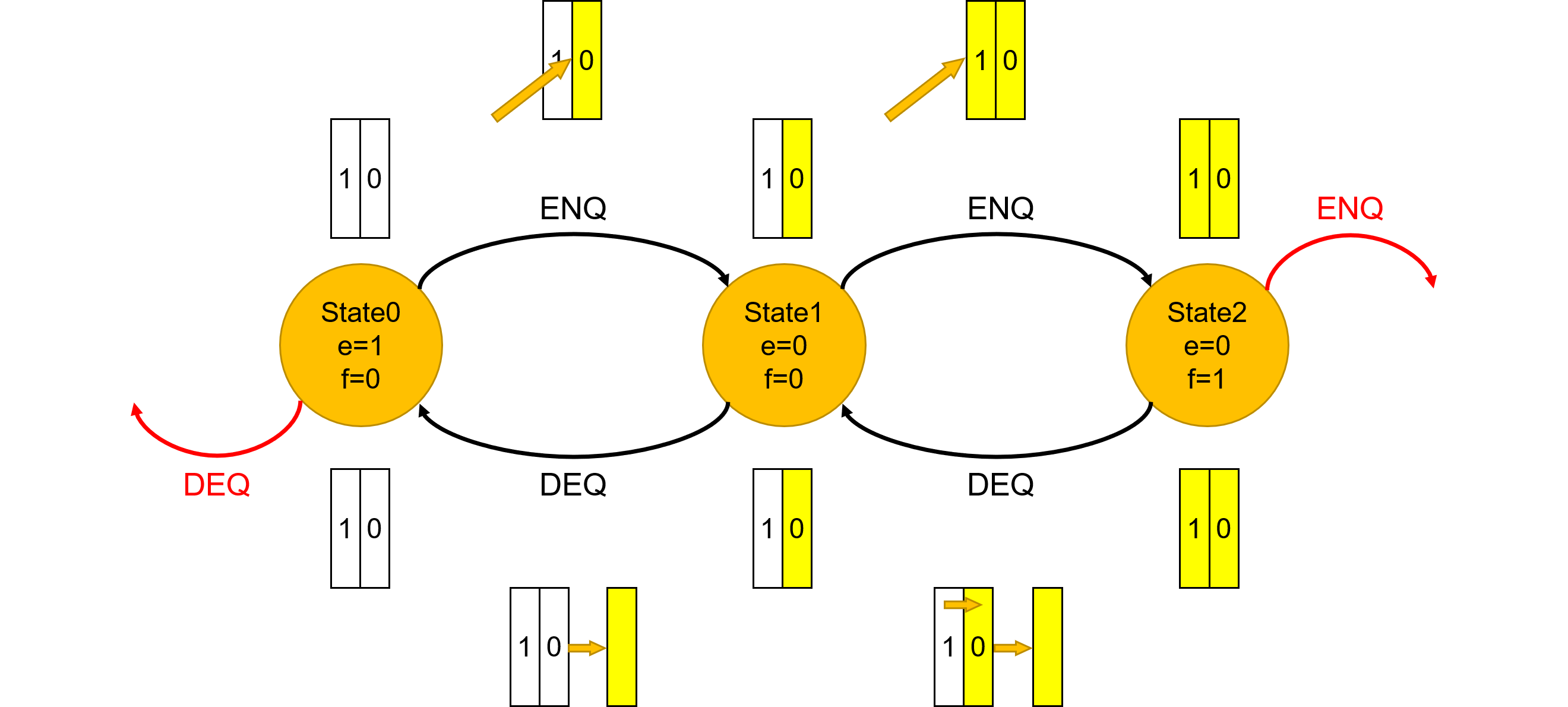

さらに、ステート遷移は、手圧縮では、

CLRのとき、empty = 1, full = 0!DEQ && ENQのとき、empty = 0, full = !emtpyDEQ && !ENQのとき、empty = !full, full = 0- 上記以外のときはホールド。emtpy, full共変化無し。

となりましたが、Bluespec製verilogソースでは、

begin

if (CLR)

begin

empty_reg <= `BSV_ASSIGNMENT_DELAY 1'b0;

full_reg <= `BSV_ASSIGNMENT_DELAY 1'b1;

end // if (CLR)

else if ( ENQ && ! DEQ ) // just enq

begin

empty_reg <= `BSV_ASSIGNMENT_DELAY 1'b1;

full_reg <= `BSV_ASSIGNMENT_DELAY ! empty_reg ;

end

else if ( DEQ && ! ENQ )

begin

full_reg <= `BSV_ASSIGNMENT_DELAY 1'b1;

empty_reg <= `BSV_ASSIGNMENT_DELAY ! full_reg;

end // if ( DEQ && ! ENQ )

end // else: !if(RST == `BSV_RESET_VALUE)

となっており、完全一致しました。

前のブログ

前のブログ

次のブログ