|

6 |

RISC-Vプロセッサの設計 (11) |

verilogシミュレーション

ついでにverilogでもシミュレーションしてみます。

$ bsc -verilog Tb.bsv

Verilog file created: mkTb.v

$ iverilog top.v mkTb.v -y /usr/local/lib/Bluespec/Verilog/ -o mkTb.exev

$ ./mkTb.exev

VCD info: dumpfile verilog.vcd opened for output.

------

------

pc_if = 00000000

------

pc_if = 00000004

pc_id = 00000000

------

pc_if = 00000008

pc_id = 00000004

pc_ex = 00000000

------

pc_if = 0000000c

pc_id = 00000008

pc_ex = 00000004

pc_ma = 00000000

------

pc_if = 00000010

pc_id = 0000000c

pc_ex = 00000008

pc_ma = 00000004

pc_wb = 00000000

------

pc_if = 00000014

pc_id = 00000010

pc_ex = 0000000c

pc_ma = 00000008

pc_wb = 00000004

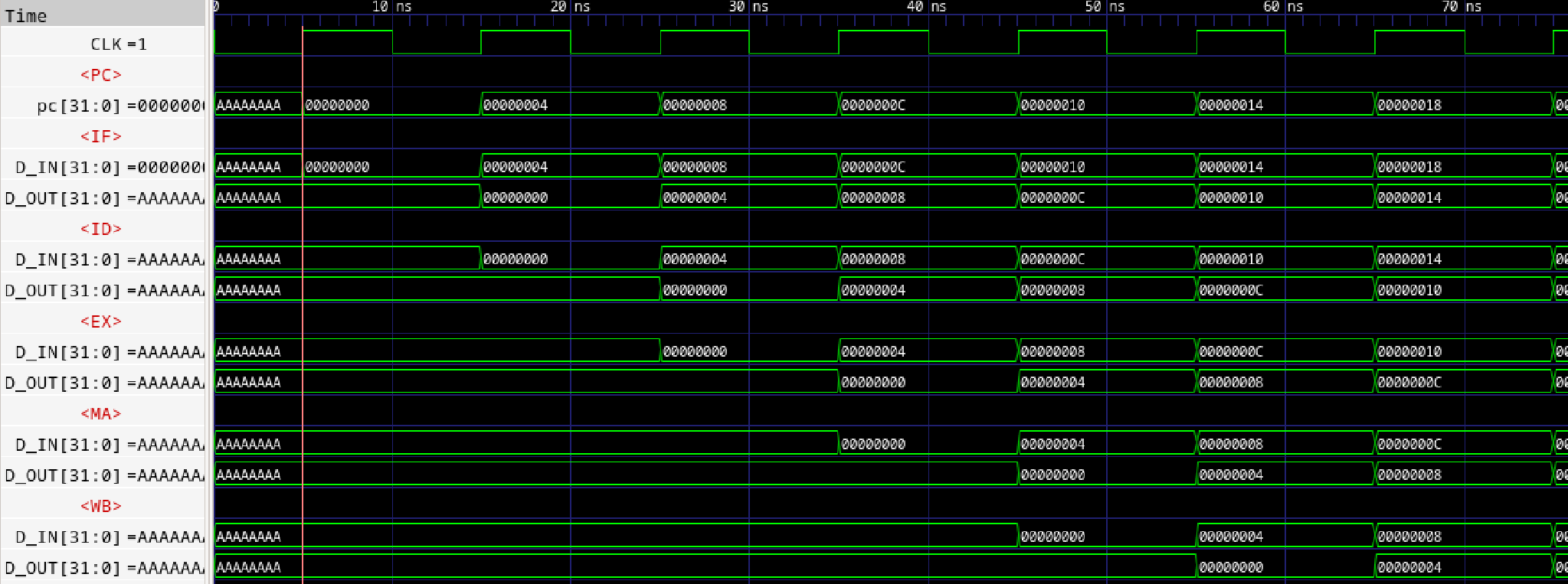

のように正しくパイプラインが動作しました。また、gtkwaveで取得したタイムチャートを図564.1に示します。

gtkwファイルはここ。

Leave a Comment