|

9 |

RISC-Vプロセッサの設計 (14) |

|

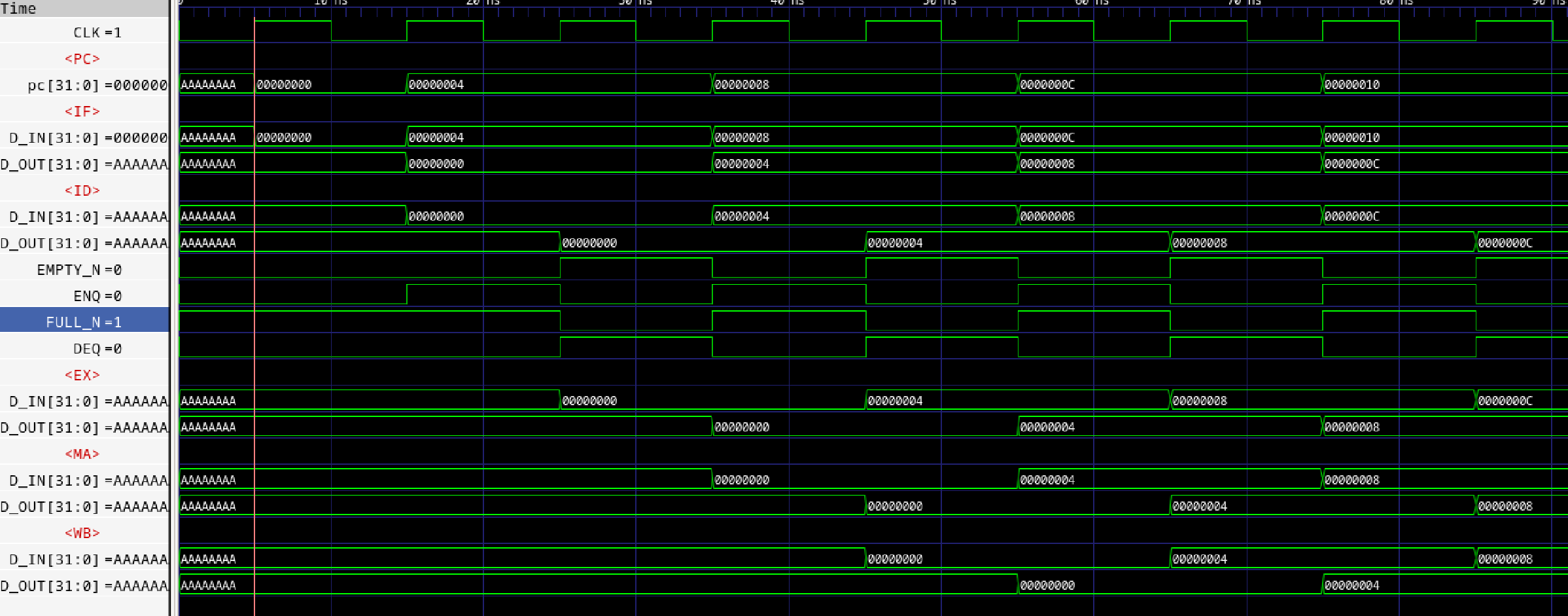

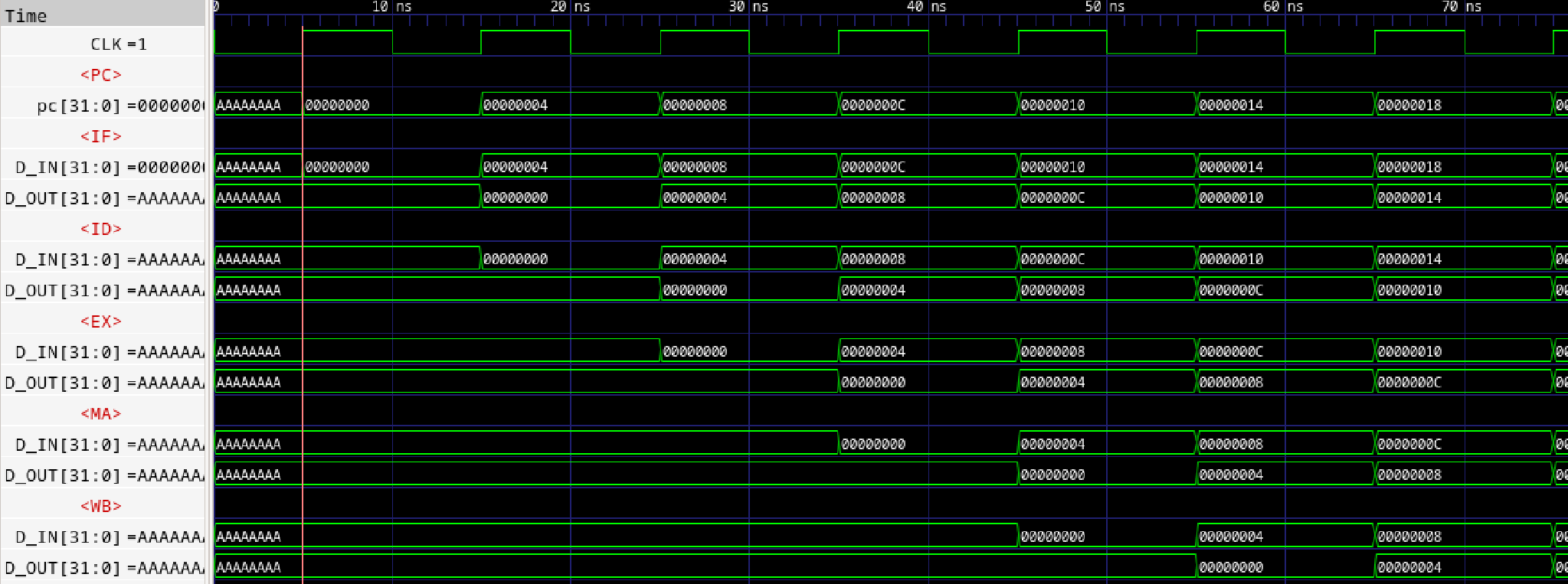

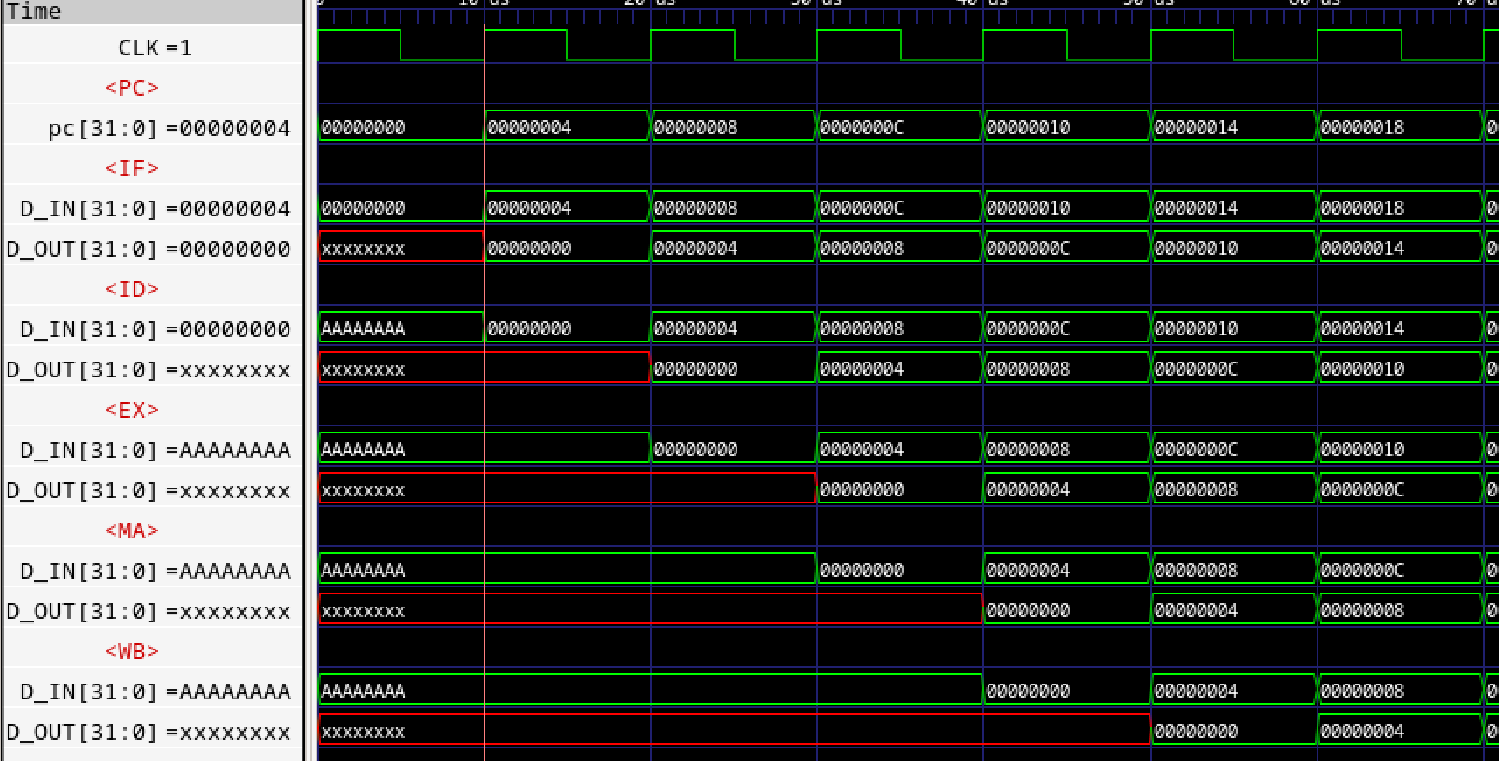

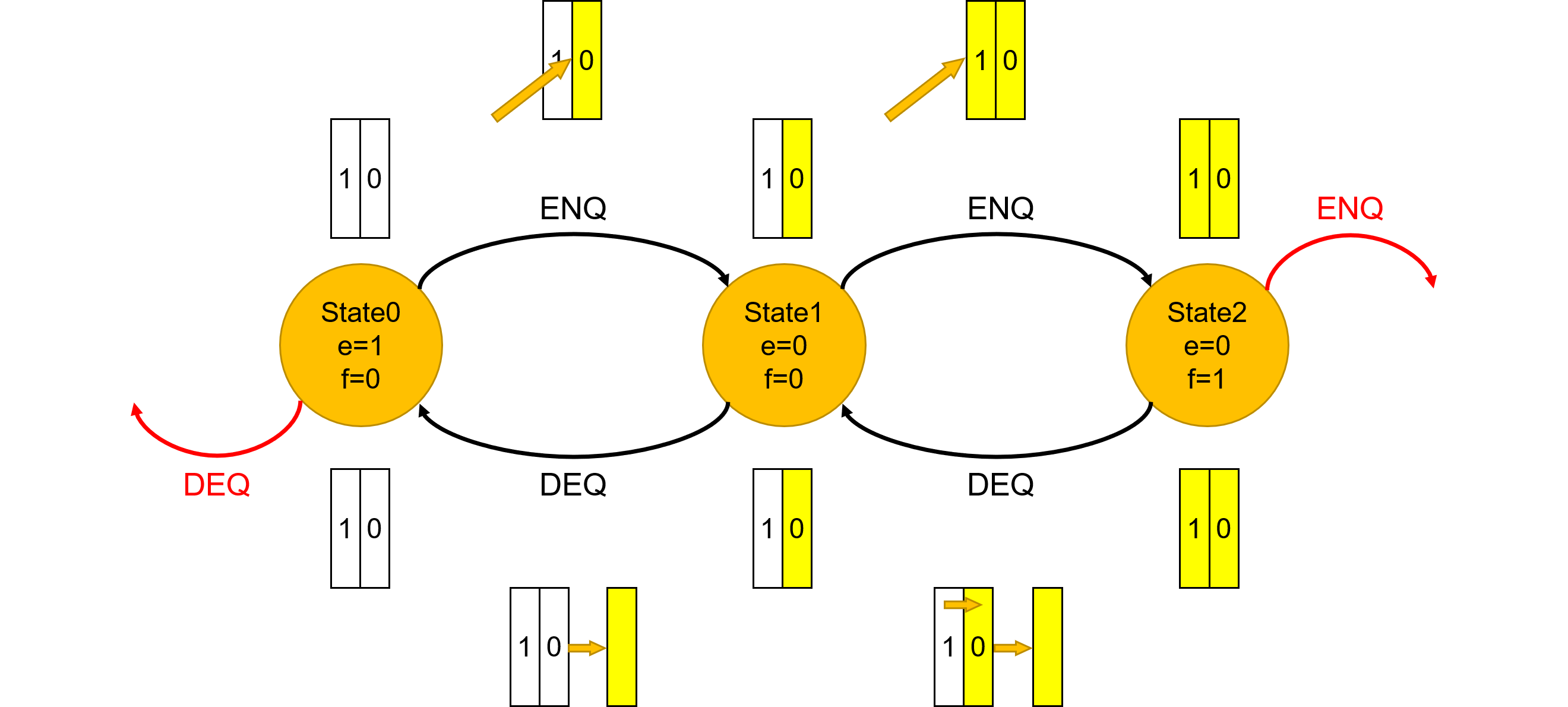

2段FIFOの検討

BSVのデフォルトである2段FIFOの動作を、新規設計するつもりで一から検討します。

2段FIFOなのでレジスタを2段持ち、それぞれd0とd1と名前を付けます。ライブラリと同様にd0からFIFO出力を固定的に出力するものとします。

- 2段FIFOのFIFOの有効段の数は0個、1個、2個なので、その数をステートと扱えば、サブシステムのステートにはState0~State2の3種類があることになります。

- 一度に2個をキューに入れることはできないので、エンキュー(以下ENQ)の場合は、State0⇒State1⇒State2のように遷移します。

- 逆にデキュー(以下DEQ)の場合はState2⇒State1⇒State0のように遷移します。

- State0のときにDEQ、State2のときにENQが起きるとエラーとなります(赤色で表現)。

- DEQの場合に後段へデータを出力しますが、必ずd0から出力するように制御します。そのため、ENQの際にはステートにより格納する段が変わります。

- 具体的にはState0のときにENQであればd0に格納

- State1のときにENQであればd1に格納

- State2のときにENQであればエラー(前述)、DEQであればd0を外に移してd1をd0に移し、d1を無効化

- State1のときにDEQであればd0を外に移してd0を無効化

- 上記無効化のフラグビットは不要です。ステート遷移先はステートと遷移条件で決まり、ステートにより有効段はあらかじめ確定しているためです。具体的にはState0は有効段無し、State1は有効段はd0のみ、State2は有効段はd0とd1と定まっています。