|

26 |

BSVによるメモリダンプモジュールの設計 (9) |

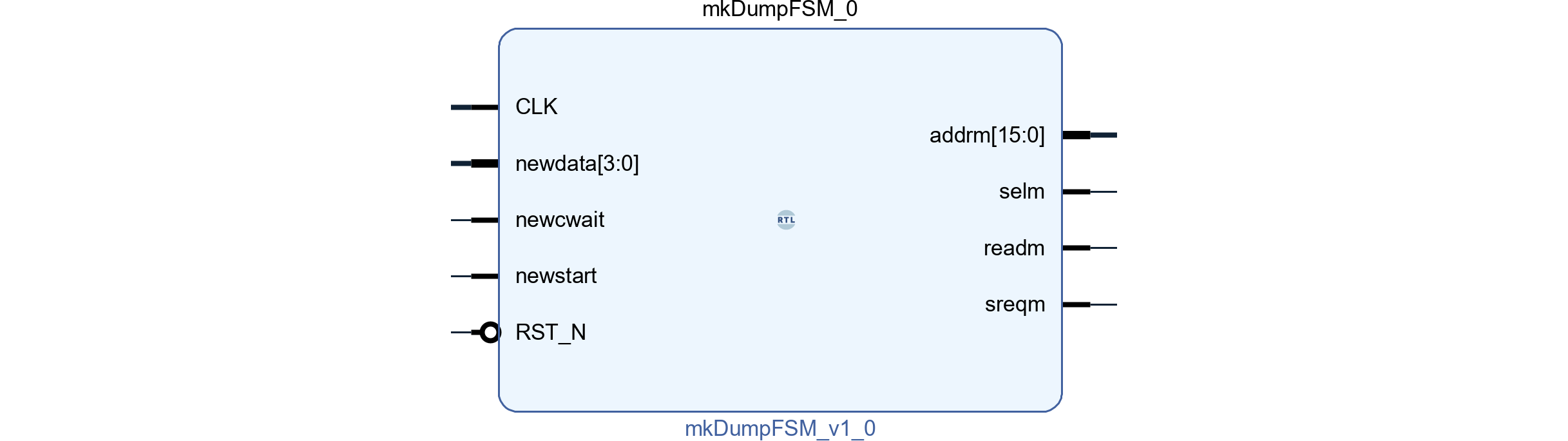

出来上がったモジュールの図を図406.1に示します。

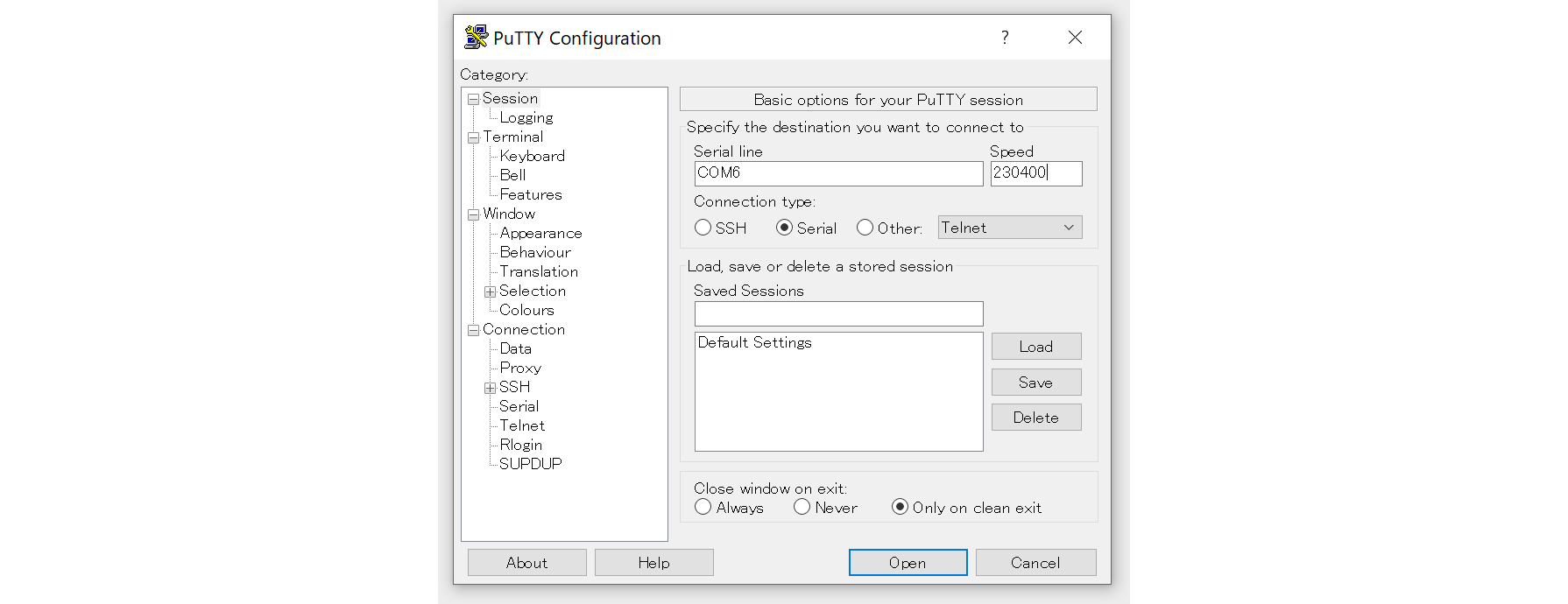

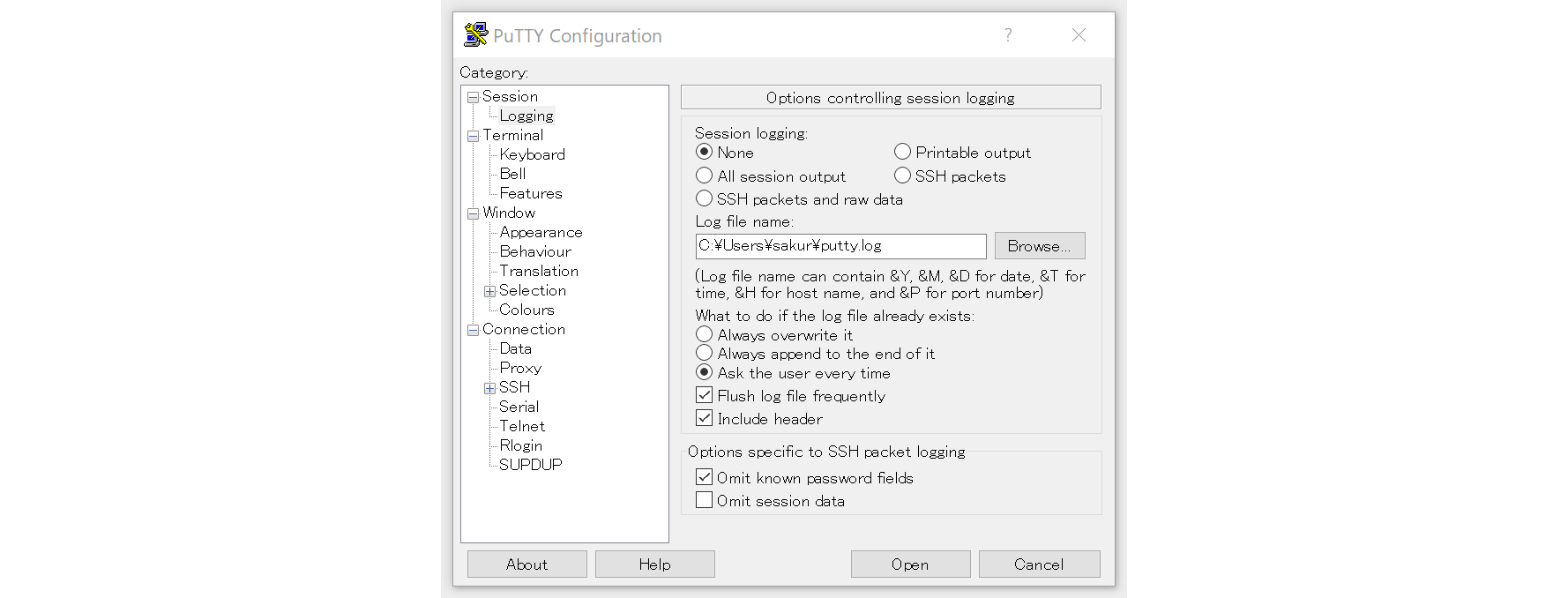

シリアルデータ出力はUART_TXに接続します。これによりFPGAボード(正確にはアダプタボードであるAES-ACC-U96-JTAGボード)上でUSBに変換され、ケーブルを経由してPCのPuttyで受信します。今回は230,400 bps、COMは6番だったので、以下のようにPuttyの受信パラメータ及びログの場所を設定します。

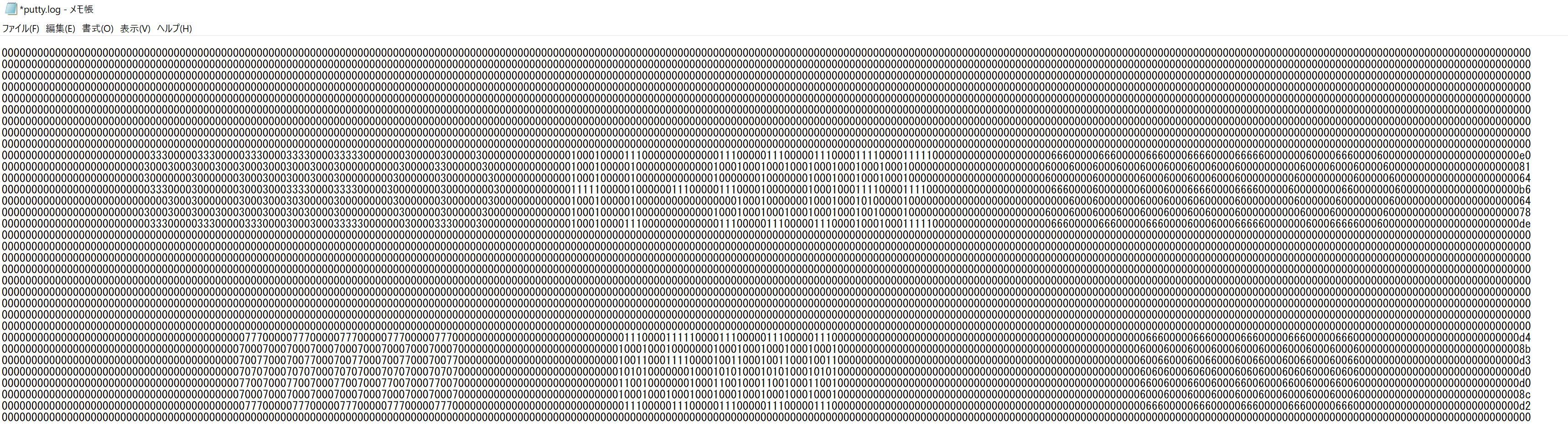

ゲームをスタートさせて、FPGAボード上のダンプスイッチを押すと、ゲームが一時停止し、FPGAボードからはPuttyに対して以下のようなデータを送信して来ます。右端はチェックサムですが、この程度の通信速度ではデータ化けはしていないようです。

Leave a Comment