|

23 |

BSVの設計トライアル (13) |

コンパイルと実行

ソースプログラムをコンパイルします。

$ bsc -u -sim TestFSM.bsv

checking package dependencies

compiling TestFSM.bsv

code generation for mkTestFSM starts

Elaborated module file created: mkTestFSM.ba

All packages are up to date.

次にリンクします。

$ bsc -sim -e mkTestFSM -o mkTestFSM

Bluesim object created: mkTestFSM.{h,o}

Bluesim object created: model_mkTestFSM.{h,o}

Simulation shared library created: mkTestFSM.so

Simulation executable created: mkTestFSM

15サイクル実行します。

$ ./mkTestFSM -V dump.vcd -m 15 | tee result

L1 S0

L1 S1

L2 S0

L2 S1

L2 S2

L3 S0

L3 S1

L4 S0

L4 S1

L3 S2

L2 S3

L2 S4

L1 S2

L1 S2

検証結果

結果を比較することにより検証します。

$ diff -c result expected

出力結果がサイクルベースで一致したことにより、正しく動作していることが検証されました。実は階層が4レベルあってもL1では戻り先が無いのでスタックを使いませんし、L4もリーフなのでスタックを使いません。従ってL2とL3だけでpush/popするため、スタックは2段(retを含めて3段)となり、spは1bitで良いことになります。これはたまたま前稿と同じ設計です。

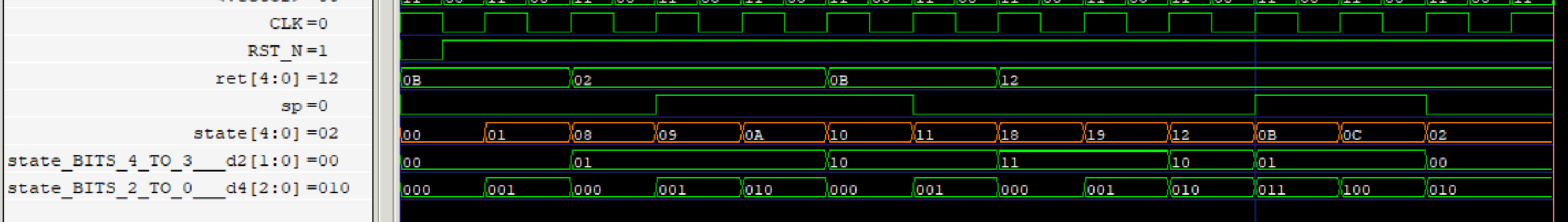

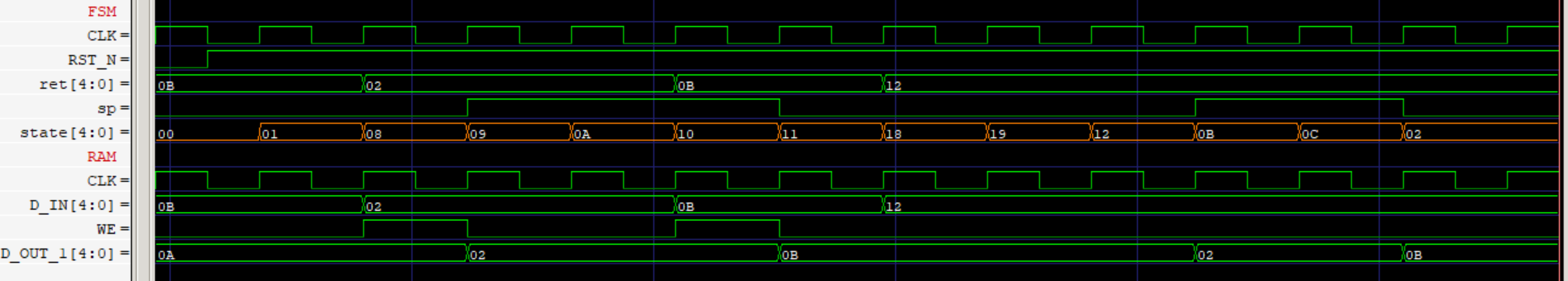

このように変更し、上記のコンパイル、実行、一致検証まで実施したところ、期待した動作をすることが確認されました。rsが2段の場合のBsimの波形を図246.2に示します。spは1bitしかないので、sp==2の際にsp==0という不正な値となっていますが、sp==2の場合のspは使用しないため、問題ありません。

Leave a Comment