|

8 |

BSVにおけるコマンドバッファ制御 (15) |

Verilogシミュレーション

次にverilogシミュレーションを実行します。

$ make vsim

bsc -verilog -bdir vobj -g mkConsumer4 -vdir rtl Consumer4.bsv

Warning: "Consumer4.bsv", line 7, column 8: (G0020)

System functions (e.g., $display) called by interface methods execute in an

unpredictable order during Verilog simulations.

Top-level interface method `consume' calls a system function (e.g.,

$display) at "Consumer4.bsv", line 34, column 7

Warning: "Consumer4.bsv", line 7, column 8: (G0117)

Rule `consume' shadows the effects of `timer' when they execute in the same

clock cycle. Affected method calls:

cnt.write, play.write

To silence this warning, use the `-no-warn-action-shadowing' flag.

Verilog file created: rtl/mkConsumer4.v

bsc -verilog -bdir vobj -u -g mkTopDirect -vdir rtl TopDirect.bsv

checking package dependencies

compiling TopDirect.bsv

code generation for mkTopDirect starts

Verilog file created: rtl/mkTopDirect.v

All packages are up to date.

bsc -verilog -bdir vobj -vsearch rtl -e mkTopDirect -o mkTopDirect.vexe

Verilog binary file created: mkTopDirect.vexe

./mkTopDirect.vexe +bscvcd=vsim.vcd +bscdumpvars

VCD info: dumpfile vsim.vcd opened for output.

5: produce = 1

5: consume = 1

105: produce = 9

105: consume = 9

205: produce = d

205: consume = d

305: produce = f

305: consume = f

405: produce = e

405: consume = e

505: produce = 7

505: consume = 7

605: produce = a

605: consume = a

705: produce = 5

705: consume = 5

805: produce = b

805: consume = b

905: produce = c

905: consume = c

=== simulation finished ===

rtl/mkTopDirect.v:115: $finish(1) called at 915 (1s)

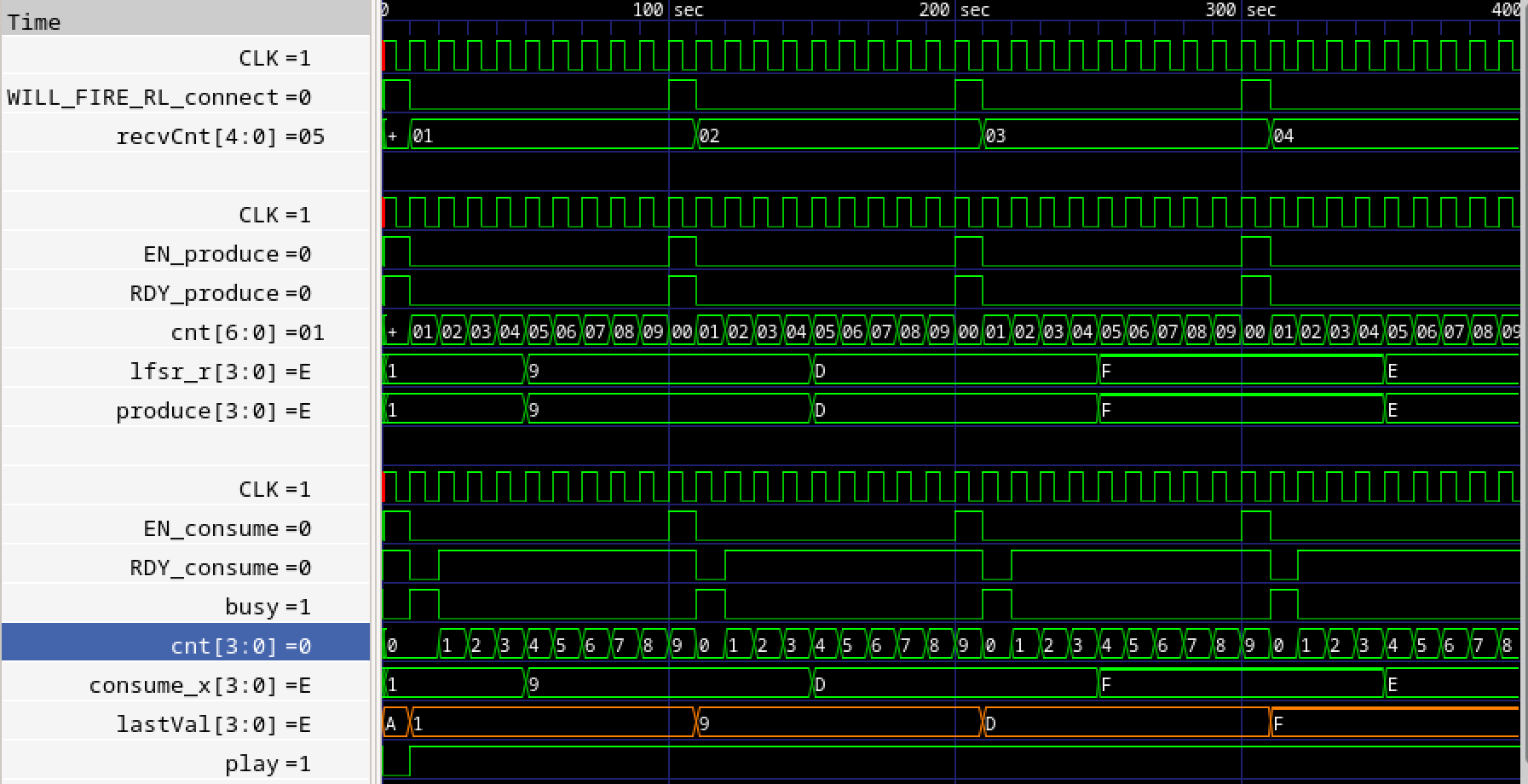

シミュレーション波形を確認します。

$ gtkwave -A vsim.vcd

本来15サイクルかかるConsumeの動作が強制的に10サイクルでリセットされるのが確認できます。

Leave a Comment