|

28 |

Ultra96とPMODインタフェース (2) |

|

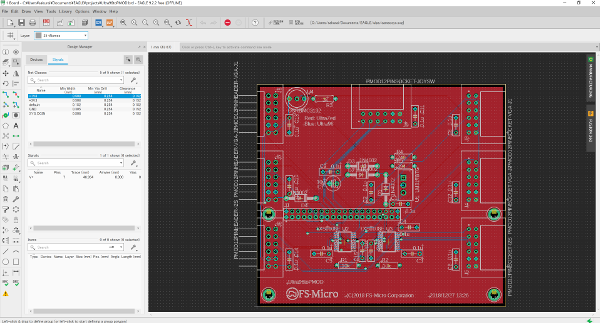

3D化による検討

基板と部品の配置を行うために3D化をします。これにより部品どうしの干渉などが発見できます。そのためには3D CADと3D部品が必要ですが、ここでは無償で使用可能なSketch Upを使用してみました。さらにEAGLEからSketch UPへのプラグインが必要となります。

そのプラグインの場所はここです。 https://eagleup.wordpress.com/

ImageMagickを入手してパスを記録しておいてください。ImageMagickのインストール時には、レガシーツール(convert.exe等)もインストールするように、チェックしておいてください。

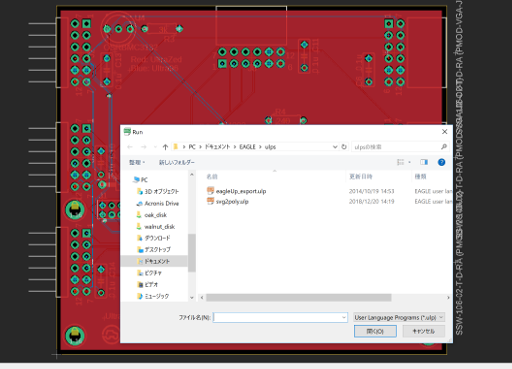

EAGLEのULP->Browseをクリックし、EagleUpを実行します。最初の一度だけパスを表示する画面が出るので、必要な情報を入力します。

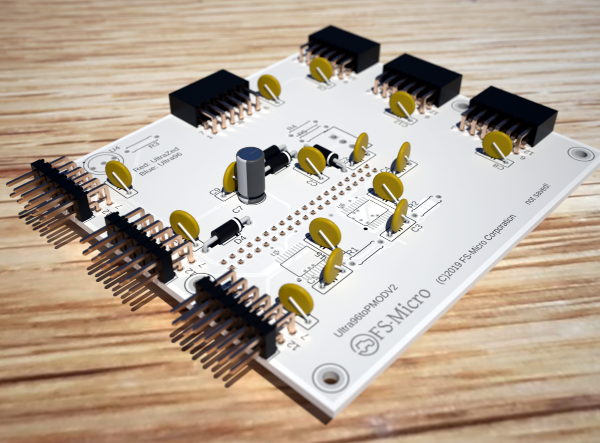

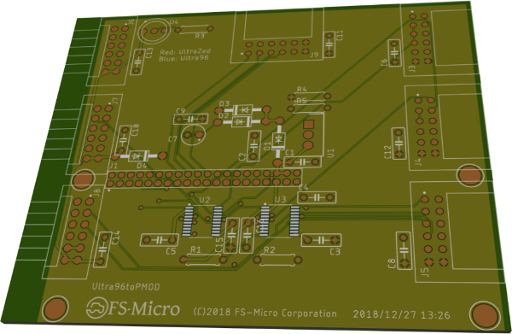

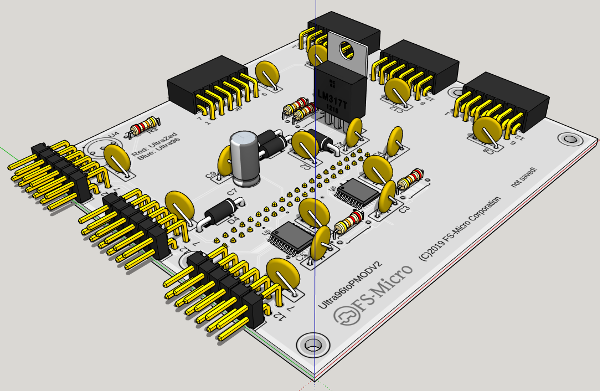

EAGLEからULPを開き、EagleUPを実行すると、SketchUpのプラグインで読み込む情報(.eupファイル)が生成されます。SketchUpを立ち上げ、プラグインを実行し、今作成された.eupファイルをロードしたものが図82.2です。ただし部品が一部未搭載です。

レンダリングしたものを図82.3に示します。ただし部品が一部未搭載です。