|

20 |

BSVによるUARTの再設計 (2) |

テストベンチ

テストベンチは変わりません。

Tb.bsv

import StmtFSM::*;

import Uart::*;

(* synthesize *)

module mkTb();

Uart_ifc uart <- mkUart();

Stmt s = seq

delay(8);

uart.load(8'h55);

uart.load(8'haa);

uart.load(8'hc3);

uart.load(8'h3c);

await(uart.done());

$finish;

endseq;

mkAutoFSM(s);

endmodule

Bsimシミュレーション

Bsimシミュレーションのコマンドは次のとおりです。

$ bsc -u -sim Tb.bsv; bsc -sim -e mkTb -o Tb.exec; ./Tb.exec -V bsim.vcd; gtkwave -A bsim.vcd

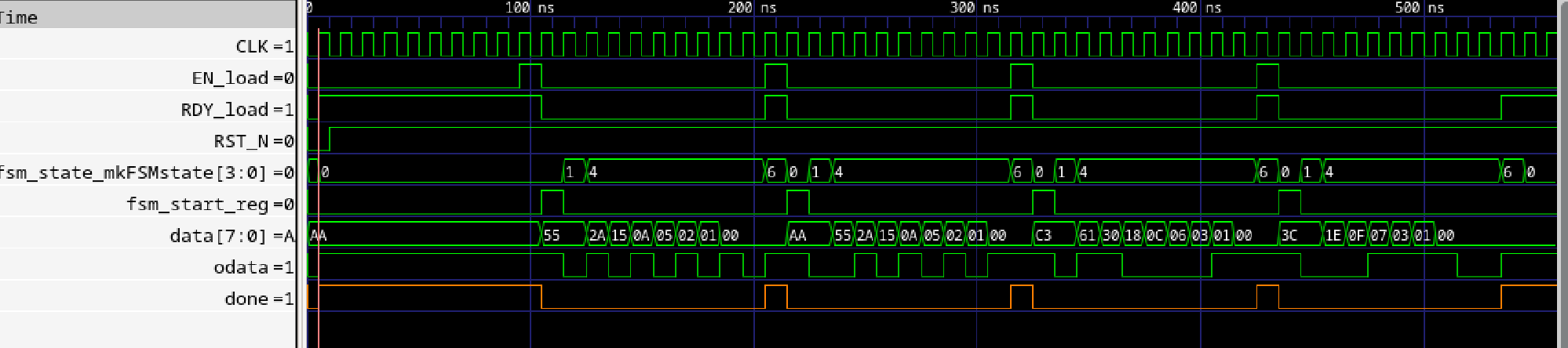

以下にBsimシミュレーション結果を示します。意外なことに明示的にdone信号を書いたにも関わらず、シミュレーションのダンプの中にdone信号がありませんでした。

テストベンチ内でレジスタにuart.doneを格納するようにしたら、インタフェースにuart.doneが現れました。awaitで使用するくらいでは削除され、レジスタに取って初めて残すようです。

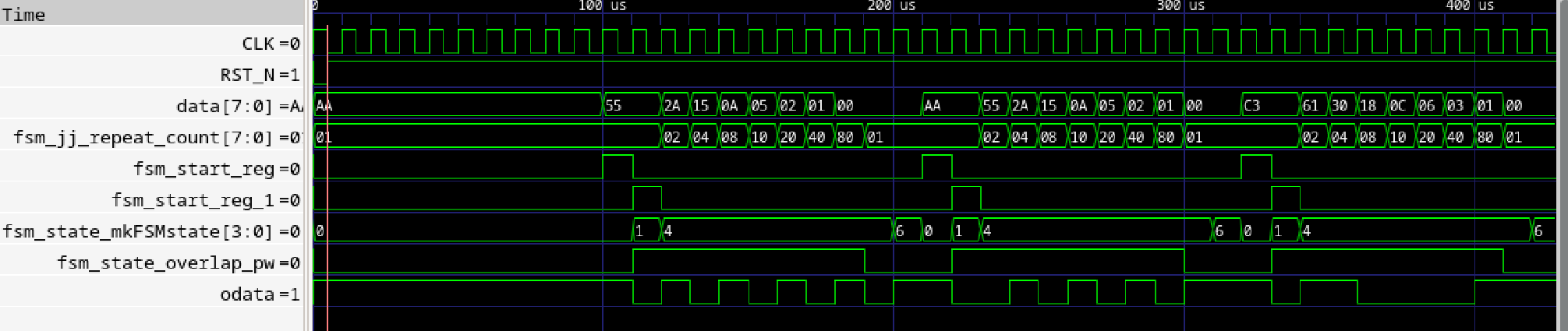

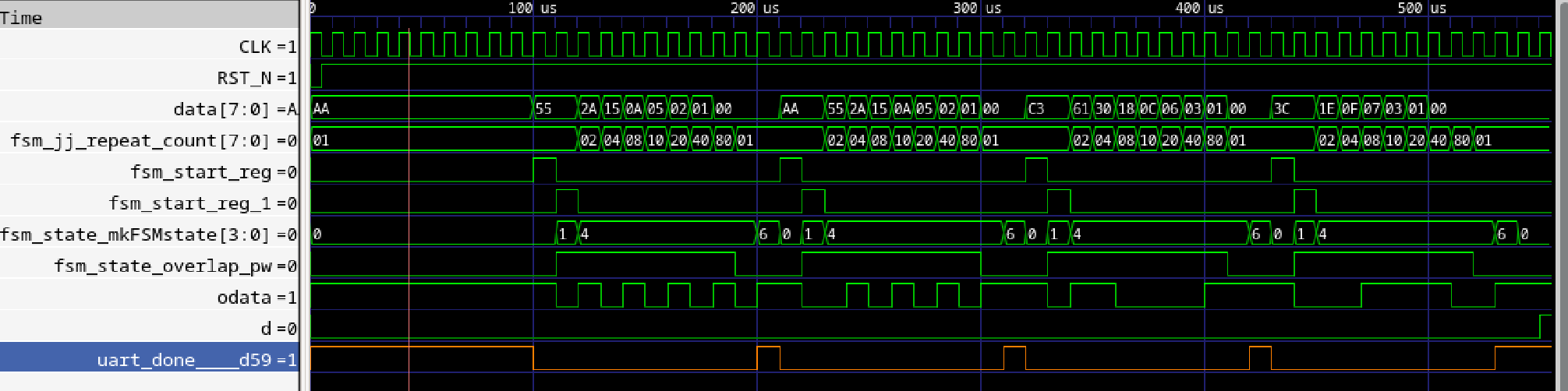

Verilogシミュレーション

Verilogシミュレーションにおいては、モジュール(mkUart.v)、それをドライブするテストベンチ(mkTb.v)の上位に最上位(top.v)を配備します。これはクロックやリセットを供給するモジュールですが、Bsimの場合はシステムから暗黙にクロックやリセットが供給される一方、Verilogでは供給されないためです。

top.v

`timescale 1ns/1ns

module top();

/*AUTOREGINPUT*/

// Beginning of automatic reg inputs (for undeclared instantiated-module inputs)

reg CLK; // To mkTb_inst of mkTb.v

reg RST_N; // To mkTb_inst of mkTb.v

// End of automatics

/*AUTOWIRE*/

mkTb mkTb_inst(/*AUTOINST*/

// Inputs

.CLK (CLK),

.RST_N (RST_N));

initial begin

RST_N = 1'b0;

#10;

RST_N = 1'b1;

end

initial begin

CLK = 1'b0;

forever begin

#5 CLK = ~CLK;

end

end

initial begin

$dumpfile("verilog.vcd");

$dumpvars;

end

endmodule // top

Verilogシミュレーションのコマンドは次のとおりです。

$ bsc -u -verilog Tb.bsv; iverilog top.v mkTb.v mkUart.v -o ./mkTb.exev; ./mkTb.exev; gtkwave -A verilog.gtkw

Verilogシミュレーションのほうには当然ですが、uart.done信号が存在します。