|

28 |

Pipeline processorの設計 (18) |

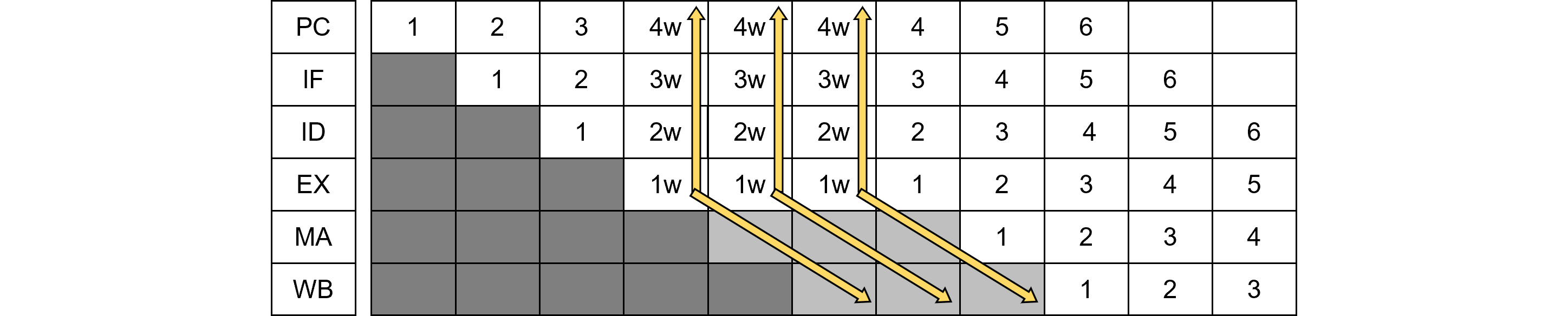

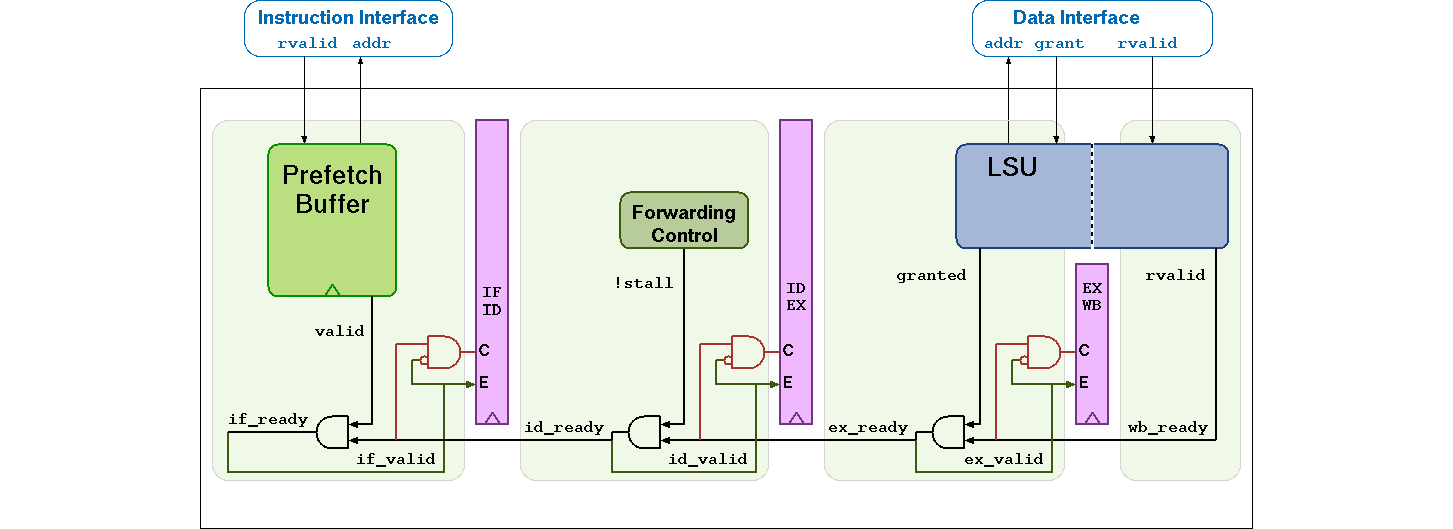

パイプライン制御の無効化論理

一方、後段にバブルを流すinvalidate信号は、EXWBレジスタのC(lear)信号ですが、やや冗長になっています。EXWB.C信号に(467.1)を代入し、ドモルガンの定理を用いて整理すれば、 $$ \require{cancel} \begin{eqnarray} \text{EXWB.C}&=&\text{wb_ready }\cap\text{!ex_valid}\\ &=&\text{wb_ready }\cap\text{(!granted }\cup\text{!wb_ready)}\\ &=&\text{(wb_ready }\cap\text{!granted) }\cup\bcancel{\text{(wb_ready }\cap\text{!wb_ready)}}\\ &=&\text{wb_ready }\cap\text{!granted} \end{eqnarray} \tag{468.1} $$ 使用ゲートは同じで、配線を繋ぎ変えるだけで1段論理になるので、2段通すのは若干無駄な論理のように見えます。論理合成を用いれば上記のように最適化されるでしょうけど。

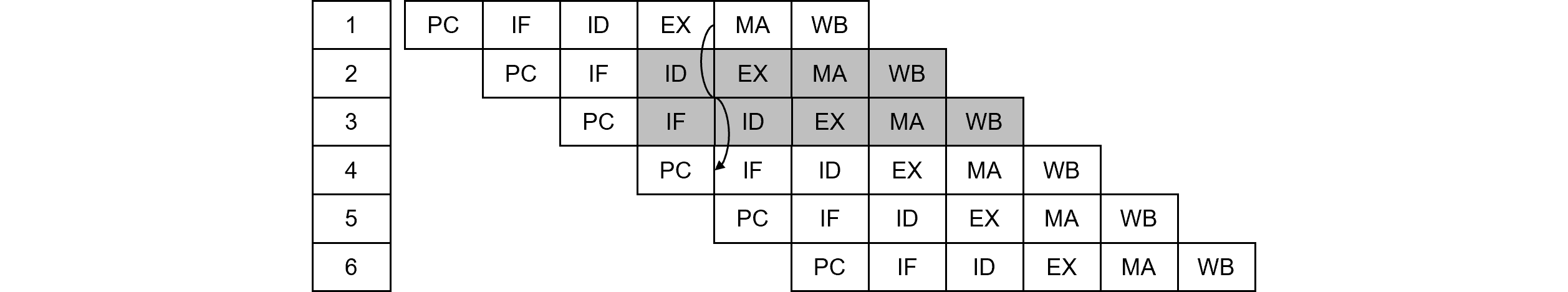

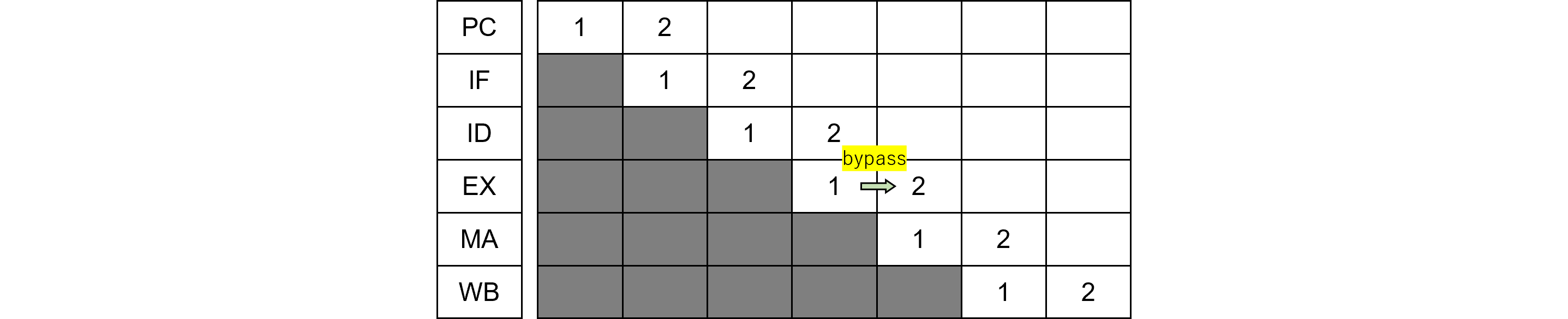

図468.2に修正後の回路を示します。

前稿等で検討したように、パイプラインバブルは後段へ流すものですから、当該ステージ、この場合は<EX>にウエイト要因があり($=\text{!granted}$)、かつ後段である<WB>からウエイトが来ていない($=\text{wb_ready}$)ときに限り、後段を無効化する論理となり、(468.1)は正しいです。そして、この無効化信号は、パイプラインストリームのキャンセルにも用いられます。

パイプライン制御の有効論理

EXWB.Cの反転論理である<EX>有効信号を新たに$ex\_valid$とすれば、 $$ \require{cancel} \begin{eqnarray} ex\_valid&=&\text{!wb_ready }\cup\text{granted }\\ &=&wb\_wait\text{ }\cup\text{ }!exs\_wait \end{eqnarray} \tag{468.2} $$ となります。