|

30 |

グラフィックディスプレイコントローラの設計 (4) |

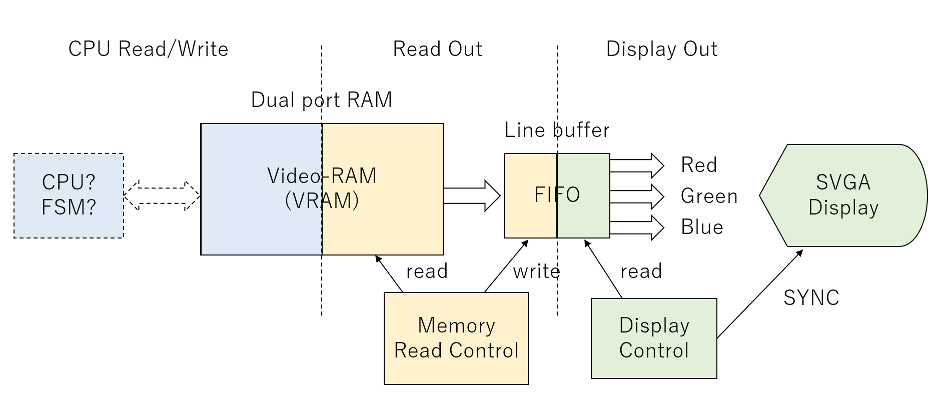

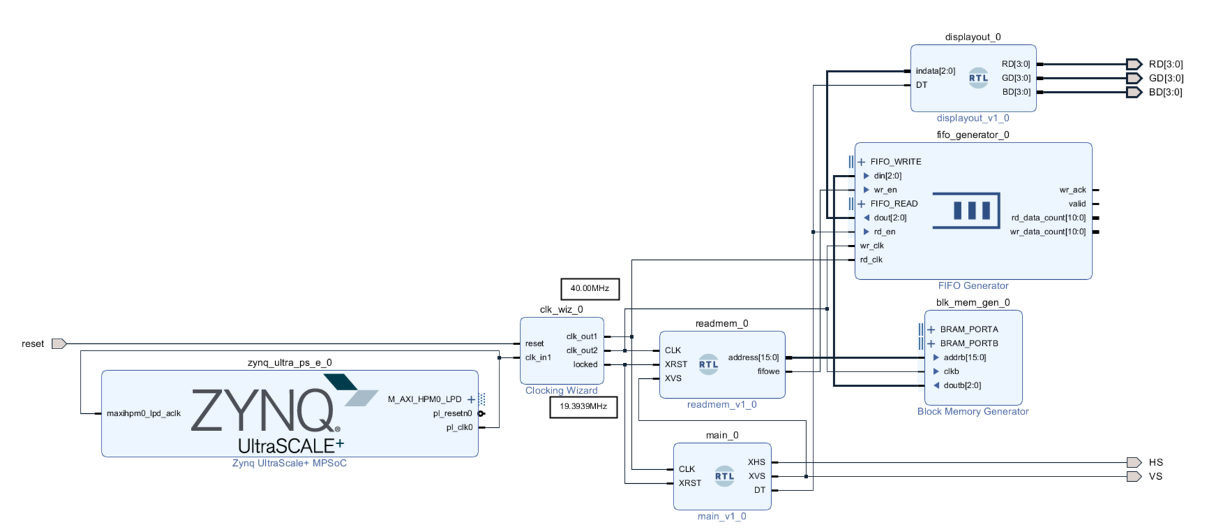

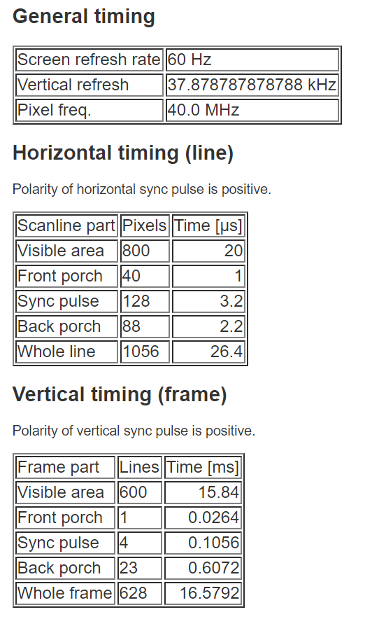

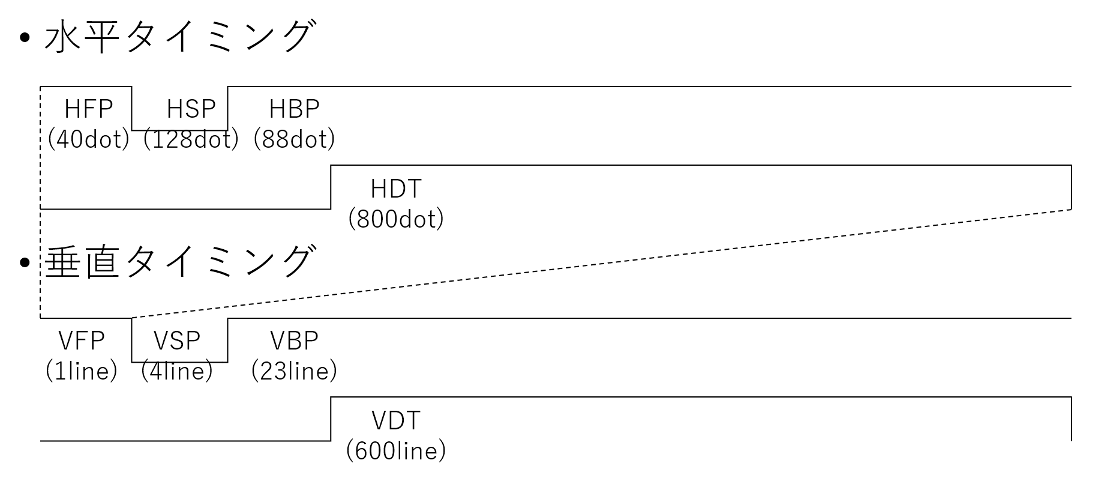

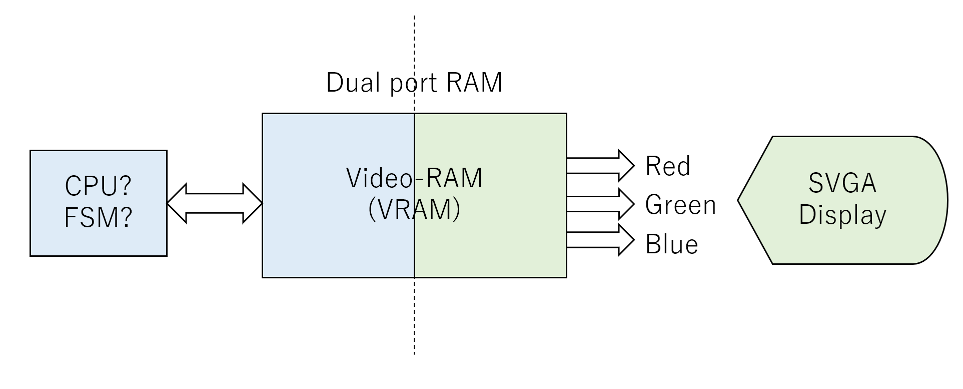

前回までで、VRAMの内容を定常的に表示するグラフィックディスプレイコントローラの設計が完了しました。割愛していますが、シミュレーションを駆使し、動作の確認を行っています。

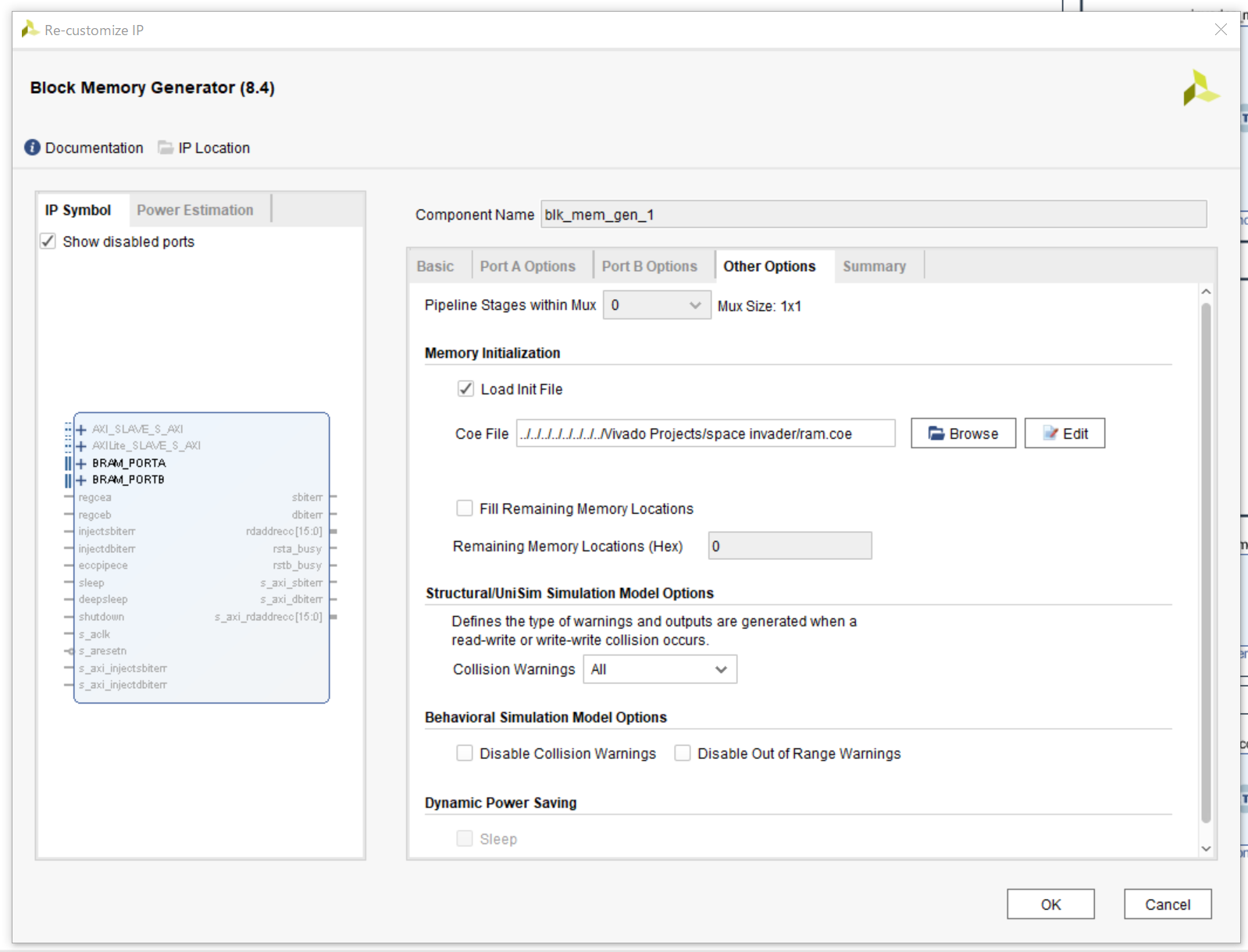

このままでは描画マスタを設計していないため、静止画を表示することしかできませんが、Bitstream中に初期VRAMデータを埋め込むことが可能です。ブロック図でデュアルポートメモリをダブルクリックすると、以下の画面が現れ、"Other Options"の"Memory Initialization"にファイル名を入力します。

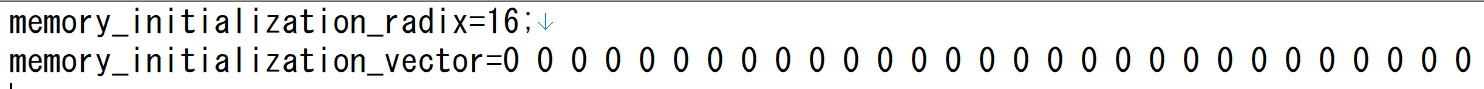

ここでは、dual port memoryの初期データファイルとして、スペースインベーダーの画像を取り込むことにします。データは以下のようなフォーマットで構成します。Vivadoにはデータがフォーマットに沿っているかの確認を行うコマンドがあり、validateを実行し、正しいデータかどうか確認した後にwrite bitstreamを行います。

以下にGDCを起動したところの図を示します。残念ながら、描画マスタを設計しておらず、表示マスタのみが動作しているため、画像は静止しています。