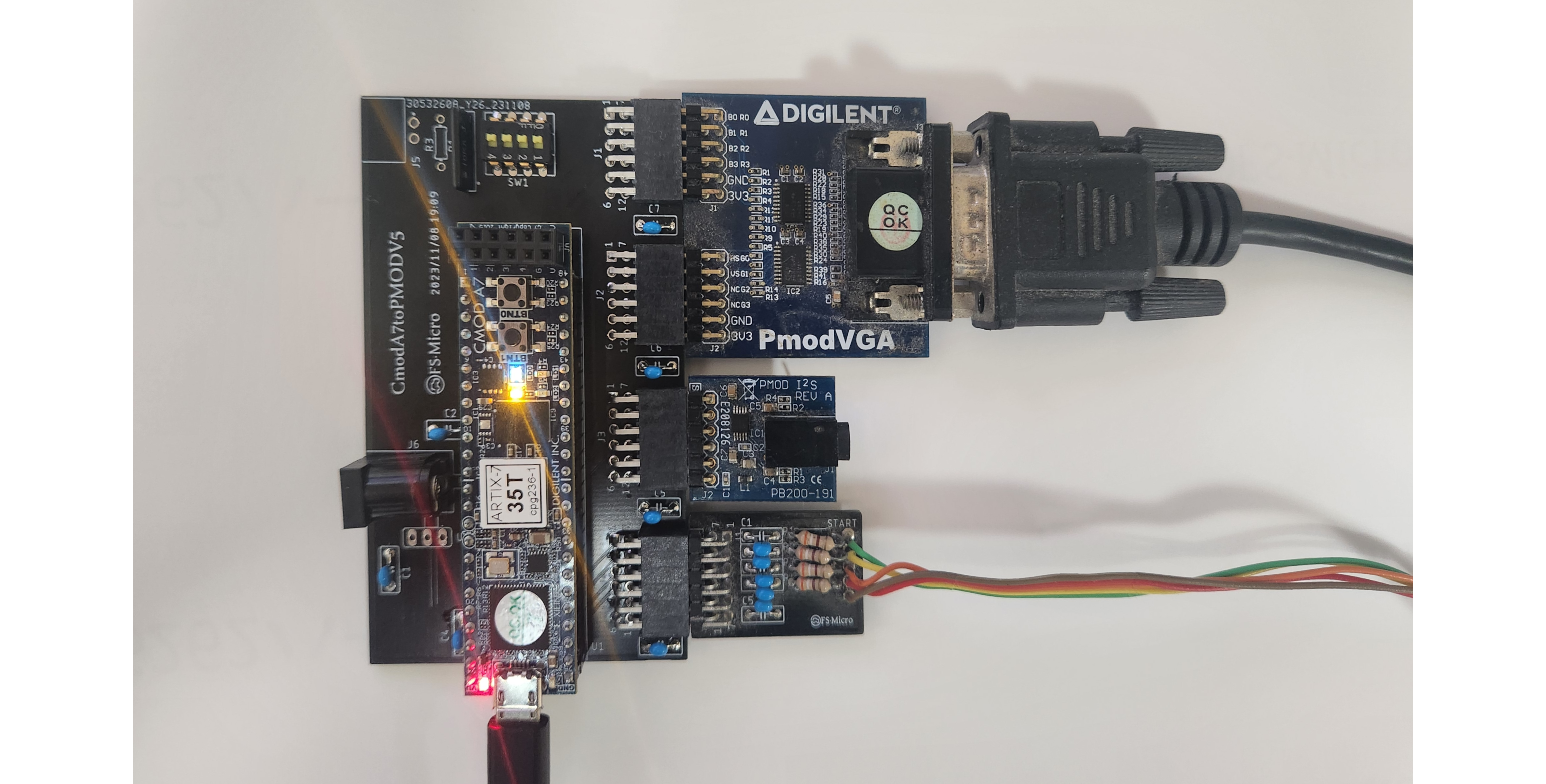

実験によるフィードバック

VRを実際にADCに接続してJTAG経由で測定したところ、VRと付属回路の電圧値は0.158~0.711Vとなりました。LTSpiceの値と異なったのは手持ちの適当な抵抗を付けたからかもしれません。

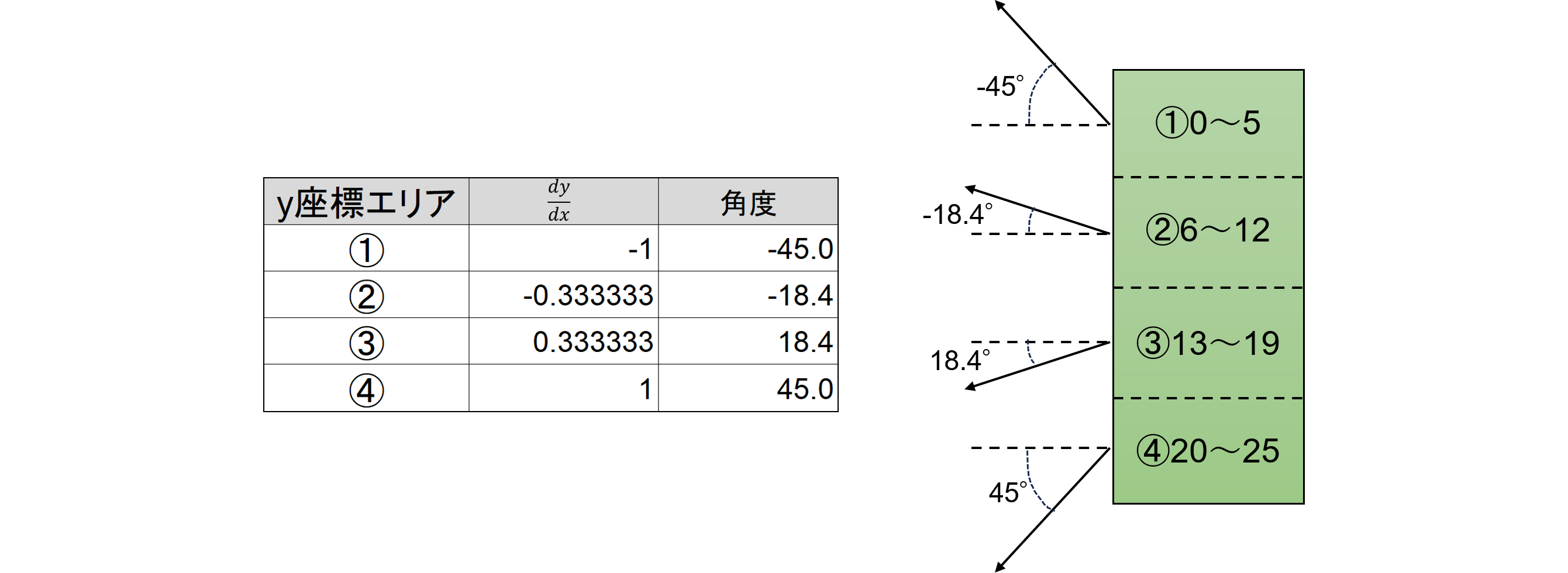

また、パラメータ化したa, bはデフォルト値のa=105, b=90で特に違和感はありませんでした。特に可変範囲は90°としました。これは全回転角が300°でリニアの場合ですが実際にはそうではなく、使用角度bは45°くらいとなりました。

ADCの出力をちょうどy座標の動作範囲にクリップしていましたが、実験の結果、パドルが端にくっつかない問題がありました。そのためADCの出力を、動作範囲よりも5%ほど大きめにして座標計算でもクリップすることにします。

さらにパドル消去アルゴリズムを変更したため、パドルの大きさも多少変えました。従って、再度設計計算を行います。一度方式としては確定しているため、数値を少々変更するだけです。変化点をマーカで表示します。ピンクは前記事との変化点であり、ブルーは最終結果としてソースコードに入れる値です。

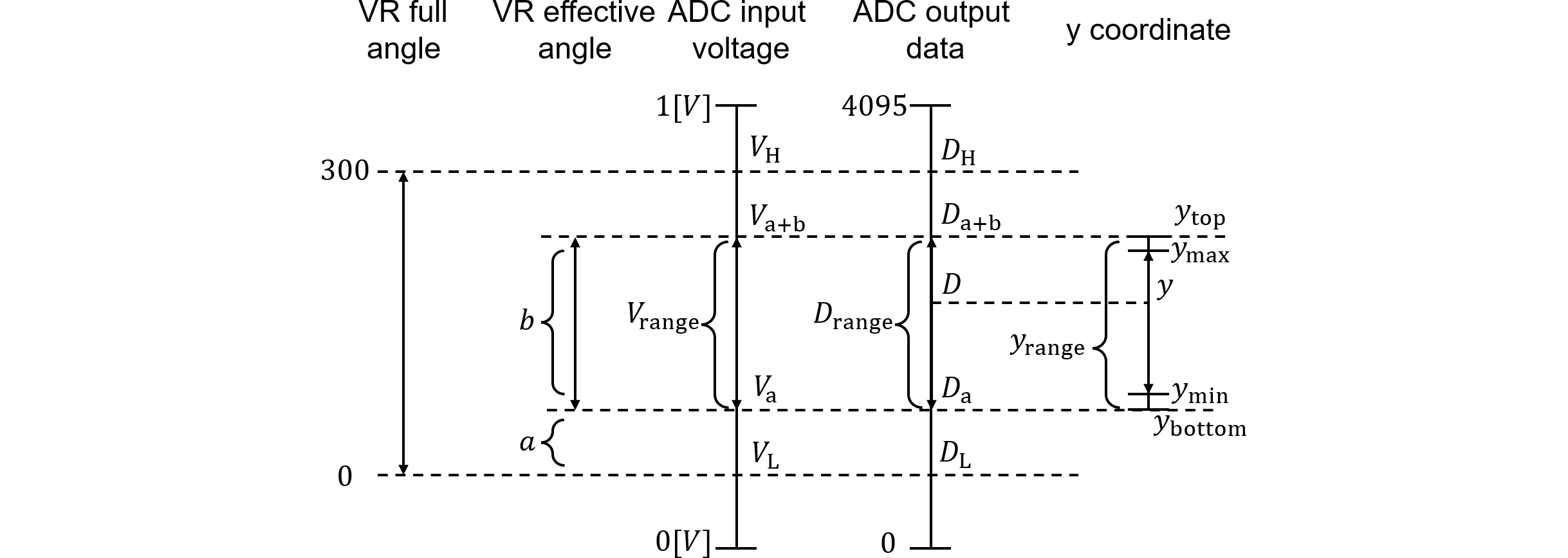

- VRの全角度は300°

- VRの有効角はパラメータ化し、開始角a[°] (デフォルト値a=105)、範囲b[°] (デフォルト値b=90)

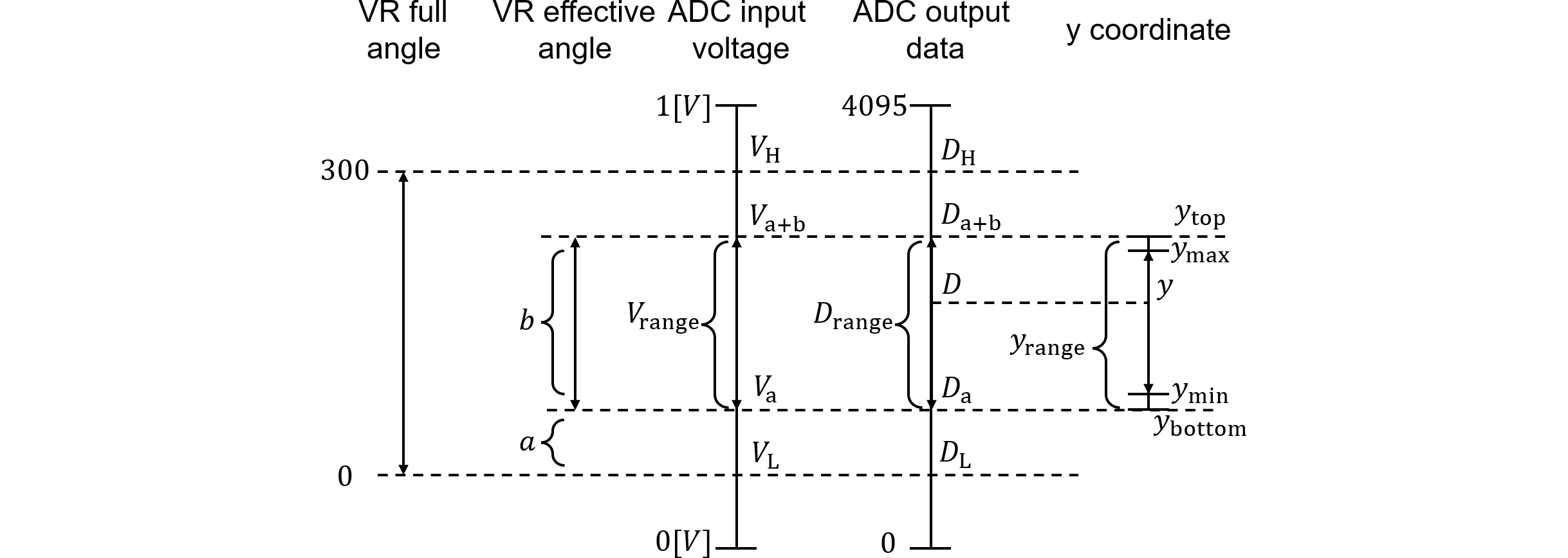

- VRの全角度の際のADC入力電圧は測定結果より、0.16~0.71[V]

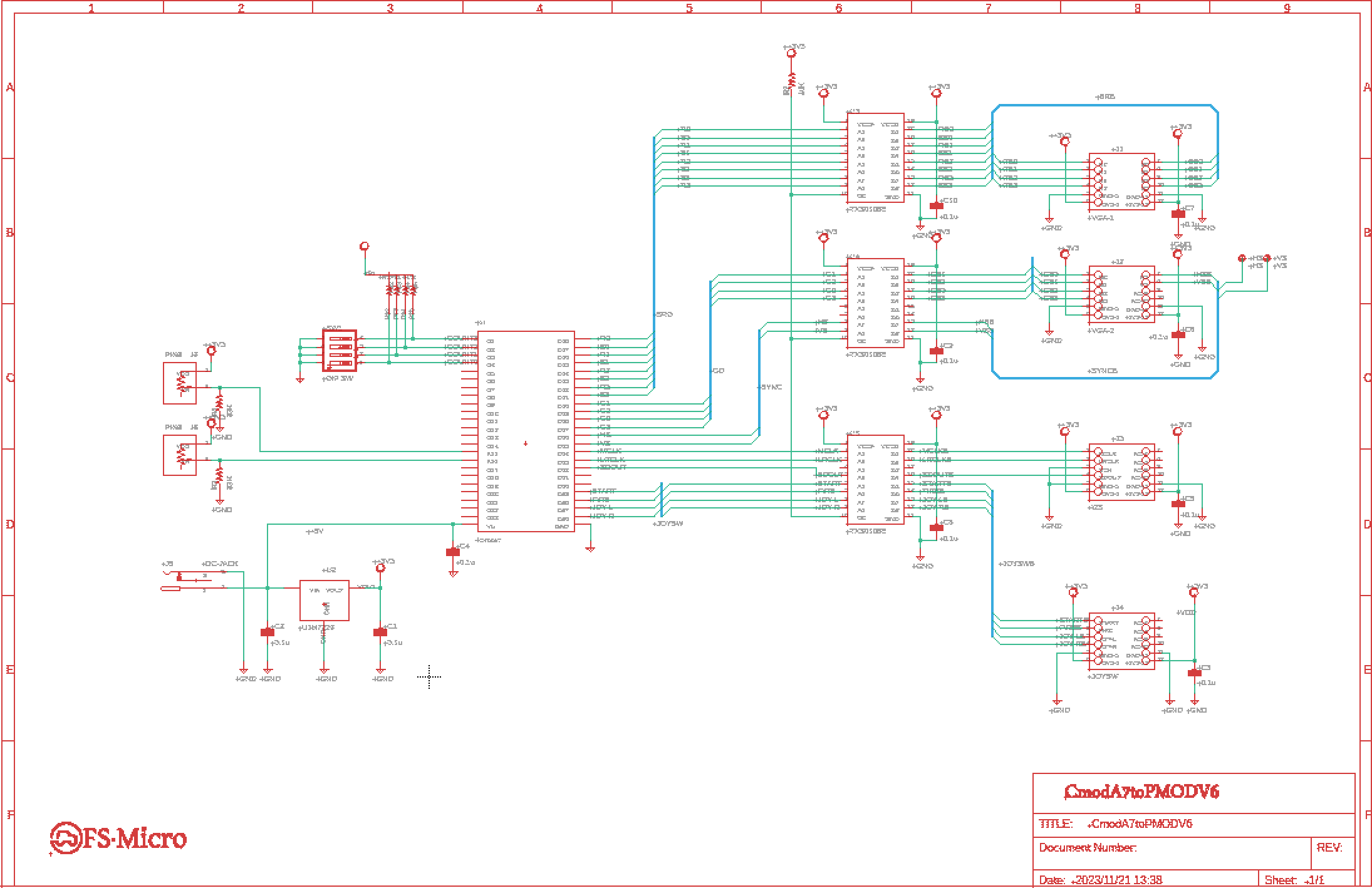

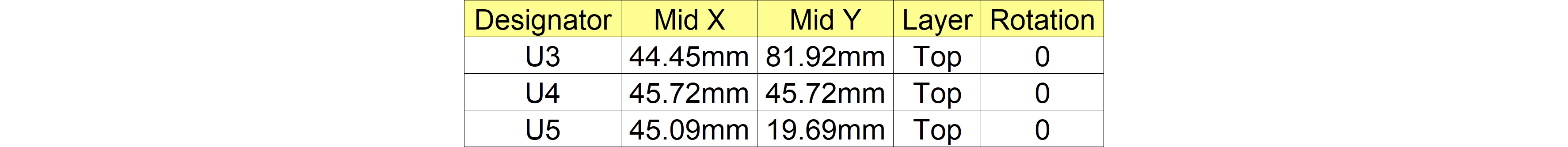

図710.1 レベルダイア

図710.1 レベルダイア

再設計計算

これらより、ADC入力電圧は開始角$a$の値を$V_\text{a}$、終了角$a+b$の値を$V_\text{a+b}$として、

$\require{color}

\definecolor{pink}{rgb}{1.0,0.8,1.0}

\definecolor{blue}{rgb}{0.8,0.8,1.0}$

- $V_\text{L}=\colorbox{pink}{0.16}$, $V_\text{H}=\colorbox{pink}{0.71}$

- $V_\text{range}=V_\text{H}-V_\text{L}=\colorbox{pink}{0.55}$

- $V_\text{a}=\frac{V_\text{range}}{300}a+V_\text{L}$

- $V_\text{a+b}=\frac{V_\text{range}}{300}(a+b)+V_\text{L}$

次にAD変換後のデータDは入力全範囲0~1[V]を4096分割する。開始角の値を$D_\text{a}$、終了角の値を$D_\text{a+b}$として

- $D_\text{a}=4096V_\text{a}=\frac{4096V_\text{range}}{300}a+4096V_\text{L}=\colorbox{pink}{7.509}a+\colorbox{pink}{655.4}$

- $D_\text{a+b}=4096V_\text{a+b}=\colorbox{pink}{7.509}(a+b)+\colorbox{pink}{655.4}$

- $D_\text{range}=D_\text{a+b}-D_\text{a}=\colorbox{pink}{7.509}b$

一方、y座標の制約は以下のとおりであり、$y_\text{top}$(上限$y_\text{max}$+5%)と$y_\text{bottom}$(下限$y_\text{min}$-5%)の値でクリッピング。

- $y_\text{min}=\colorbox{pink}{44}, y_\text{max}=\colorbox{pink}{219}, Paddle_\text{h}=\colorbox{pink}{26}$

- $y_\text{bottom}=y_\text{min}-7=\colorbox{pink}{37}, y_\text{top}=(y_\text{max}-Paddle_\text{h})+7=\colorbox{pink}{200}$

- $y_\text{range}=y_\text{top}-y_\text{bottom}=200-37=\colorbox{pink}{163}$

これらからy座標を求めると、ADCのデータを$D$とすれば、

- $y=\frac{y_\text{range}}{D_\text{range}}(D-D_\text{a})+y_\text{bottom}=\frac{\colorbox{pink}{163}}{\colorbox{pink}{7.509}b}D-\frac{\colorbox{pink}{163}}{b}a-\frac{\colorbox{pink}{163}\cdot\colorbox{pink}{655.4}}{\colorbox{pink}{7.509}b}+\colorbox{pink}{37}\\

=\frac{\colorbox{pink}{347.3}}{b\ll4}D-\frac{\colorbox{pink}{163}}{b}a-\frac{\colorbox{pink}{14225}}{b}+\colorbox{pink}{37}=\frac{\colorbox{blue}{347}D-\colorbox{blue}{2608}a-\colorbox{blue}{227607}}{b\ll4}+\colorbox{blue}{37}$

y式中のシフトは固定小数点演算を行うために分母分子を16倍しているものです。さらに最小値$D_\text{a}$、最大値$D_\text{a+b}$で入力ADCデータのクリッピングを行います。

- $D_\text{a}=\colorbox{pink}{7.509}a+\colorbox{pink}{655.4}=(\colorbox{blue}{120}a+\colorbox{blue}{10486})\gg4$

- $D_\text{a+b}=\colorbox{pink}{7.509}(a+b)+\colorbox{pink}{655.4}=(\colorbox{blue}{120}(a+b)+\colorbox{blue}{10486})\gg4$

以上より、完成したBSVコードの変更点のみを以下に示します。

クリッピング値計算部分

// 座標の下限-5%と上限+5%に対応するADC値の計算

Bit#(20) adcMinValue = (120 * extendedA + 10486) >>4; // Min = 7.509A + 655.4

Bit#(20) adcMaxValue = (120 * (extendedA + extendedB) + 10486) >> 4; // Max = 7.509(A+B) + 655.4

ADCからy値計算部分

Bit#(24) coordinate = ((zeroExtend(clippedAdcValue) * 347

- zeroExtend(extendedA) * 2608 - 227607)

/ zeroExtend(extendedB) >> 4) + 37;

変換器部分はこのとおりですが、FSM中でのパドルの可動範囲$y_\text{min}=\colorbox{blue}{44}$、$y_\text{max}-Paddle_\text{h}=219-26=\colorbox{blue}{193}$でクリッピングすることを忘れないように注意します。

前のブログ

次のブログ

前のブログ

次のブログ