|

27 |

Parameterについて (4) |

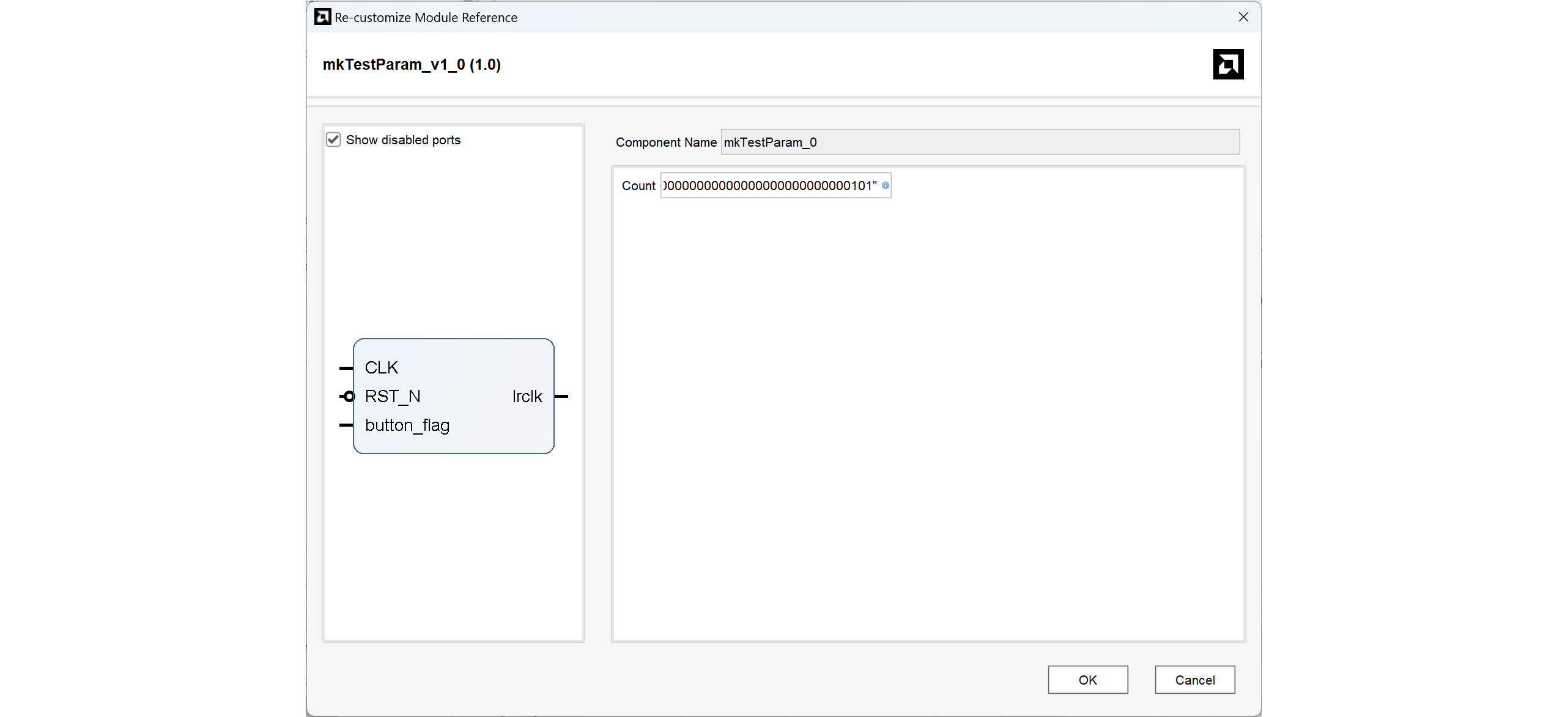

IPインテグレータによる変更

まずパラメータを5とします。入力は10進数、16進数、2進数を受け付けますが、表示は2進数となります。最初は5回を設定したので、"0000....0101"と表示されます。ただしこれはverilog記述に依存するようで、verilogが10進であれば10進となります。

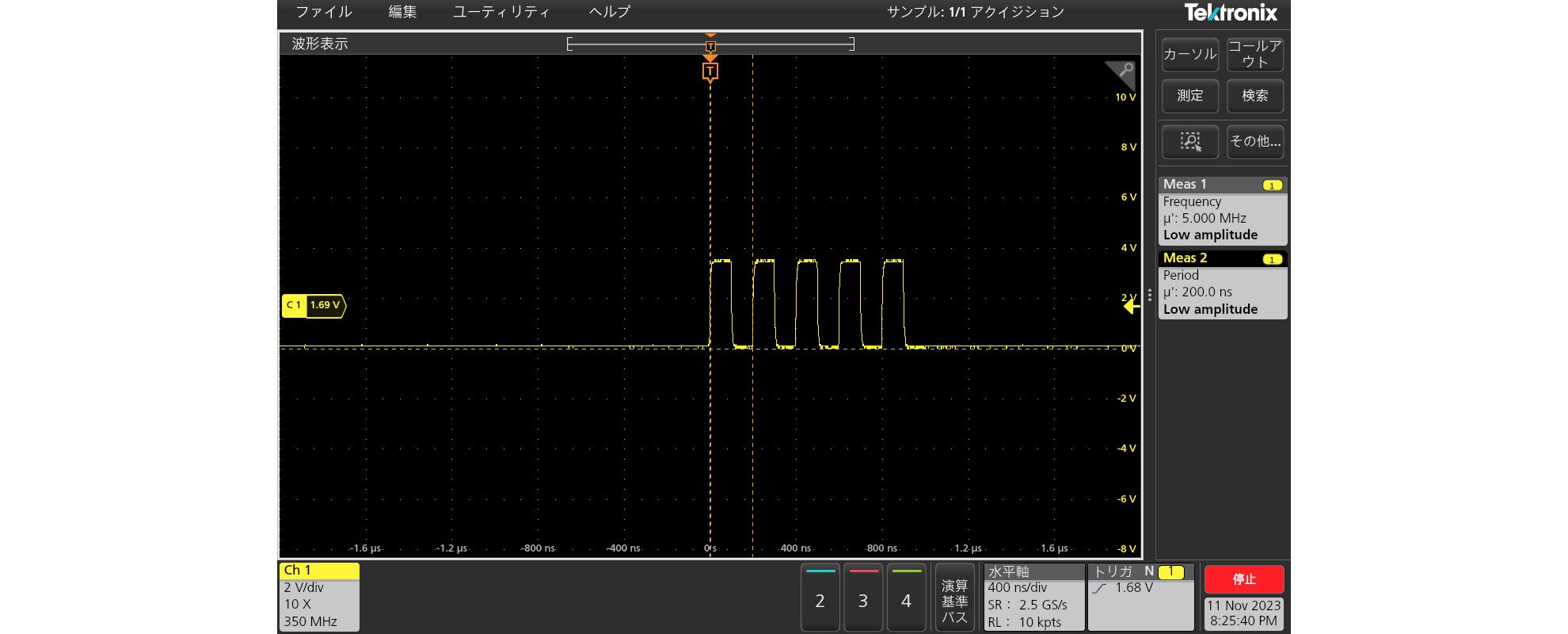

合成してビットストリームをFPGAにダウンロードしてボタンを押せば、以下の波形が得られます。パルスが5回出力されています。

次にパラメータを7とすれば、"0000....111"と表示されます。

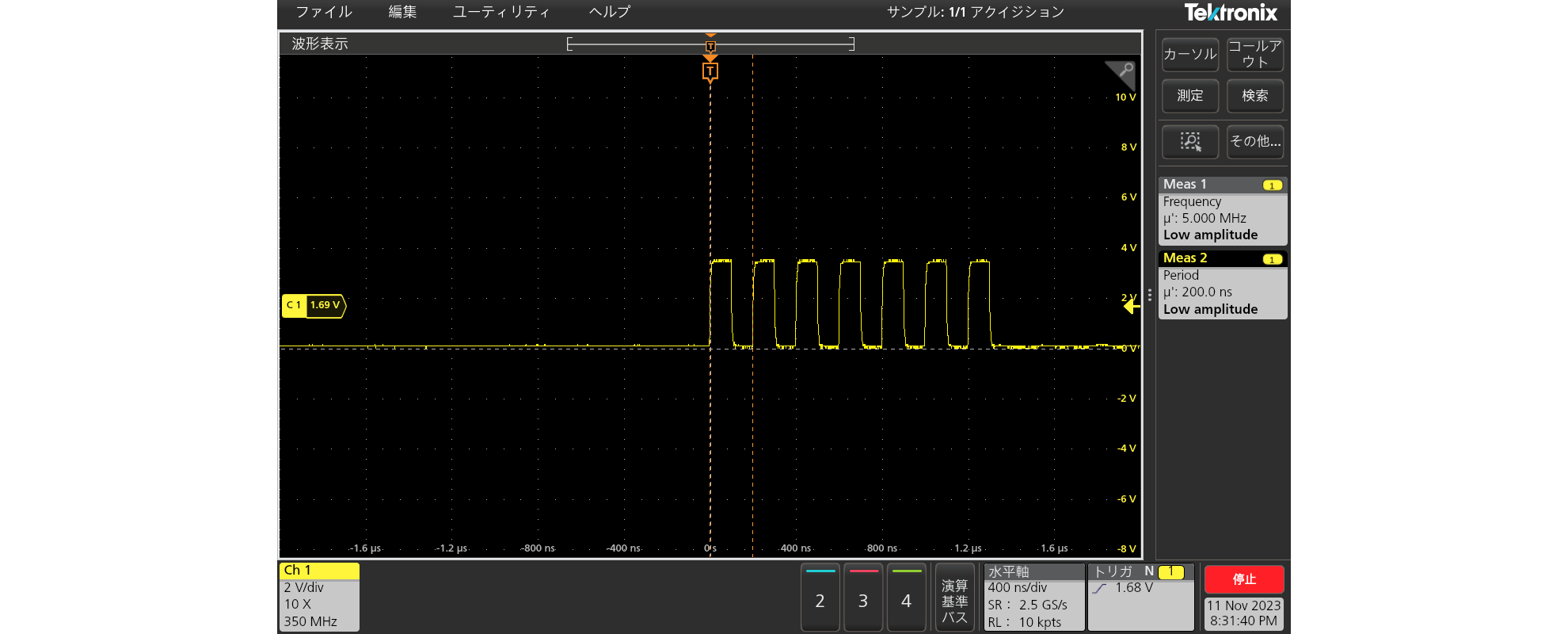

合成してビットストリームをFPGAにダウンロードしてボタンを押せば、以下の波形が得られます。パルスが7回出力されています。

Leave a Comment