|

18 |

色変換回路 (2) |

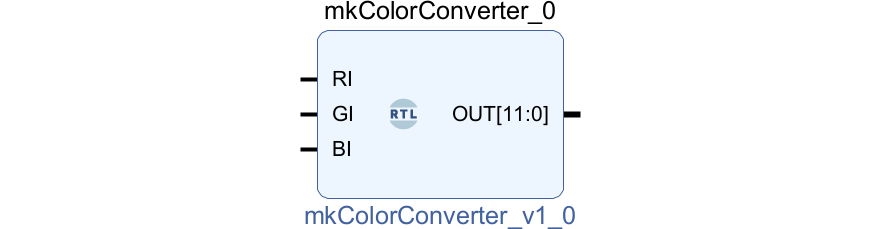

このソースから生成されたverilogファイルは以下のようになります。先頭のコメントやifdef文等を省略したソースを示します。

module mkColorConverter(RI,

GI,

BI,

OUT);

// value method mapColor

input RI;

input GI;

input BI;

output [11 : 0] OUT;

// signals for module outputs

reg [11 : 0] OUT;

// remaining internal signals

wire [2 : 0] x__h134;

// value method mapColor

always@(x__h134)

begin

case (x__h134)

3'b0: OUT = 12'd2369;

3'b001: OUT = 12'd3460;

3'b010: OUT = 12'd1461;

default: OUT = 12'd3276;

endcase

end

// remaining internal signals

assign x__h134 = { RI, GI, BI } ;

endmodule // mkColorConverter

問題は以下のようにstructで3つのデータを構造化しているにも関わらず、12ビット出力ポートが1個生成されてしまうことです。構造体メンバを取り出す方法がありません。

typedef struct {

Bit#(4) ro;

Bit#(4) go;

Bit#(4) bo;

} ColorOutputs deriving (Bits);

これを4bitの3つの出力ポートとしたいわけです。

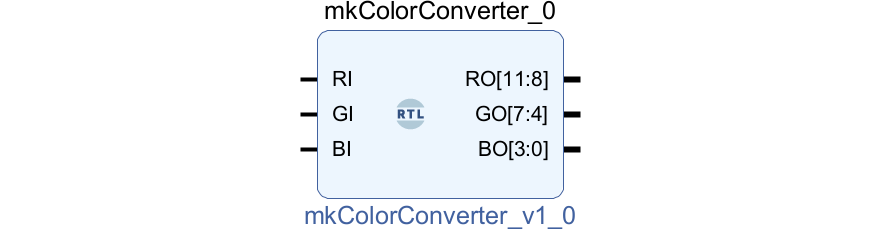

不思議なことにBSVの世界から離れてverilogだけでなんとかしようとして手修正によりポートを3つに分けてみたのですが、思ったようにはなりませんでした。例えばverilogを

module mkColorConverter(RI,

GI,

BI,

RO,

GO,

BO);

// value method mapColor

input RI;

input GI;

input BI;

output [3 : 0] RO;

output [3 : 0] GO;

output [3 : 0] BO;

// signals for module outputs

wire [3 : 0] RO = OUT[11:8];

wire [3 : 0] GO = OUT[7:4];

wire [3 : 0] BO = OUT[3:0];

reg [11: 0] OUT;

のように手修正しても、以下の図のような回路となってしまいました。ポート名は良いのですが、ポート番号が思ったように付いてくれません。

いちいち手修正するのも嫌なので、BSVで可能な方法を探ります。

Leave a Comment