|

30 |

サウンドコントローラの設計 (2) |

※前回の続きです。

設計制約

設計制約をリストアップします。

- LRCLKの1周期に対し、L=16bit, R=16bitの32bitのシリアルデータが必要であり、シリアルデータはSCKでシフトされるので、SCK=LRCLK*32。ただしこのSCKは、DACに供給しなければDAC内部で発生されます。

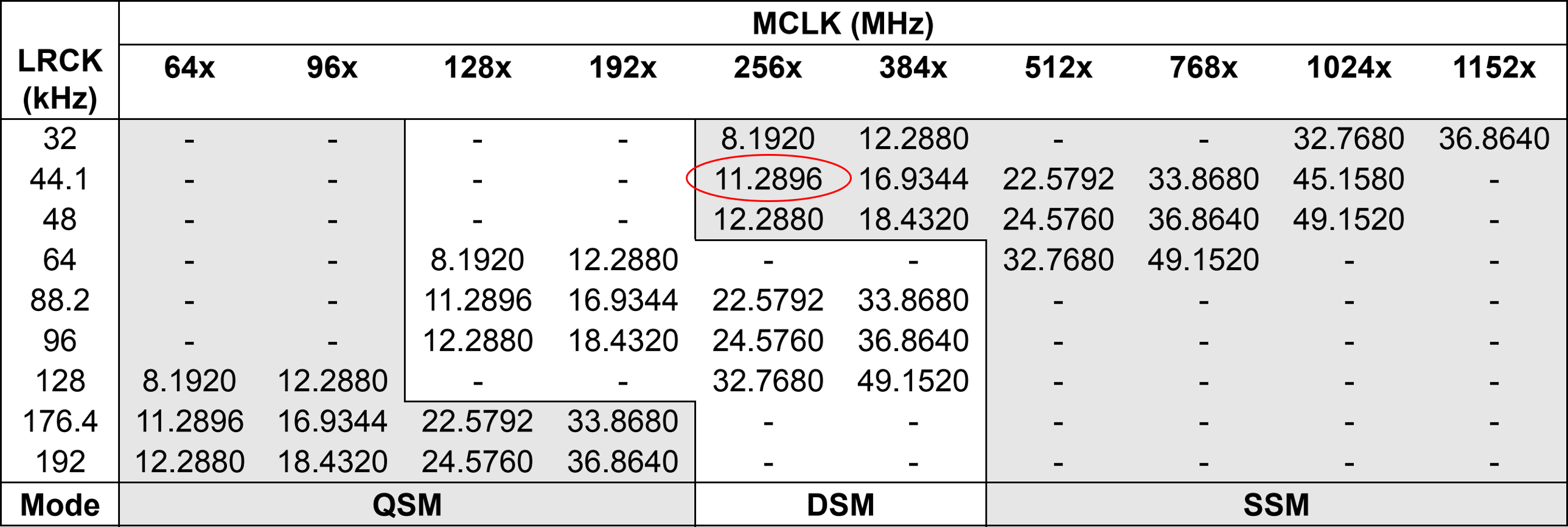

- データフォーマットより、サンプリングレートは16進数で16'h2b11=11025、すなわち11.025KHz。LRCLK=Fs(サンプリング周波数)とのことで、LRCLK=11.025KHzとしたいところですが、下図において、LRCLK=11.025KHzが存在しないので、データのほうを4倍のインターポレーションすることにし、LRCLK=44.1KHzとします。

- 上記関係式よりSCK=1.4112MHz。

- マスタークロック(MCLK)は下図のように、256, 384, 512, 768, 1024倍等の任意性がありますが、ここでは256倍のMCLK=11.2896MHzを使用します。

タイミングチャート

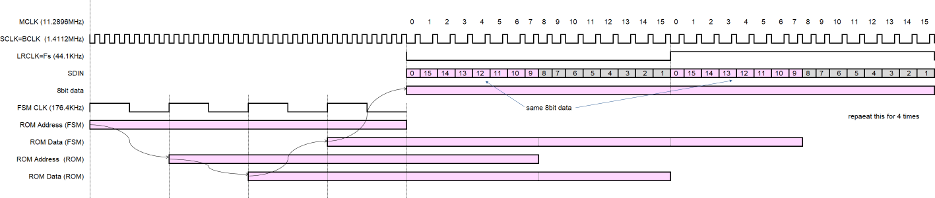

クロックに関する設計制約が解決したので、タイミングチャートを書いていきます。基本的にハードウェアベースのサウンド出力であるため、FSMによるフォーマット解析を行います。タイミングチャートは以下のとおりです。

ステートマシンのクロックFSMCLKは図74.2のように、ステートアドレス、ステートデータ、データアドレス、データデータの4クロックで1サウンドデータの読み出しになることから、$\text{CLK}^{-1}$をCLKの周期と表記すれば、4*$\text{FSMCLK}^{-1}$=2*16*$\text{SCK}^{-1}$、つまり、8*FSMCLK=SCK。これよりFSMCLK=176.4KHz。

DACが要求する16bitデータ×2ch(L, R)の32bitデータについては、データソースが8bitモノラルであるため、8bitデータをMSB側に詰め、残りは0詰めし、16bitとします。LとRには同じデータを供給します。

インタポレーションのやり方はゼロ詰めする方法と、同じデータを繰り返す方法があります。16bit@44.1KHz表現可能なDACに対して8bit@11.025KHzという荒い音質であることから、同じ32bitデータを4回繰り返すことにします。

以上で設計制約から来るクロック周波数とタイミングチャートが確定したので、これに基づいてFSMを設計します。