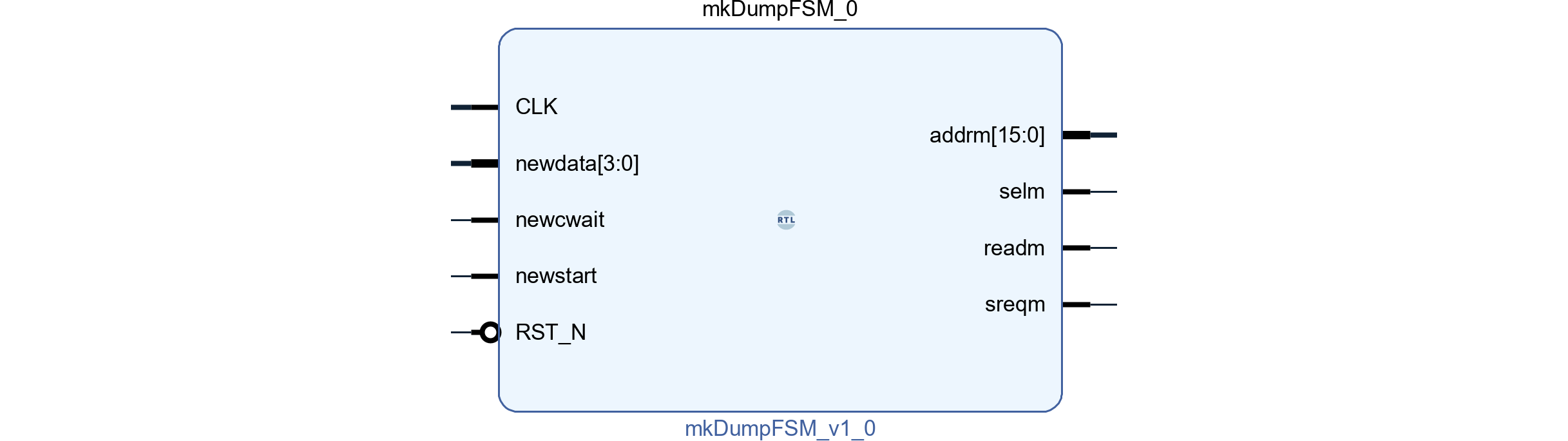

RAMアドレスマルチプレクサの設計

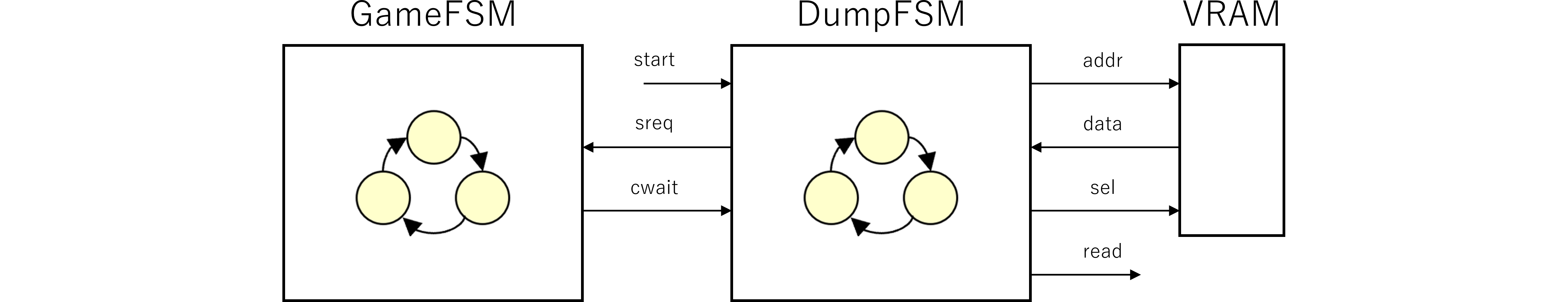

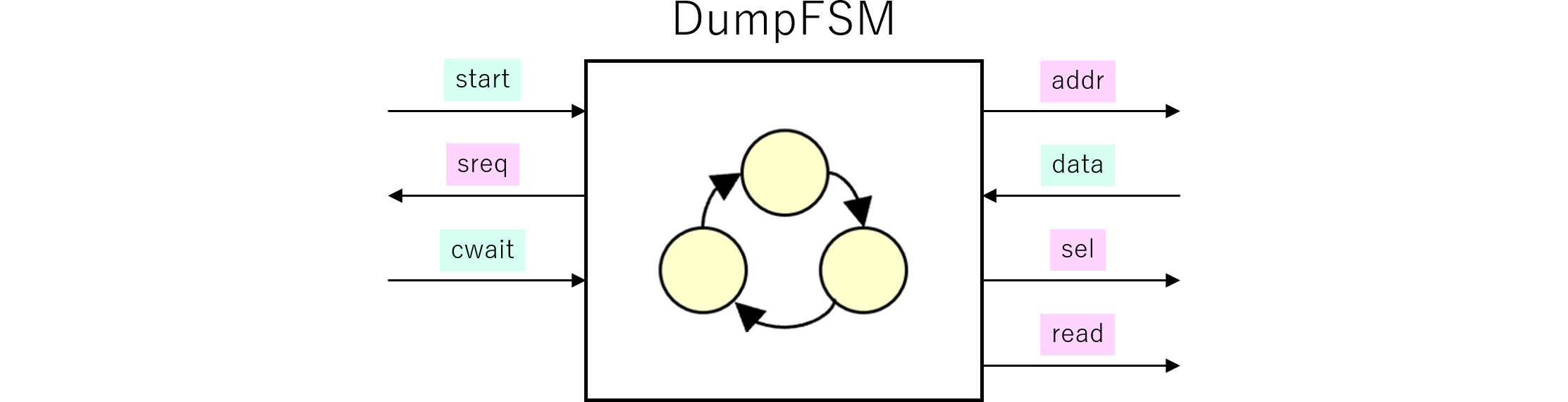

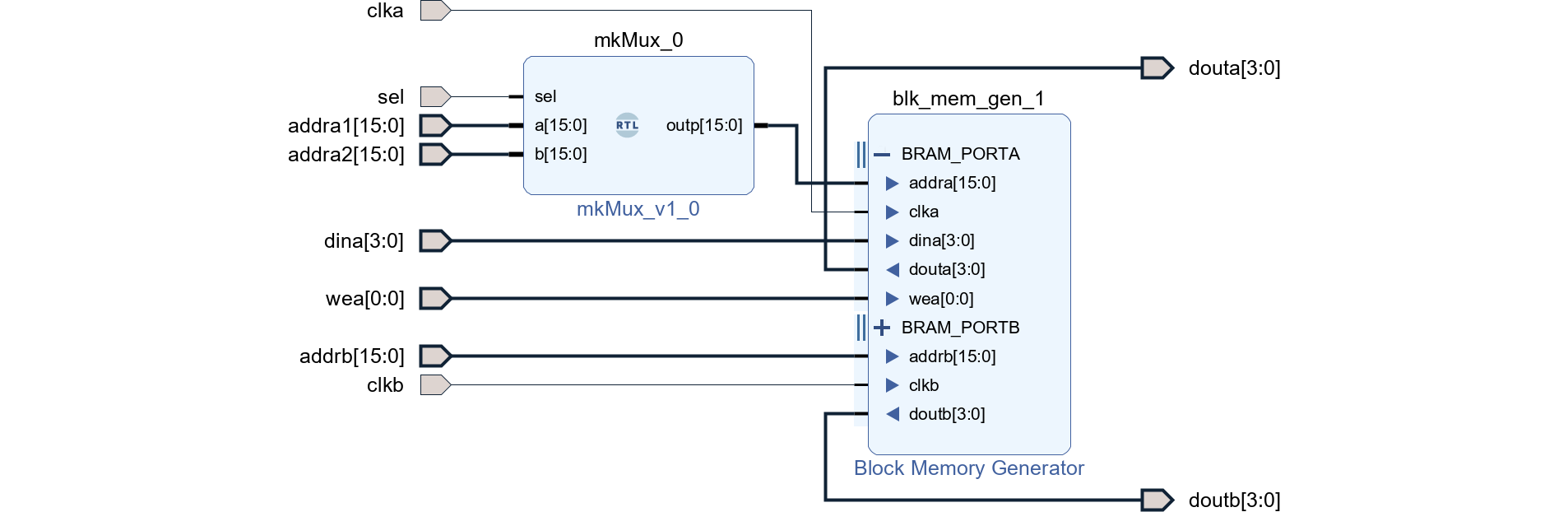

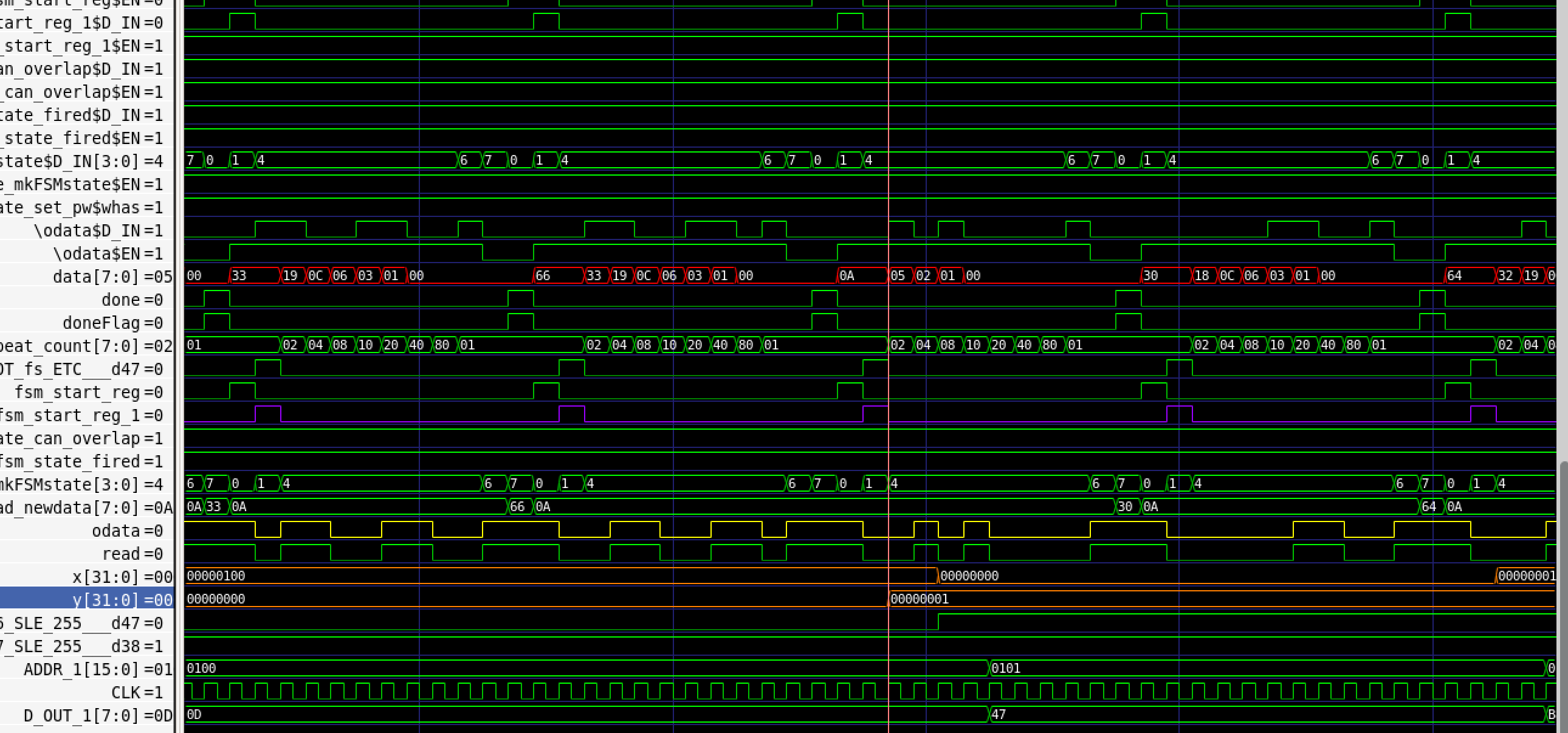

VRAMアクセスするマスタに、FSM、CRTCに加えてメモリダンパが加わりました。しかしながらBRAMのポートが2つまでなので、FSM側のアドレスバスをシェアします。CRTCは常にアクセスしているのに比べて、メモリダンパはFSMが動作していない時のメモリ状態を観測するためだからです。アドレスシェアのためのマルチプレクサを設計します。

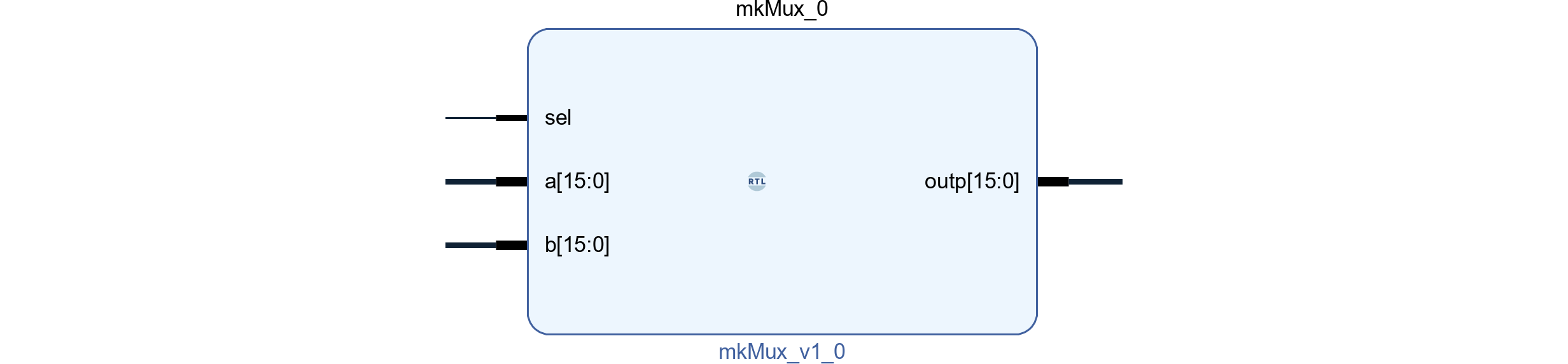

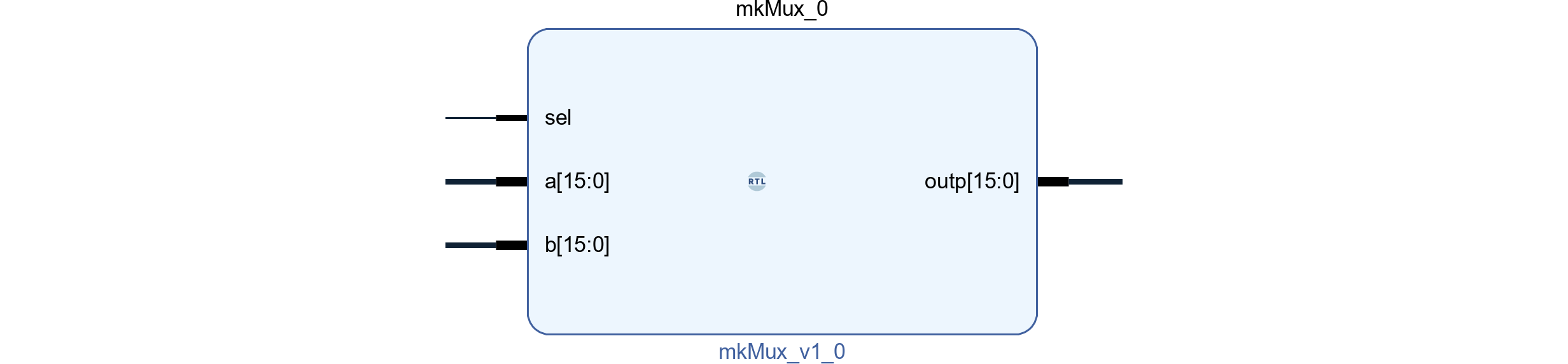

図402.1 マルチプレクサ

図402.1 マルチプレクサ

Mux.bsv

typedef Bit#(16) Addr_t;

interface Mux_ifc;

(* prefix="" *)

method Addr_t outp(Bool sel, Addr_t a, Addr_t b);

endinterface

(* synthesize, always_ready = "outp", no_default_clock, no_default_reset *)

module mkMux(Mux_ifc);

method Addr_t outp(Bool sel, Addr_t a, Addr_t b);

if (sel) return b;

else return a;

endmethod

endmodule

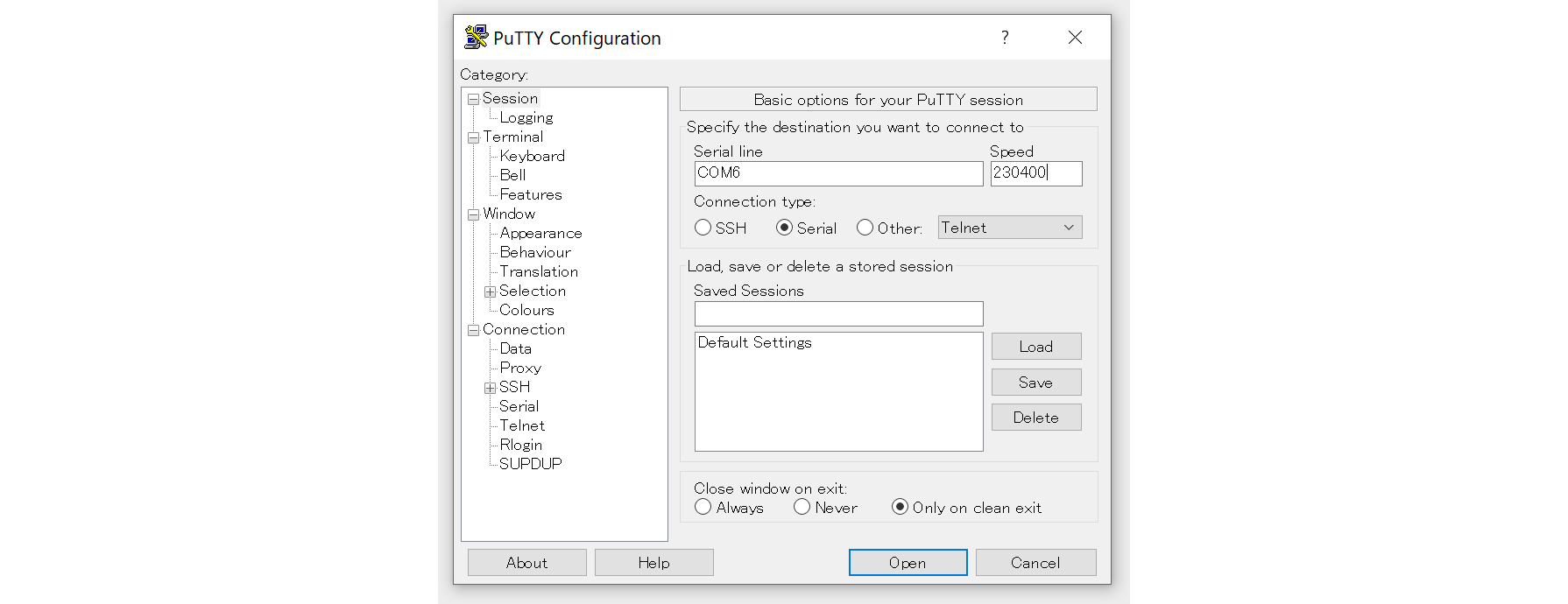

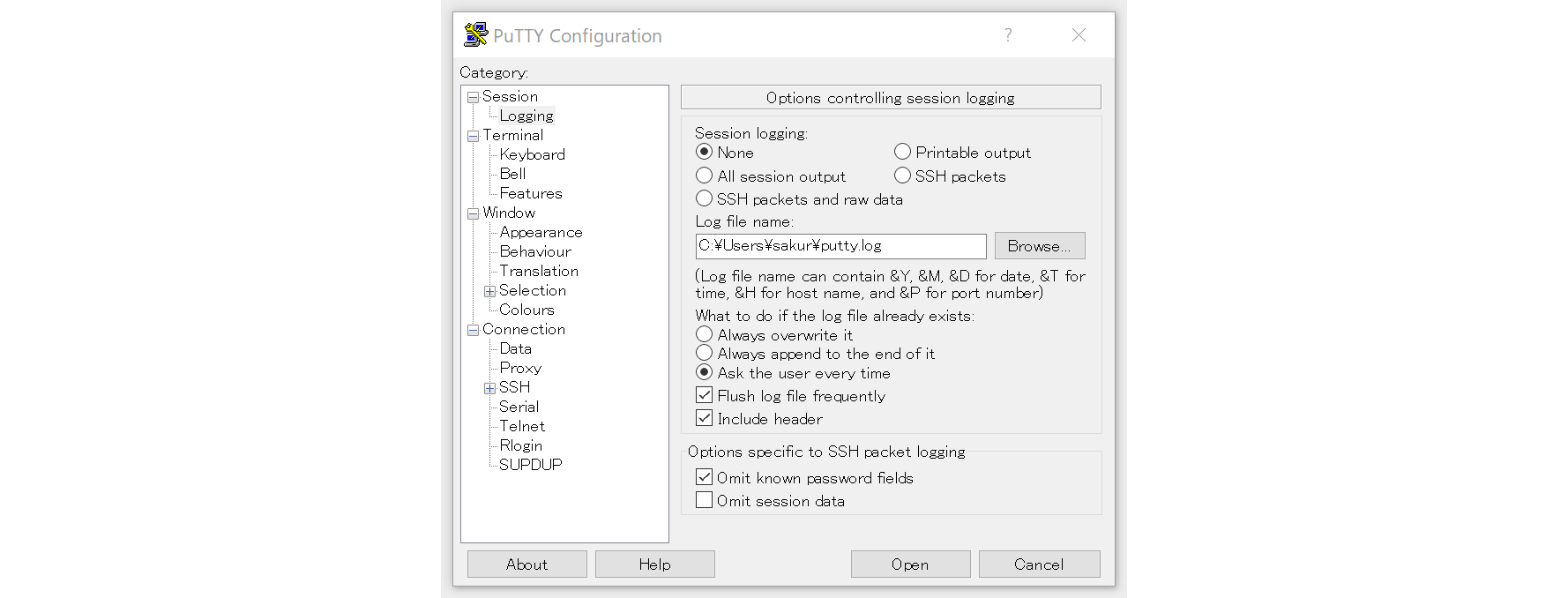

出力のハンドシェーク端子は不要であるため、

(* synthesize, always_ready = "outp" *)

を指定して削除しています。さらに、組み合わせ回路であるため、clock, resetを使用していないので、それらポートを削除するために、

(* no_default_clock, no_default_reset *)

を指定しています。また、入力ピン名が、メソッド名_変数名、例えばoutp_a等のように複雑になるのを防止するため、

(* prefix="" *)

を指定してメソッド名を消しています。

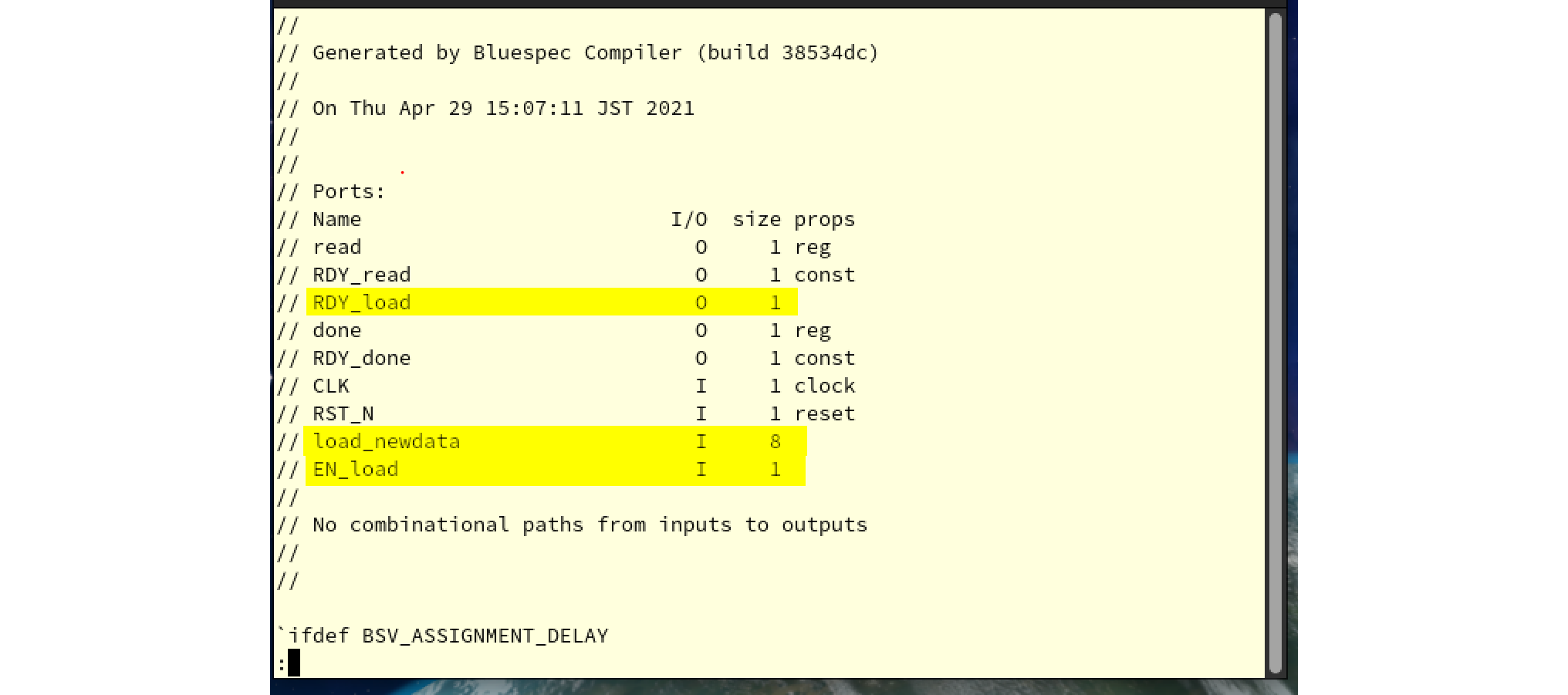

これを合成すると以下のようなVerilogになります。

mkMux.v

//

// Generated by Bluespec Compiler (build 38534dc)

//

// On Thu May 20 14:21:23 JST 2021

//

//

// Ports:

// Name I/O size props

// outp O 16

// sel I 1

// a I 16

// b I 16

//

// Combinational paths from inputs to outputs:

// (sel, a, b) -> outp

//

//

`ifdef BSV_ASSIGNMENT_DELAY

`else

`define BSV_ASSIGNMENT_DELAY

`endif

`ifdef BSV_POSITIVE_RESET

`define BSV_RESET_VALUE 1'b1

`define BSV_RESET_EDGE posedge

`else

`define BSV_RESET_VALUE 1'b0

`define BSV_RESET_EDGE negedge

`endif

module mkMux(sel,

a,

b,

outp);

// value method outp

input sel;

input [15 : 0] a;

input [15 : 0] b;

output [15 : 0] outp;

// signals for module outputs

wire [15 : 0] outp;

// value method outp

assign outp = sel ? b : a ;

endmodule // mkMux

わずか、 assign outp = sel ? b : a ; という一行のverilogを得るためにいろいろと記述していますが、これはBSVの練習のためでもあります。

前のブログ

次のブログ

前のブログ

次のブログ